Efficient On-chip Power Conversion **POWER SOC 2020 Noah Sturcken, PhD Ferric President & CEO**

## NEXT GEN ELECTRONICS REQUIRE NEXT GEN POWER SYSTEMS

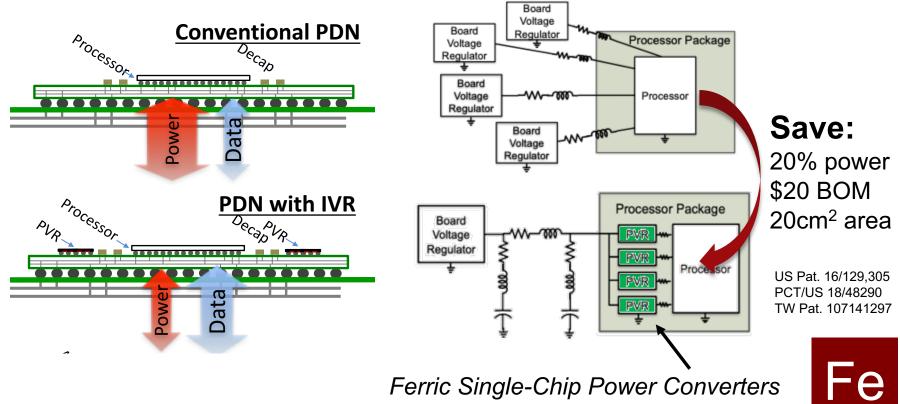

Ferric's manufacturing and system technology enable integrated power management, saving...

- 20-50% Power

- 50-70% Board Space

- 20% Cost

A new foundational technology for modern Systems on Chip

## FERRIC PACKAGE VOLTAGE REGULATORS (PVRS)

- Shrink power converters to be co-packaged with processors

- ■Reduce losses associated with high currents passed through board  $\rightarrow$  socket  $\rightarrow$  package  $\rightarrow$  processor

- Enable delivery of many independently scalable supplies

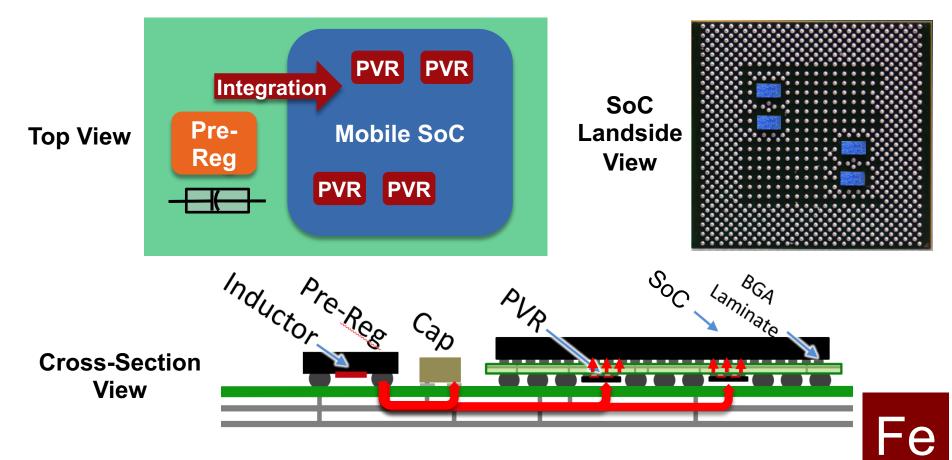

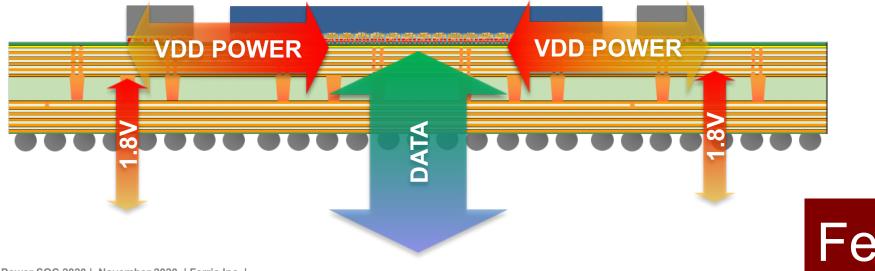

## **PACKAGE VR** for Mobile Applications Processor

- Low-profile (150um) PVR chiplets can be attached to landside of chip-scale packages or be embedded into wafer-level packages

- Consolidate SOC power supplies to a single, loosely regulated 1.8V

## **FERRIC** Single Chip Power Converters

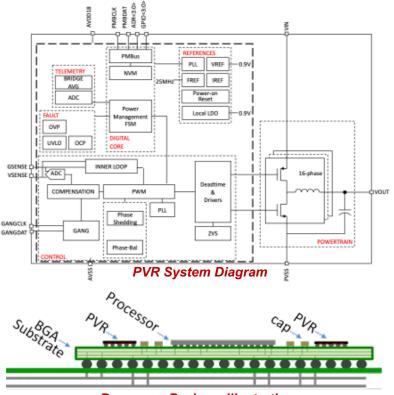

#### **Package Voltage Regulator**

#### Complete many-phase Buck on a single CMOS chip

- Integrating switches, inductors, controller, telemetry and references

- Only missing bulk decoupling capacitance

- V<sub>IN</sub> 1.0V-2.0V :: V<sub>OUT</sub> 0.3V-1.5V with I<sub>OUT</sub> 0-20A

- Conversion efficiency 90% ~ 80%

- Digital Feedback Controller

- 50MHz+ feedback control bandwidth

- 12-bit windowed flash ADC

- Up-to 18-phase DPWM with < 3mV resolution and < 200ps latency</li>

- Fast-Phase-Shedding inner control loop

- 1MHz PMBus-Compliant Serial Interface

- Programmable V<sub>OUT</sub>, F<sub>SW</sub>, Compensation, Telemetry, Faults, etc.

- Dynamic Voltage Scaling (DVS) bus for 200ns voltage transitions

- Gang mode for 1-16 parallel chips

#### Technology

- TSMC N28 HPC+

- Ferric-2 power inductors

- TSMC Cu Pillar terminations on 160µm pitch

- Achieve ~2A/mm<sup>2</sup> chip current density (excluding cap)

- ~1.2A/mm<sup>2</sup> with ceramic decoupling on input and output

- Sold as Standard Product direct to SoC vendors

- Known-Good-Die (KGD) for package integration into FC-BGA/LGA or Si Interposer

Processor Package Illustration

Fe

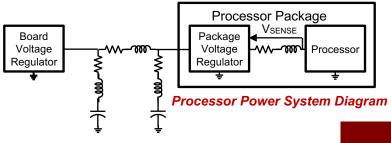

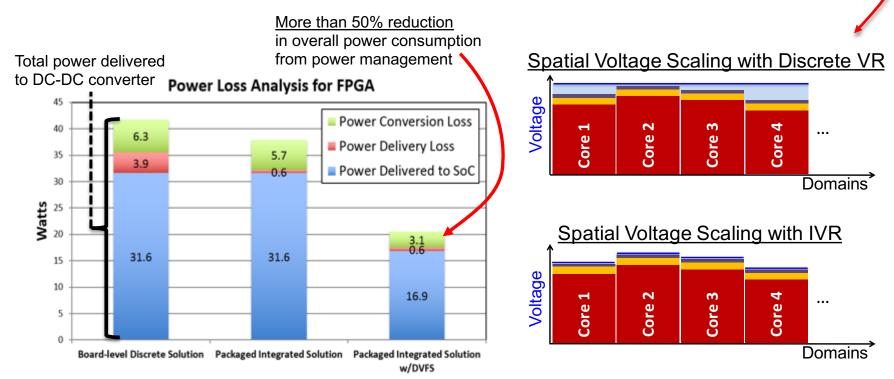

## **PACKAGE VR** Power Savings: 20-50%

- Lower Distribution Losses: Package Voltage Regulators reduce losses in the power distribution network since they are small enough to be integrated at the true Point of Load

- Improve Voltage Regulation: Package Voltage Regulators offer ~100x higher regulation bandwidth than conventional solutions, allowing for improved performance and power savings from reduced voltage margins

- Improve Power Management: Ferric's integrated solution improves spatial and temporal granularity for power management by 100x which enables more than 50% power savings depending on workload

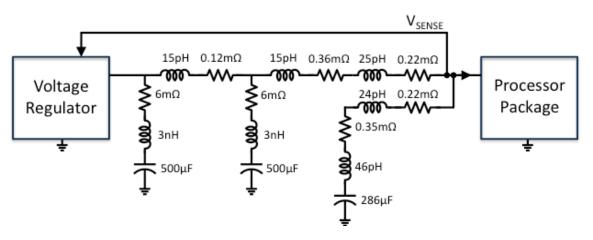

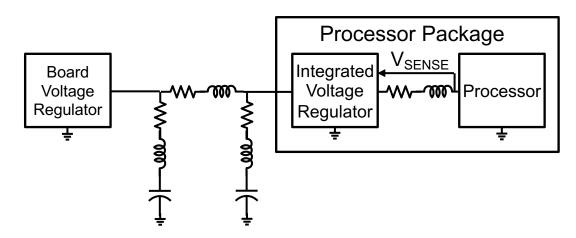

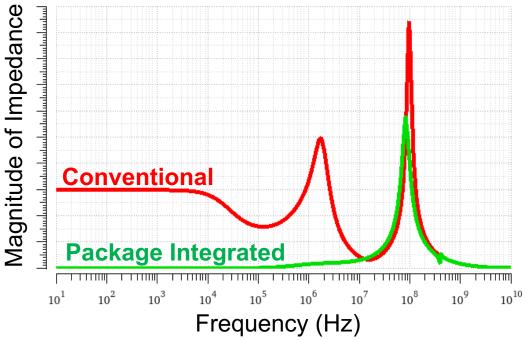

## **PACKAGE VR** Improved Power Integrity

**Conventional Power Delivery Network (PDN)**

#### **Integrated Power Delivery Network (PDN)**

High bandwidth (>50MHz) feedback in immediate proximity to the load:

- Reduce maximum broadband supply impedance to << 1mΩ</p>

- Reduce processor supply voltage margins for improved efficiency

- Regulate resonant impedance peaks from upstream PDN

## **PACKAGE VR** Improved Power Integrity

#### Conventional Power Delivery Network (PDN) Integrated Power Delivery Network (PDN)

Smaller loop inductance Less bulk capacitance Higher feedback bandwidth Fewer parasitics Less impedance overall

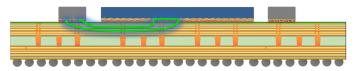

### PACKAGE VR Improved Power Integrity

#### 60A Processor Load Step with Mother Board VR

#### 60A Processor Load Step with Ferric Package VR

2.62

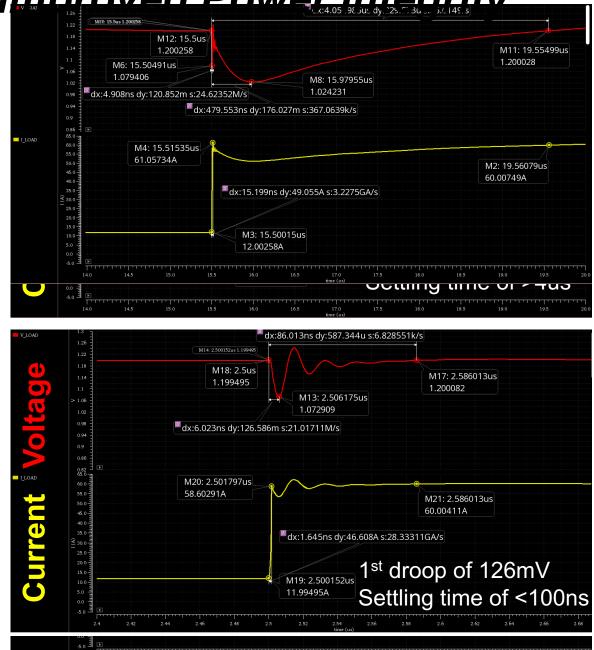

# **PACKAGE VR** Dynamic Voltage Scaling

- Steep Voltage Transitions: Many interleaved buck converter phases, each operating at 100MHz+ switching frequency enables fast voltage transitions ~2mV/ns

- Low Interface Latency: ~200ns of total latency for voltage/state transitions enable aggressive dynamic voltage scaling with associated power savings

- Reduced Transition Penalty: 100x reduction in decoupling capacitance reduces power loss associated with charging and discharging decoupling capacitors

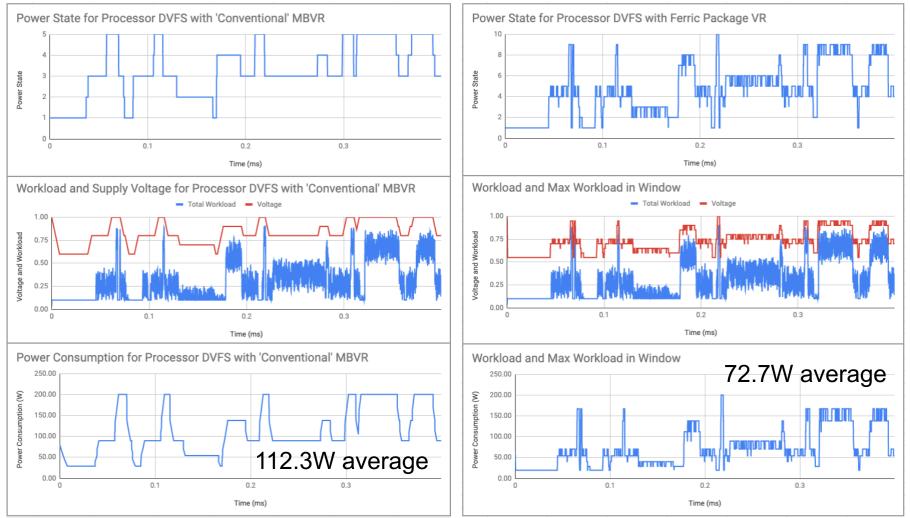

## Fine Grain DVFS with Ferric PVRs

#### Identical Workload and Performance with 35% less power consumption!

## **PACKAGE VR** Power & Data Bottlenecks

Package Voltage Regulators reduce power supply current at Package-to-board interface by ~3x, allowing:

~2x higher signal bandwidth or ~40% reduction in pin count

New bottlenecks for in-package power delivery must be avoided

Power & Data bottlenecks can still occur at chip-to-package interface

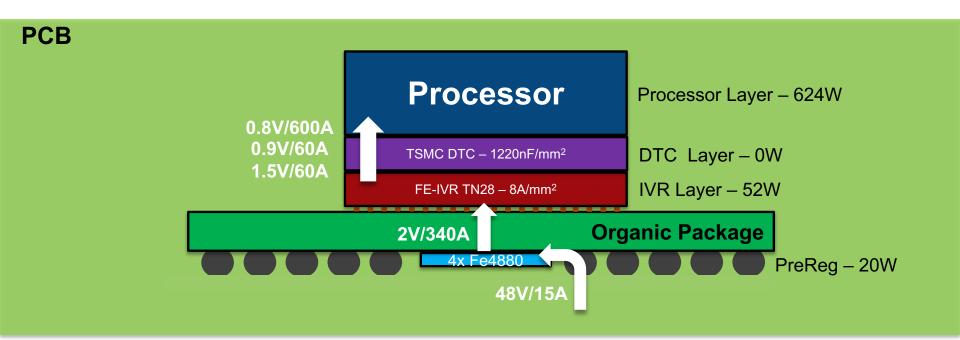

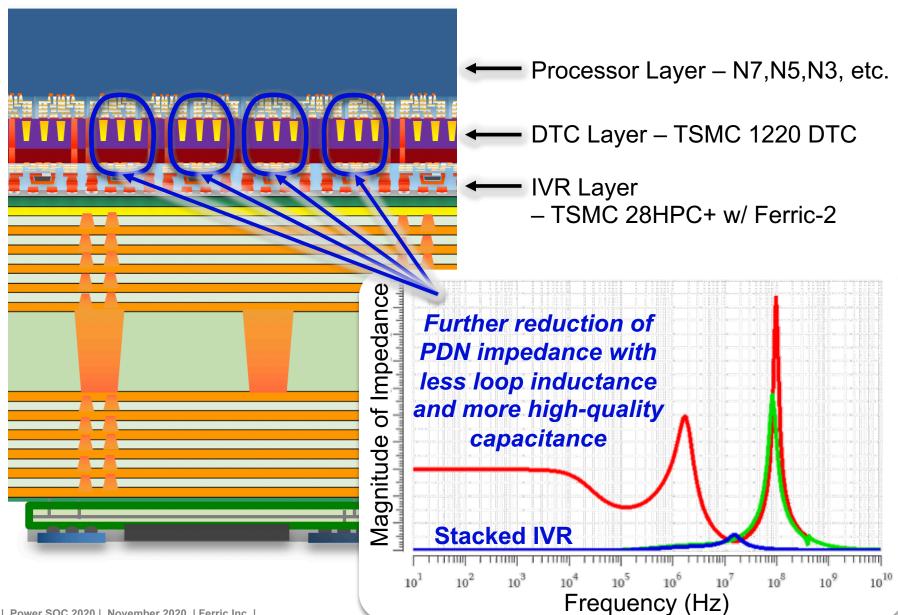

### **Stacked IVR | Example Datacenter Solution**

| Supply   | Converter | Converter | Converter<br>Area<br>(mm2) | Decap<br>Area<br>(mm2) | Decap<br>(uF) | Voltage<br>Ripple<br>(mV) | ASIC<br>Supply | Input<br>Voltage<br>(V) | Input<br>Current<br>(A) | Input<br>Power<br>(W) | Output<br>Voltage<br>(V) | Output<br>Current<br>(A) | Output<br>Power<br>(W) | Total<br>Eff. % | Power<br>Dissipated<br>(W) |

|----------|-----------|-----------|----------------------------|------------------------|---------------|---------------------------|----------------|-------------------------|-------------------------|-----------------------|--------------------------|--------------------------|------------------------|-----------------|----------------------------|

| 1        | - FE-IVR  |           | 75                         | 45                     | 54.9          | <1                        | VDDC           | 2                       | 260.9                   | 521.7                 | 0.8                      | 600                      | 480                    | 92%             | 41.7                       |

| 2        | TN28      | 1 Chip    | 7.5                        | 4.5                    | 5.5           | <1                        | AUX A          | 2                       | 29.3                    | 58.7                  | 0.9                      | 60                       | 54                     | 92%             | 4.7                        |

| 3        |           |           | 7.5                        | 4.5                    | 5.5           | <1                        | AUX B          | 2                       | 47.9                    | 95.7                  | 1.5                      | 60                       | 90                     | 94%             | 5.7                        |

| SUBTOTAL |           |           | 90                         | 54                     | 65.9          |                           |                |                         | 338.1                   | 676.2                 |                          | 720.0                    | 624.0                  |                 | 52.2                       |

|          |           |           |                            |                        |               |                           |                |                         |                         |                       |                          |                          |                        |                 |                            |

| INT      | FE4880    | 4 Modules | 480                        | N/A                    | N/A           | <20                       | PVDD_PVR       | 48                      | 14.5                    | 697.1                 | 2                        | 338.1                    | 676.2                  | 97%             | 20.9                       |

|          |           |           |                            |                        |               |                           |                |                         |                         |                       |                          |                          |                        |                 |                            |

| TOTAL    |           |           |                            |                        |               |                           |                | 48                      | 14.5                    | 697.1                 |                          |                          | 624.0                  | 89.5%           | 73.1                       |

\*assume IVR junction temperature is 85C, otherwise ambient temperature of 75C

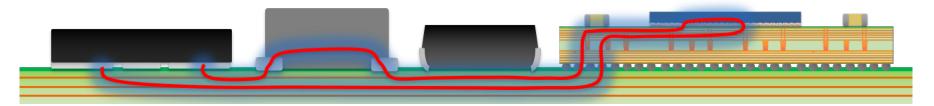

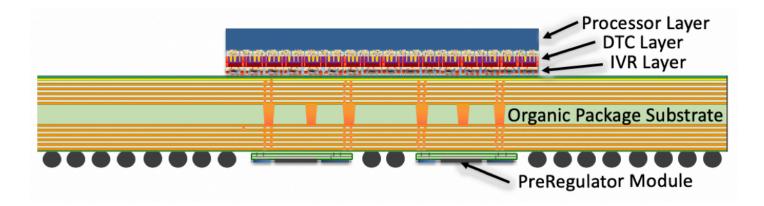

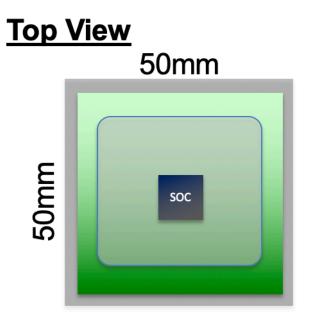

## **Stacked IVR** | Datacenter Solution - Package

#### **Cross Sectional View**

**Bottom View**

| Fe4880 |  |

|--------|--|

|        |  |

| Fe4880 |  |

| Fe4880 |  |

|        |  |

| Fe4880 |  |

| <br>   |  |

14 | Power SOC 2020 | November 2020 | Ferric Inc. |

#### **Stacked IVR** | Datacenter Solution – Cross Section

# QUESTIONS?