# **3D Microfabricated Air-core Inductors for Integrated Power Supply**

Hoà Thanh Lê

DTU Danchip National Center for Micro- and Nanofabrication

**DTU Electrical Engineering** Department of Electrical Engineering

## What is a power supply?

2 PwrSoC18, "3D Microfabricated Air-core Inductors for Integrated Power Supply"

## Want it to disappear?

3 PwrSoC18, "3D Microfabricated Air-core Inductors for Integrated Power Supply"

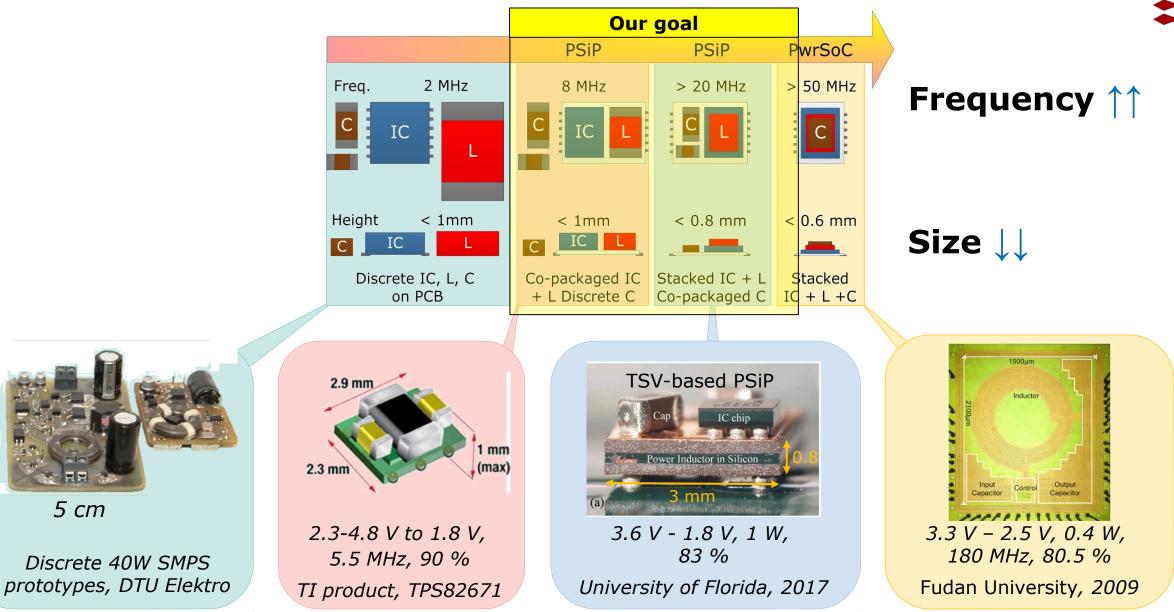

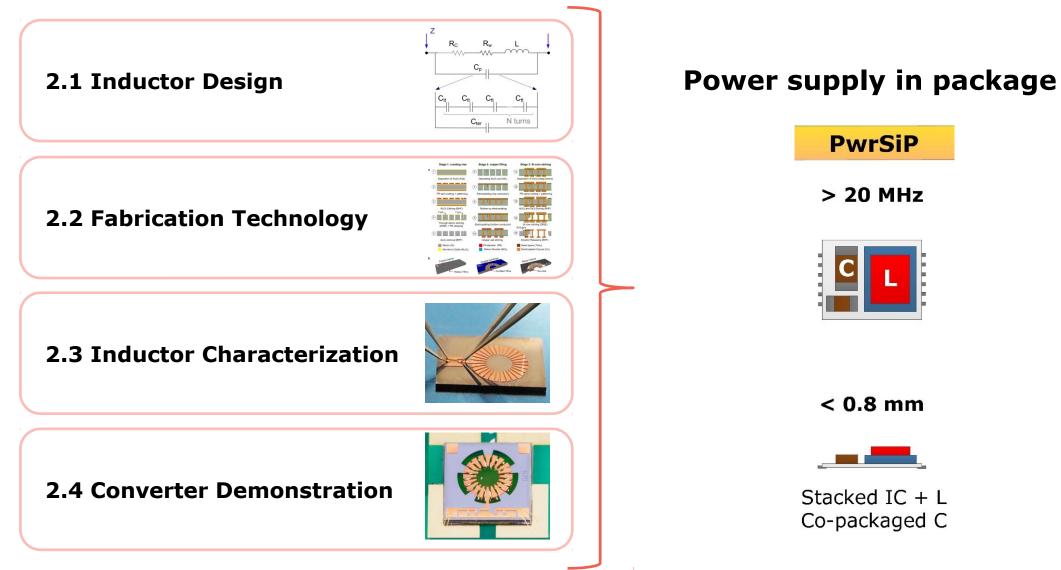

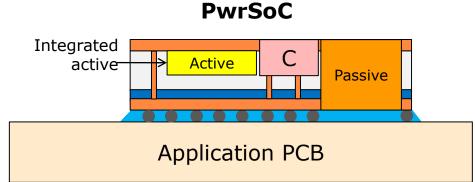

### **Integrated power supplies**

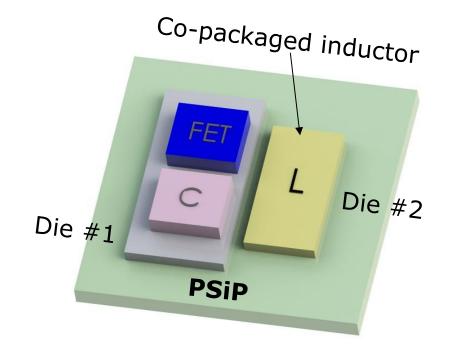

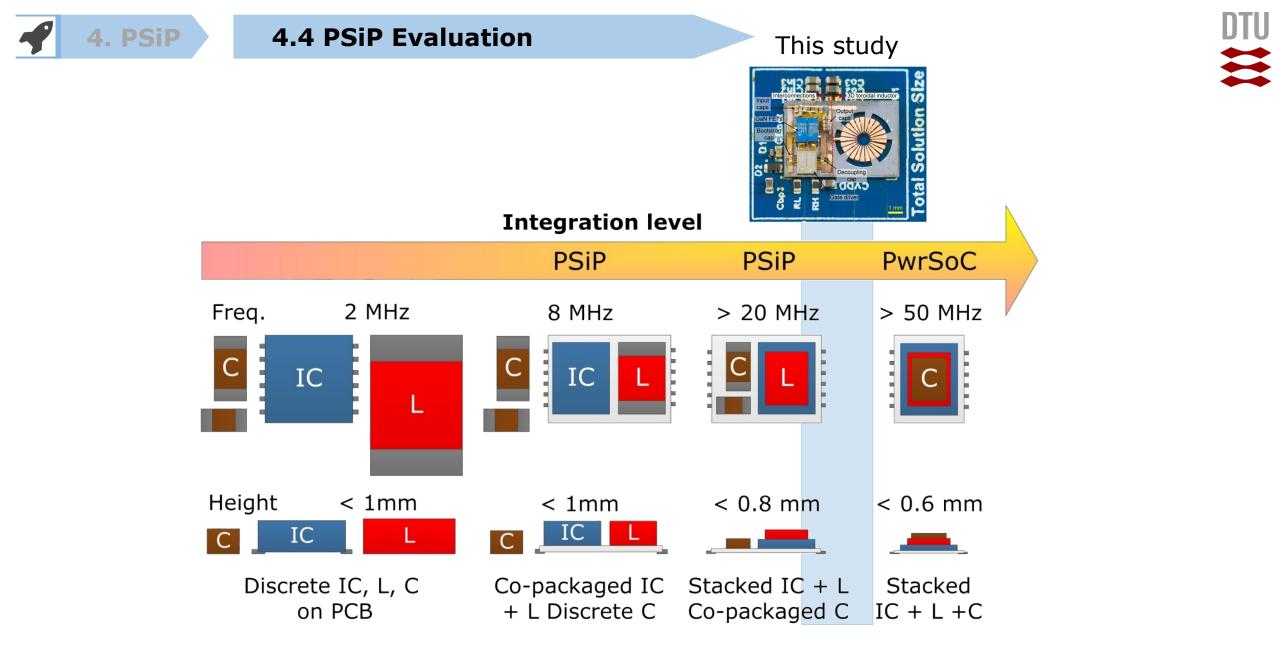

- Power Supply In Packaged (PSiP)

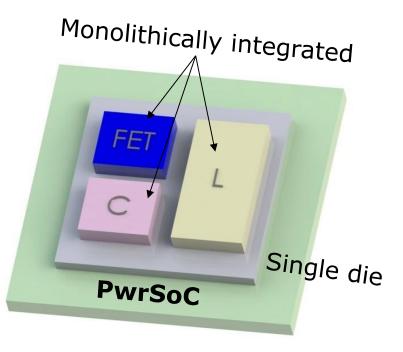

- Power Supply On Chip (PwrSoC)

1. Introduction

#### **PwrSoC Evolution and State of the Art**

6 PwrSoC18, "3D Microfabricated Air-core Inductors for Integrated Power Supply"

Prof. Mathuna et al. 2013, PwrSoC for more than Moore technologies

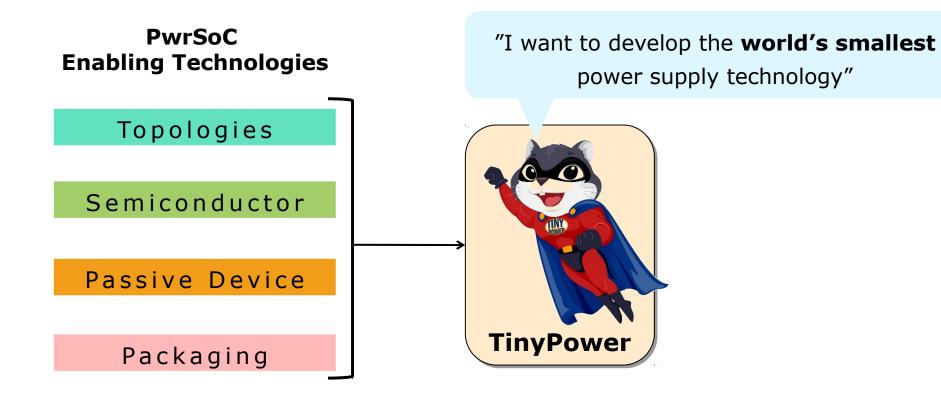

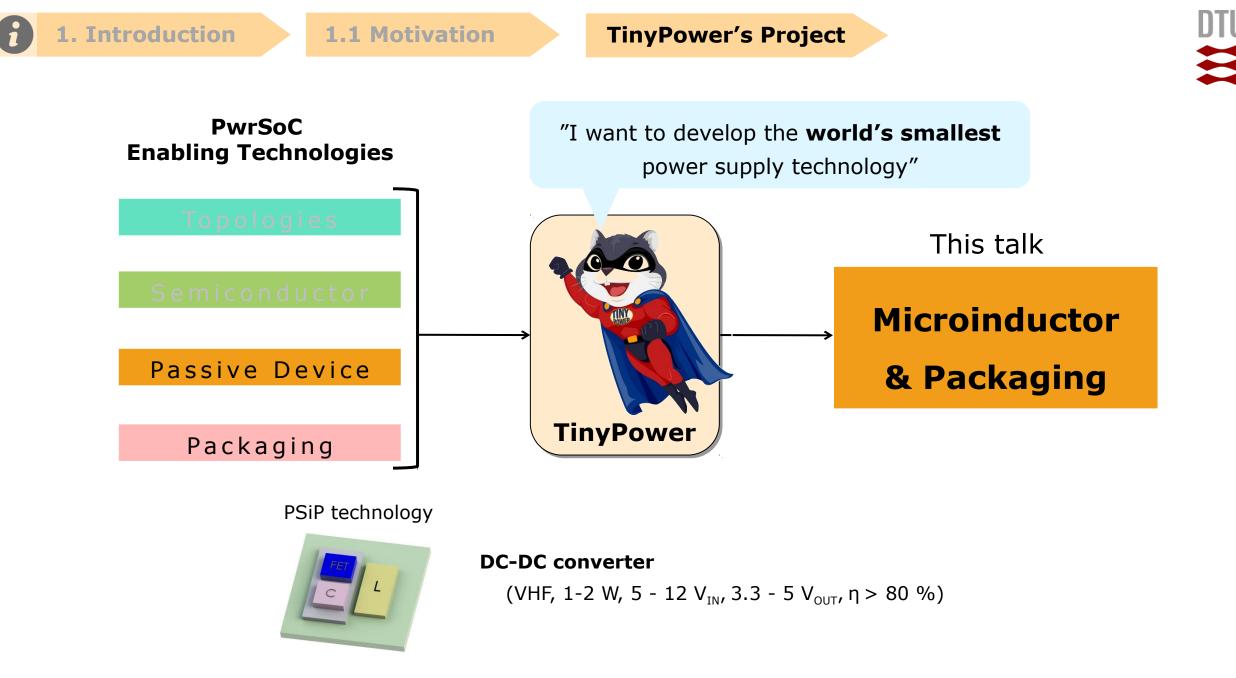

#### **TinyPower's Project**

DTU

**2.3 Problems and Solutions**

2. State of the art 2.1 Mic

### **2.1 Microfabricated Inductor**

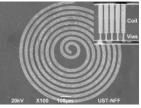

#### Winding structure

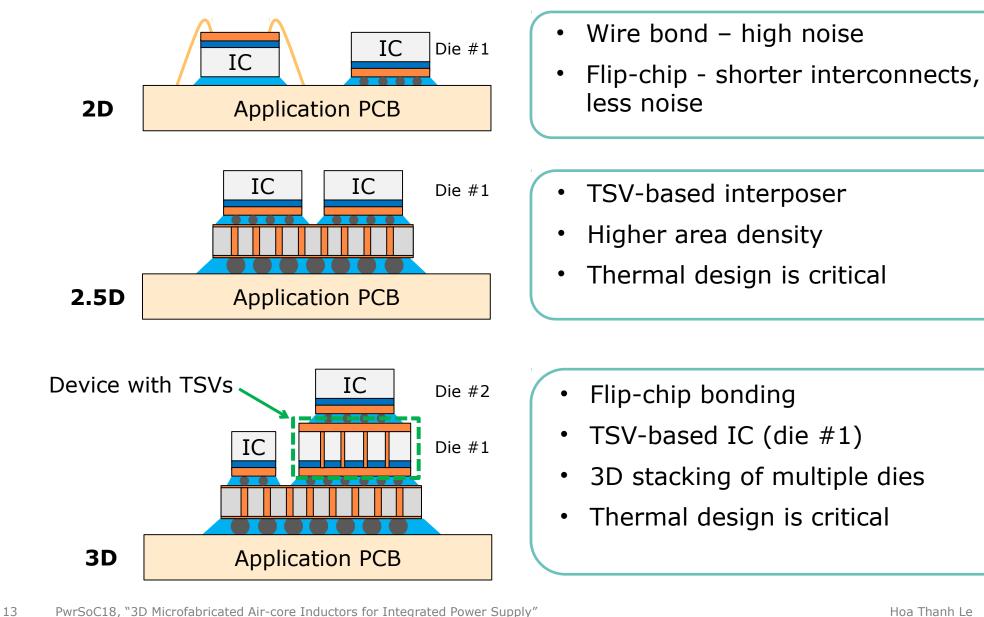

**2D**

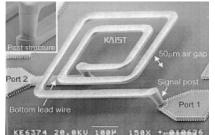

#### 3D

Kim et al. 2013, JMM

#### **Core material**

#### Powder

#### Thin film

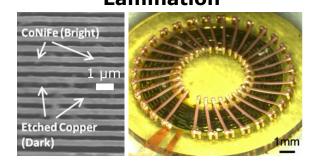

# Lamination

alloy (~ 2.5 µm)

200 µm

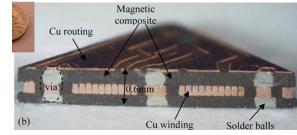

Wang et al. 2011, TPEL Anthony et al. 2014, Micro. Eng. Kim et al. 2013, JMM

### Fab. technology

On-Si

In-Si

Wu et al. 2011, IEEE Elec. Device Let. Wang et al. 2011, TPEL Yu et al. 2013, JMEMS

Volume

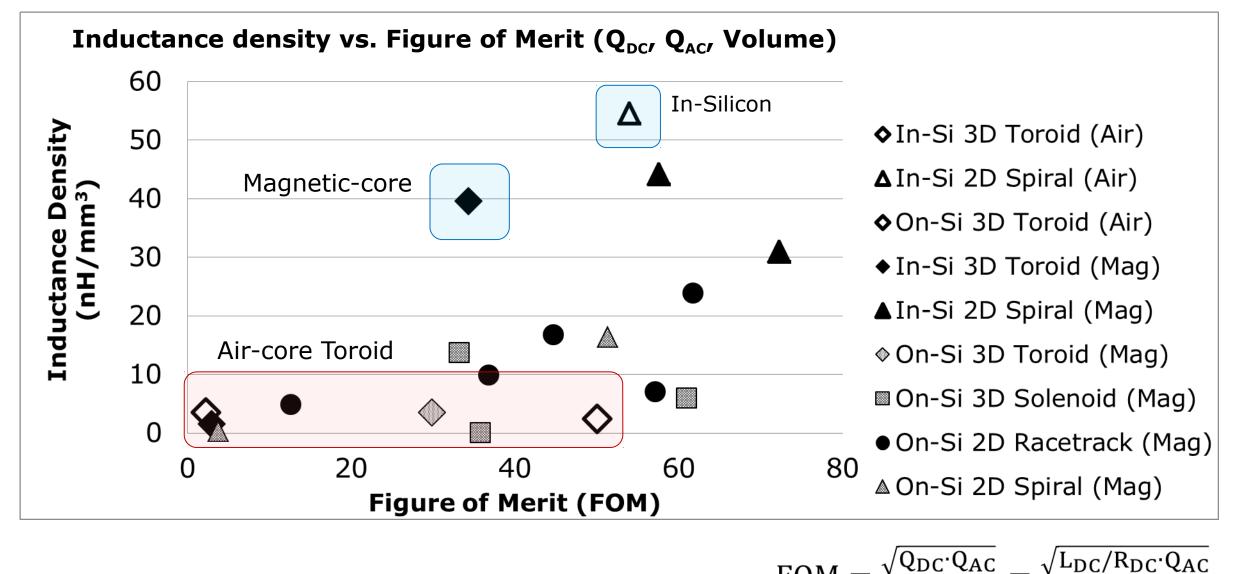

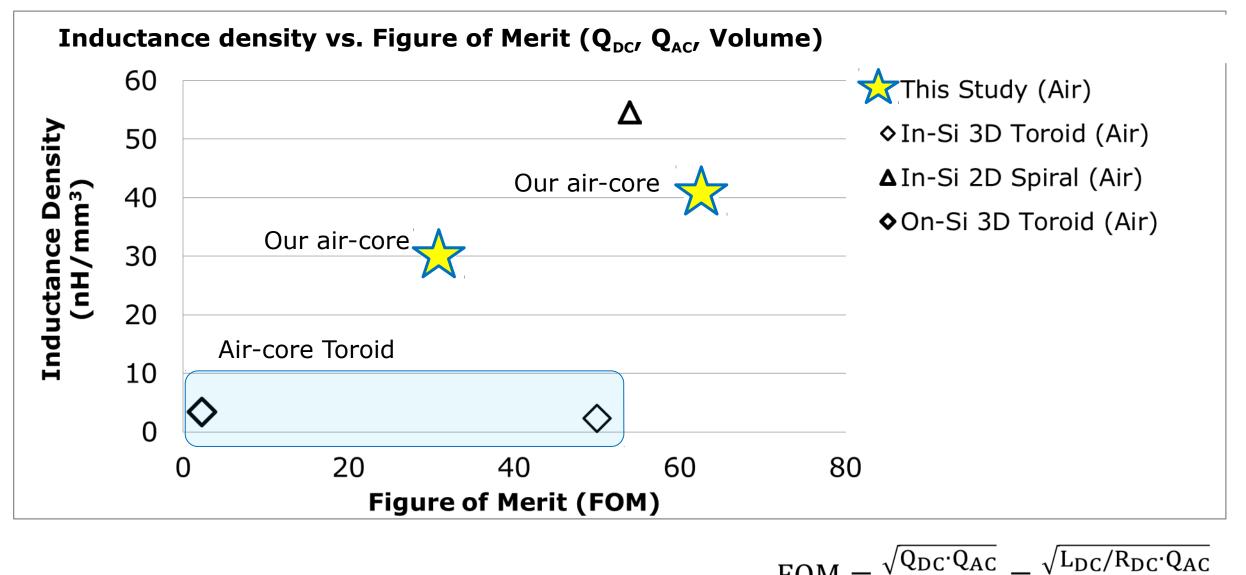

FOM =

Volume

2. State of the art

2. State of the art

2. State of the art

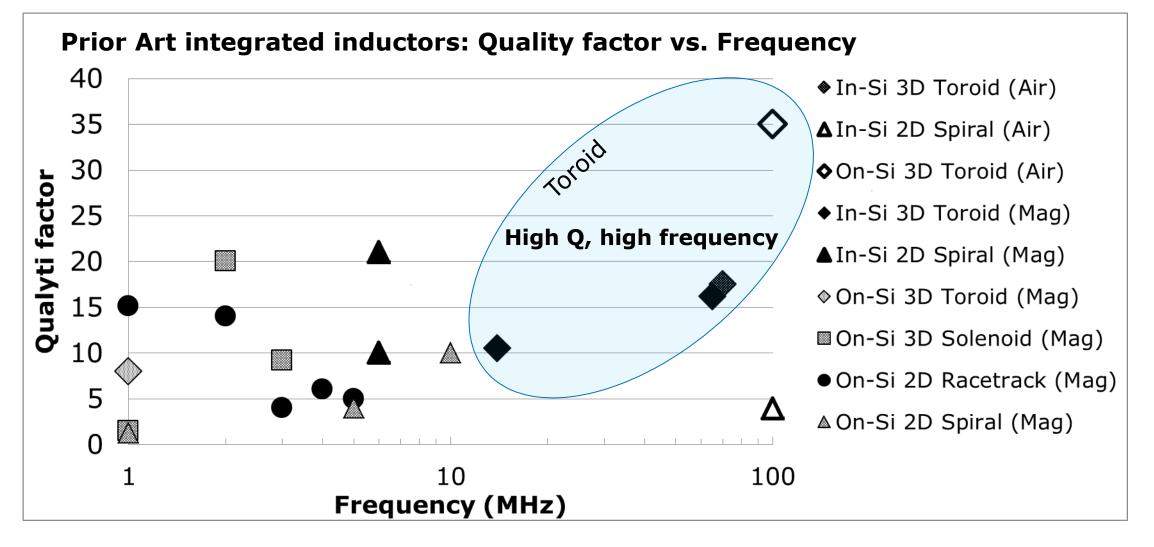

- Lack of a TSV technology for 3D inductor and packaging

- CMOS-compatible for monolithic integration

- Toroidal inductor for high Q, high frequency, low EMI

- In-silicon inductors for low profile

# Solutions?

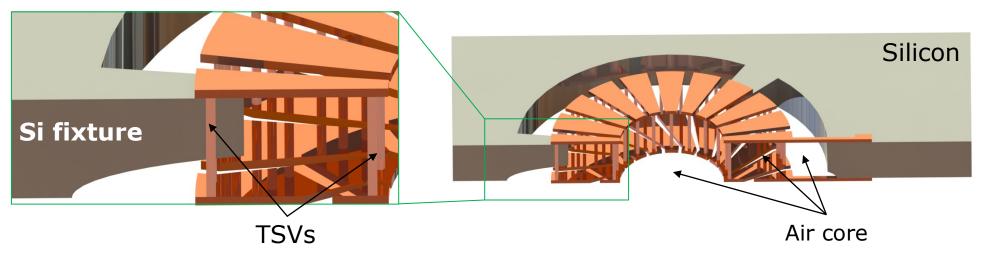

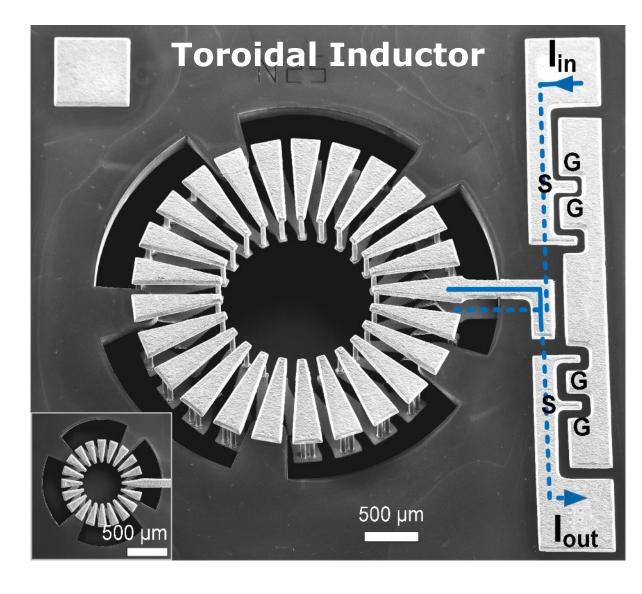

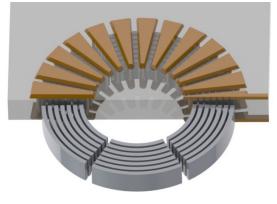

### A novel design of 3D TSV air-core inductor

### Features

- TSV-based inductor

- Free-standing windings without Si core

- Toroidal shape

- Hollow air core

### Advantages

- ✓ In-silicon inductors, 3D packaging

- ✓ Low parasitic -> High Q, high frequency

- ✓ Low EMI with toroidal core

- Possibility for magnetic-core filling

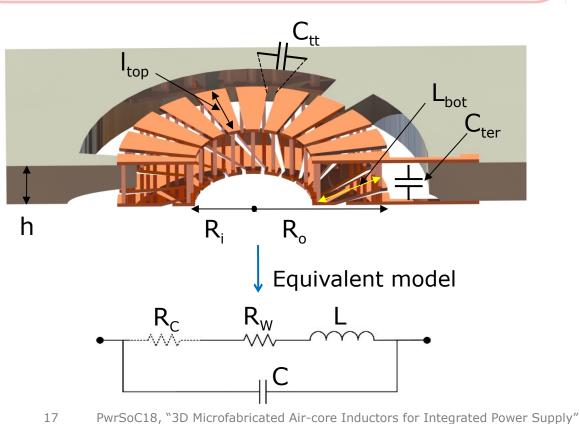

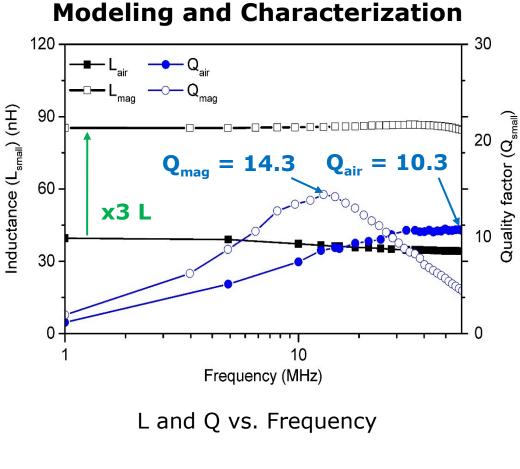

### **Analytical Modeling**

### Inductor model

- predicts inductor's properties (L, R, C, Q)

- is based on an equivalent model

- accounts geometrical dimensions

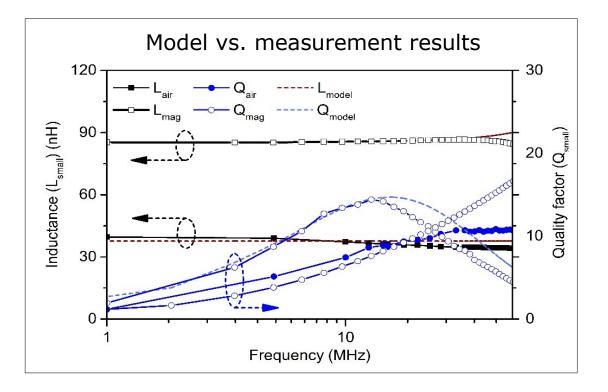

#### Model Accuracy for air-core inductor

- Inductance > 92.7 % (f < 66 MHz)

- Q > 90 % (f < 35 MHz)

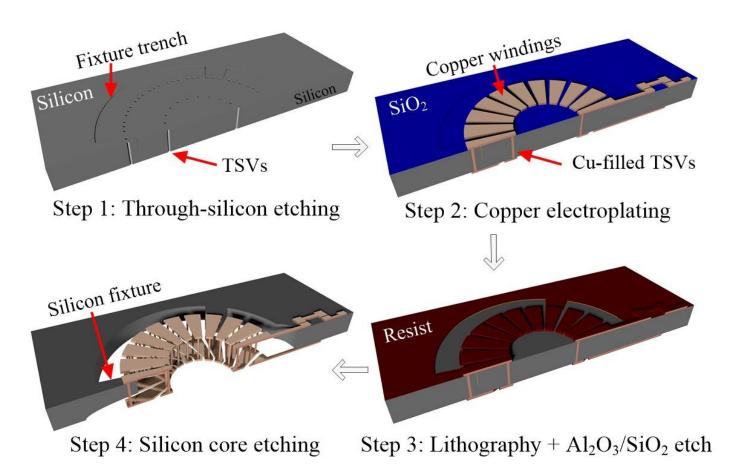

#### **Process 3D Animation**

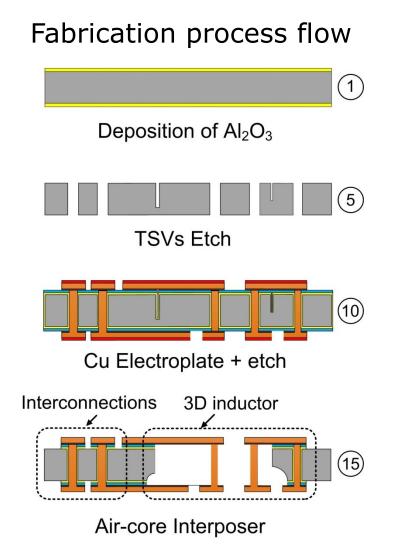

**Step 1** is to create 50-µm-diameter TSVs in a 350-µm-thick wafer by deep reactive ion etching and atomic layer deposition.

**Step 2** includes deposition of insulation layers 50 nm  $Al_2O_3$  and 1.5  $\mu$ m  $SiO_2$ , electroplating of copper in TSVs and top and bottom conductors, and copper wet etching to define the toroidal windings.

**Step 3** starts with protecting Cu windings by  $Al_2O_3$  followed by photolithography of spray-coated resist and wet etching using hydrofluoric acid.

**Step 4** is to etch the silicon core using dry ICP etching and release the suspended windings by wet etching and drying steps.

3D Animation is available at https://www.nature.com/articles/micronano201782

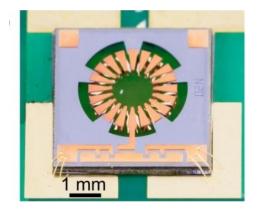

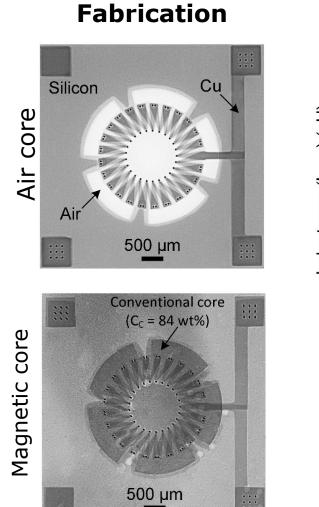

### Fabrication: Air core

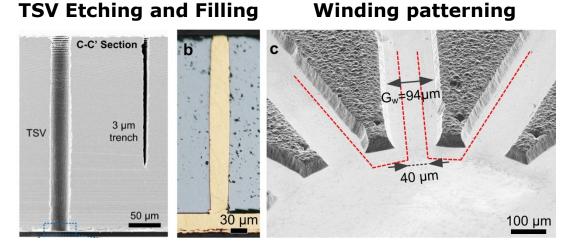

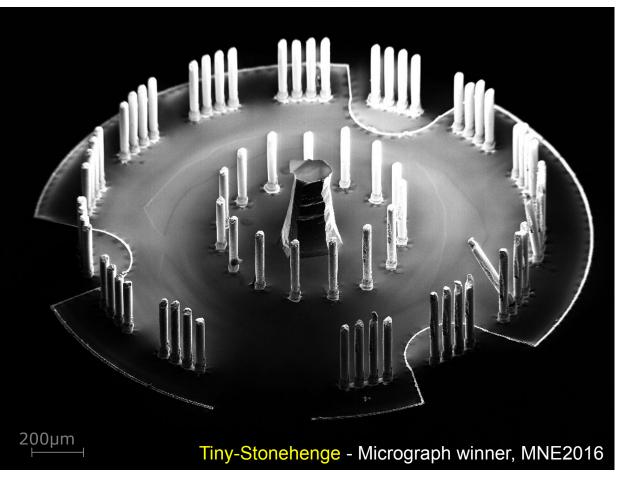

### Fabrication Results at Important Steps

#### Si-core etching and releasing

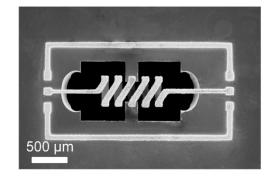

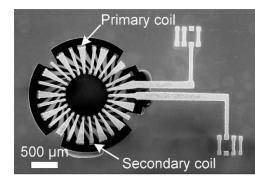

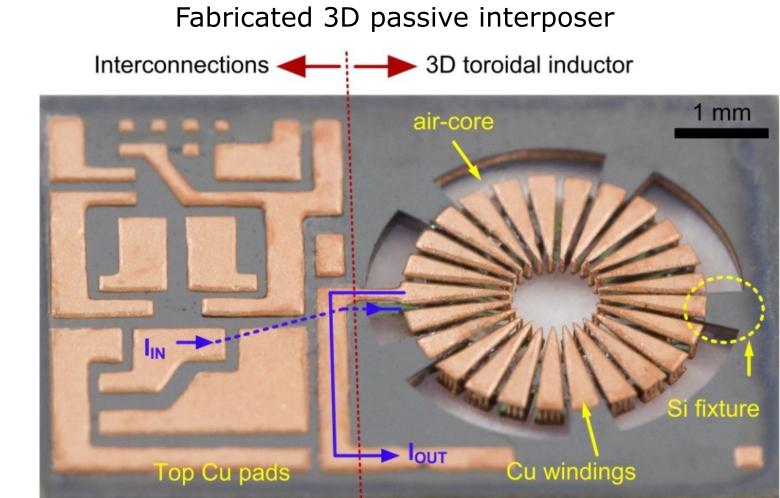

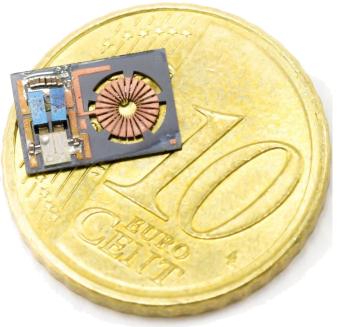

#### 70 Cu-filled TSVs on a 15-turn toroidal inductor

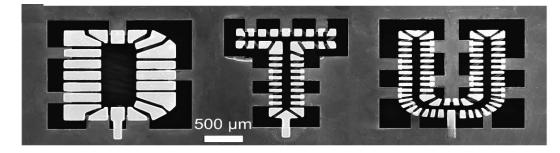

### **Fabrication Results**

Solenoid

Transformer

**DTU Inductor**

Hoa Thanh le et al. 2018, Microsystems & Nanoengineering

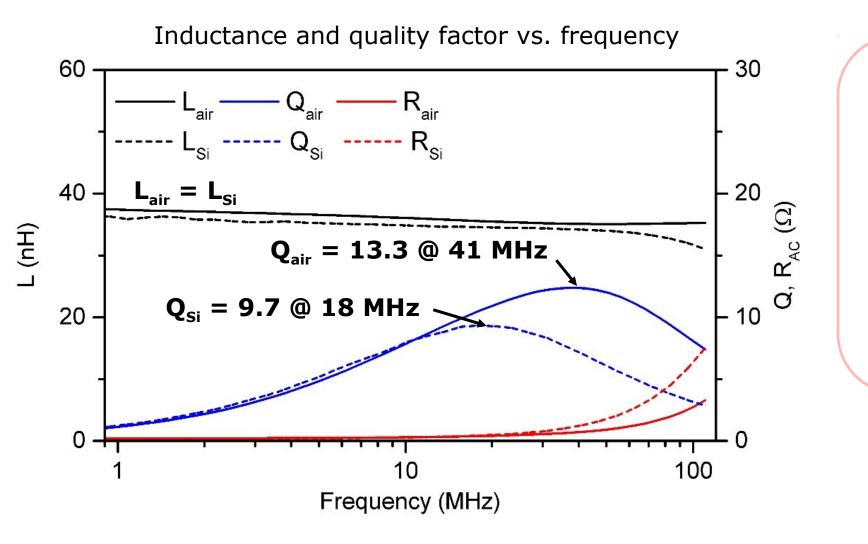

#### **Removing the Si-core**

- 3x less capacitance

- No substrate eddy-current loss

### Highlights

- Same inductance

- 40% higher Q

- 130% higher frequency

#### **Performance Evaluation**

Volume

FOM =

Volum

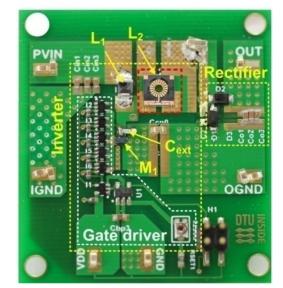

### **Demonstrator 1 with Air-core Inductor**

#### 33 MHz ZVS Boost converter

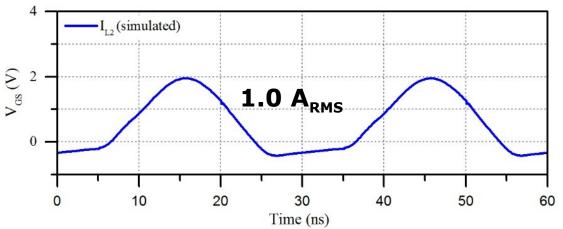

### Inductor

- carry 1 A of RMS current

- 0.98 W loss in inductor (winding loss)

**Converter**: 77% efficiency, 10 W output

Simulated current waveform

Air-core inductor

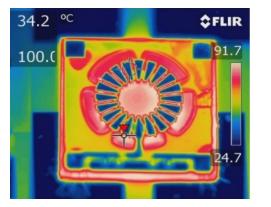

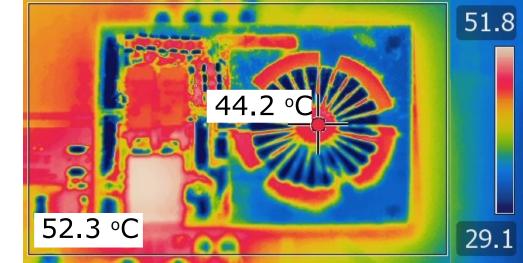

#### Thermal image

Hoa Thanh le et al. 2018, IEEE IESTPE

#### **TSV Magnetic-core Inductors**

24

#### **Converter testing**

$\eta$  = 76%,  $P_{\text{out}}$  = 2.5 W

### Inductor

- $0.5 A_{DC} + 0.86 A RMS$

- 0.63 W loss

#### **Technology Development**

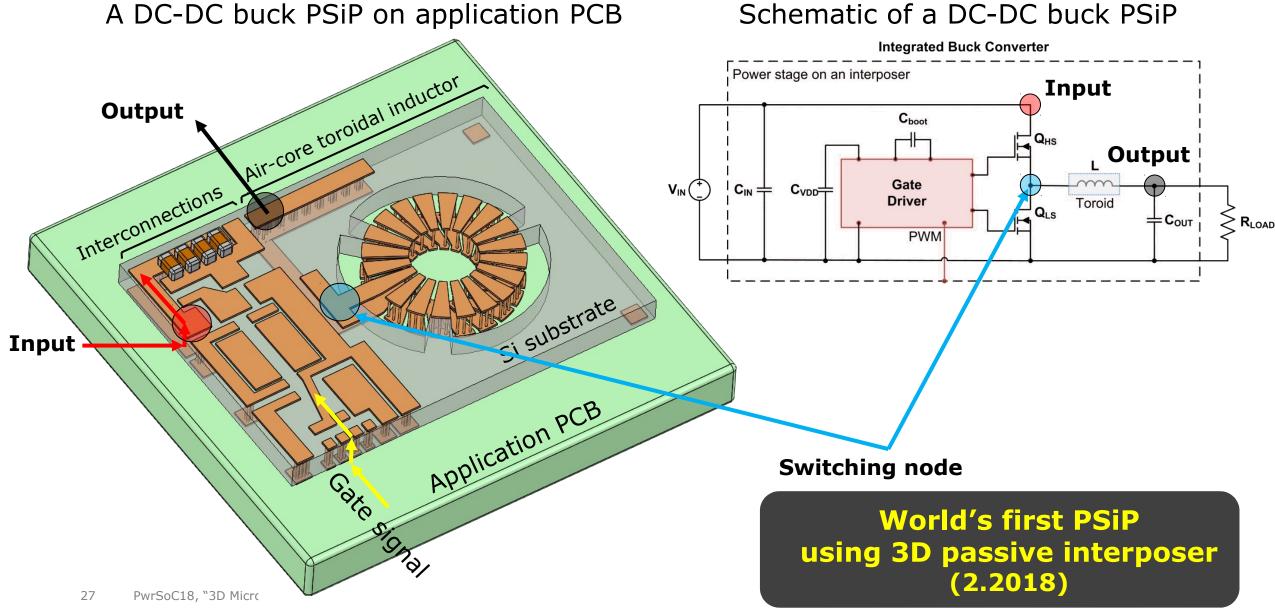

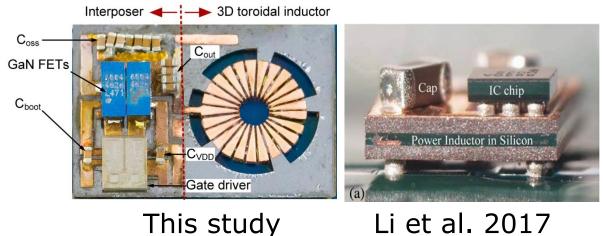

### **Applying the Technology**

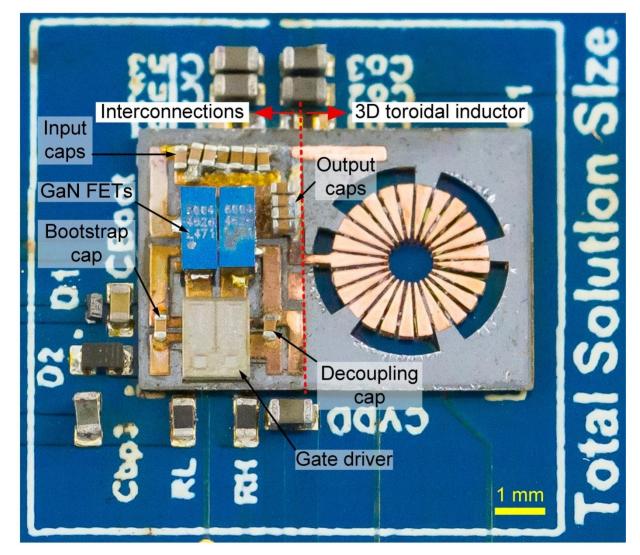

4.2 PSiP Fabrication

4. PSiP

4. PSiP

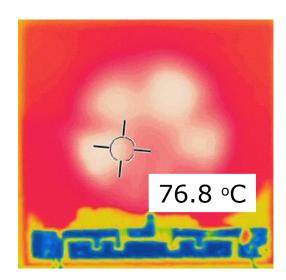

Assembled PSiP with 2 GaN FETs, gate driver, 13 capacitors

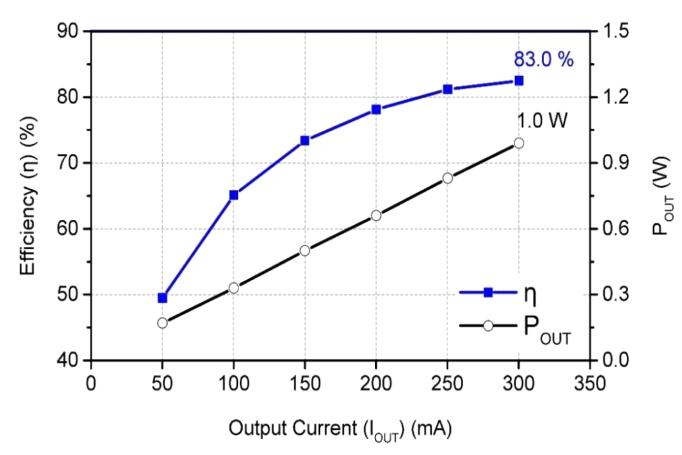

Efficiency and Output power vs. Output current

Thermal image of the inductor in PSiP at  $I_{OUT} = 0.3 \text{ A}$

| Parameters                          | This Study              | Li et al. 2017   |

|-------------------------------------|-------------------------|------------------|

| Size (cm)                           | 0.4 x 0.8 x 0. <b>1</b> | 0.3 x 0.3 x 0.18 |

| V <sub>IN</sub> (V)                 | 3.5 <b>- 8.5</b>        | 3.3              |

| P <sub>OUT</sub> (W)                | 1.15                    | 1.0              |

| P <sub>D</sub> (W/cm <sup>3</sup> ) | 36                      | 60               |

| Efficiency (%)                      | 83                      | 83               |

| f <sub>sw</sub> (MHz)               | 22                      | 6                |

### This study

### Conclusion

- > 3D though-silicon vias (TSV) technology for inductor and packaging

- State-of-the-art inductor performance

- World's First PSiP using 3D Passive Interposer Low-profile, high-η

### **Future Development**

#### **ALD laminated core**

### 5.4 Acknowledgement

**DTU Danchip** National Center for Micro- and Nanofabrication

DTU Electrical Engineering Department of Electrical Engineering

Simplight **niko** servodan