# Advanced power and thermal packaging enabling dense integration of compute nodes

### Dr. Arvind Sridhar

Smart System Integration IBM Research – Zurich, Switzerland

https://www.zurich.ibm.com/st/ https://www.zurich.ibm.com/st/smartsystem/

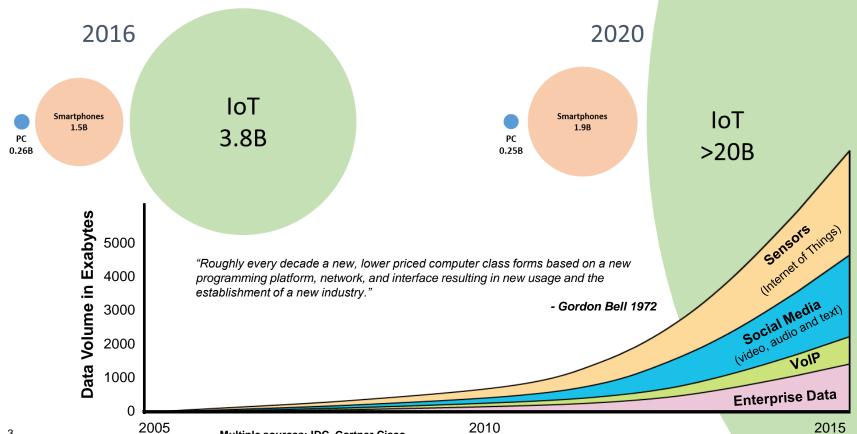

### Bell's law in our times

Multiple sources: IDC, Gartner Cisco

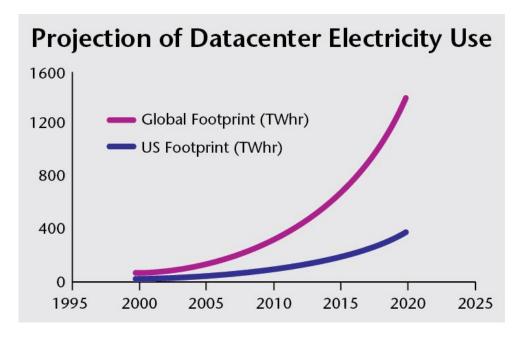

### Is our computing infrastructure up to the task?

3% of global electricity, 2% greenhouse emissions

#### Renewables?

→ no where close to running 100%

#### Efficiency?

- → First energy source

- → 1% improvement in global energy efficiency = 23 nuclear power plants/entire wind power output

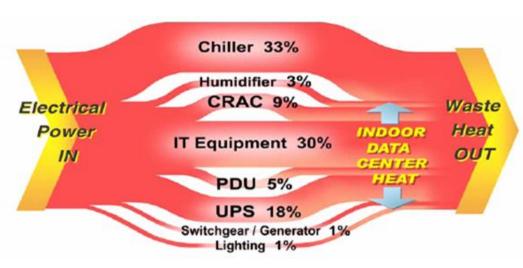

### Where do we improve efficiency?

### Via CMOS scaling?

Since 2006/07: Circuits still become smaller and cheaper, BUT not faster and not more efficient.

Since 2015: Circuits still become smaller but not cheaper → Moore's economic "law" is dead

Transistors for computing occupy much less than 1 ppm of the system volume. Rest for power supply, cooling, and communication

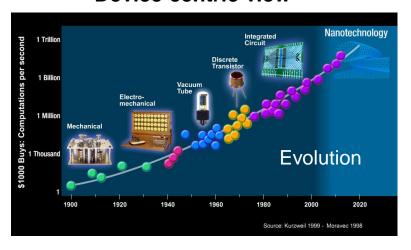

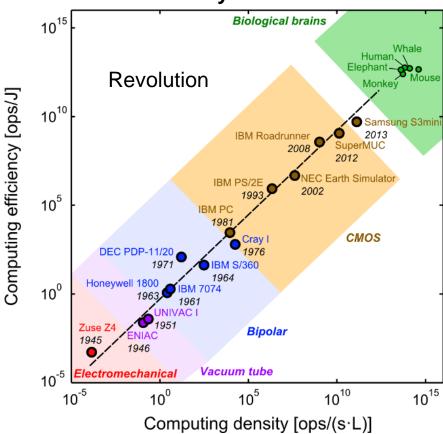

### (R)evolution of Information Technology

#### **Device centric view**

#### **Density centric view**

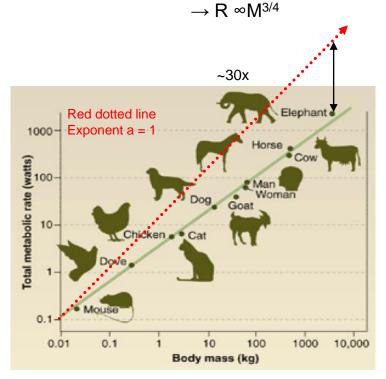

### **Allometric Scaling in Biology**

Basal Metabolic rate of animals scales sub-linearly with mass

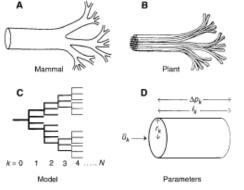

Biology achieves this by:

- 1. efficiency "densification" of supply networks by branching

- 2. combining power delivery and heat removal

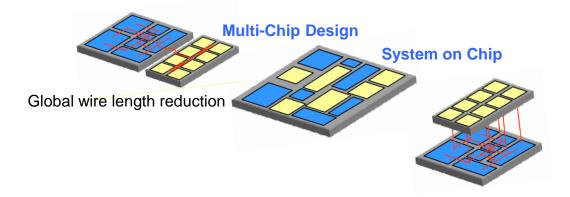

### **Paradigm Change: Vertical Integration**

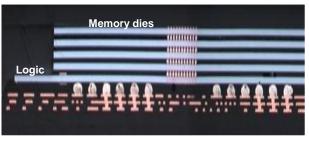

Source: Micron-IBM HMC development

#### Limitations to further scaling:

- 1. Heat removal

- 2. Power delivery

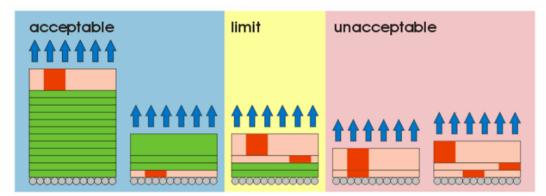

### **Heat Removal**

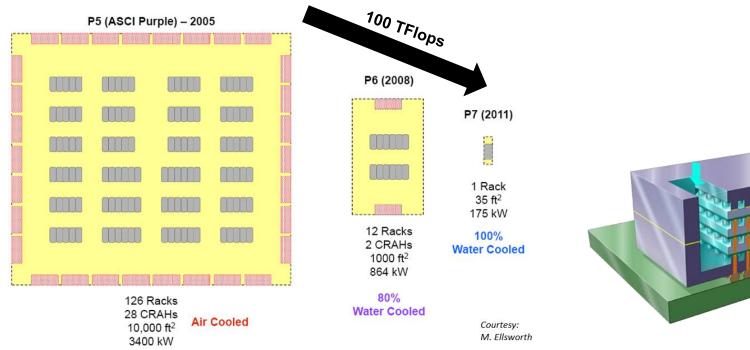

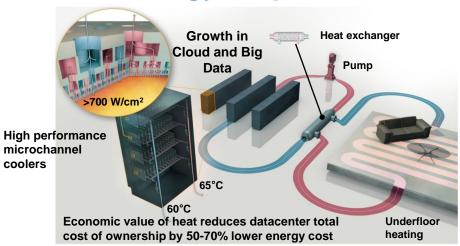

### **Liquid cooling in Datacenters**

- → 16x by node scaling

- → 18x by packaging technology

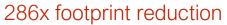

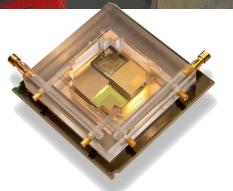

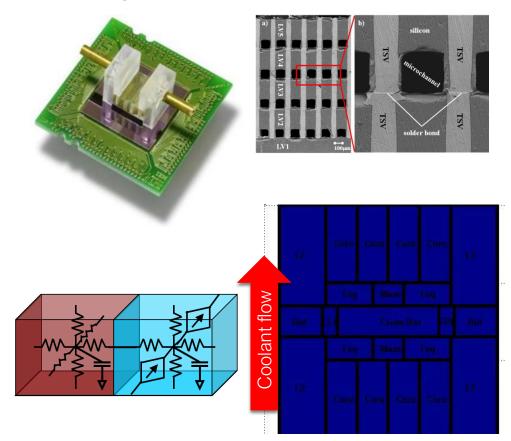

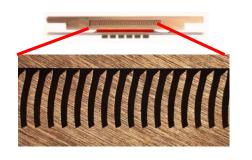

### **Interlayer Liquid Cooling (2005-2015)**

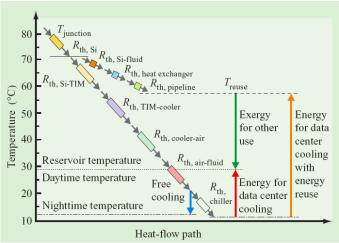

### Water cooling today, and tomorrow...

- Save chiller energy:

Cool with T > 60°C hot

water → Free cooling

- Cold and moderate climates:

- energy re-use

- Hot climates: desalination

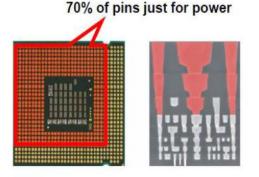

### **Power Delivery**

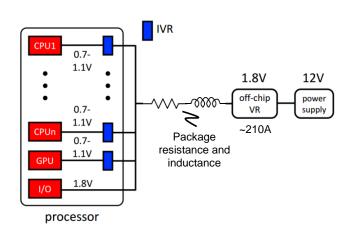

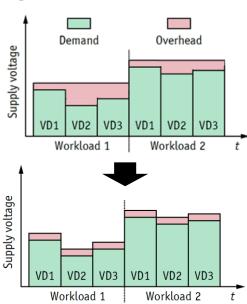

### The Power "bottleneck": need for VR granularity

#### AMD Phenom Quad Core Processor

$\frac{100W - 1V - 100A - 1m\Omega}{(Power \sim 1W/mm^2)}$

Source: C. Mathuna, APEC 2014

#### Goals:

- Bring the point of load (PoL) VRM as close to the processor as possible

- Perform the largest DC-DC down conversion possible

- Have the highest spatial granularity possible

- Follow the fast changes in CPU activity

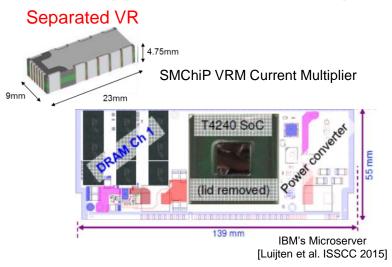

#### Different approaches to iVRs: separated, fully and hybrid

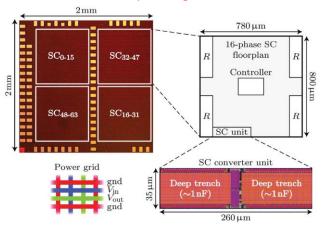

#### Fully Integrated VR

IBM/ETHZ's Switched Capacitor IBM 32nm Sol [Andersen et al. ISSCC 2015]

#### Hybrid Integrated VR

Intel's FIVR buck converter CMOS 22nm air-core L on laminate [Burton et al. APEC 2014]

IBM/Columbia U's iVR25D buck converter CMOS 45nm magnetic-core L on Interposer [Strucken et al. JSSC 2013]

Intel FIVR CMOS 14nm discrete L post processed [ISSCC 2017]

#### CarrlCool Project (EU-FP7, 2014-2017)

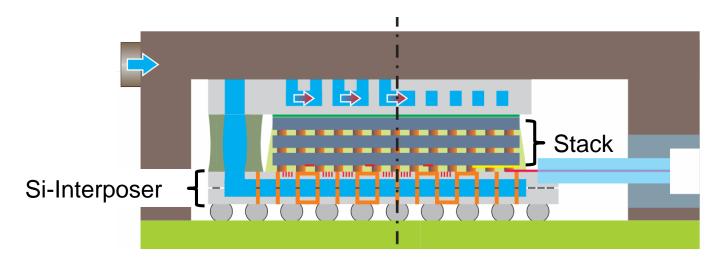

#### A silicon interposer that:

- provides liquid cooling

- delivers power using a VRM

- provides a high-speed optical link

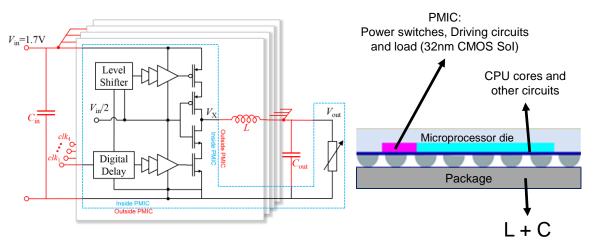

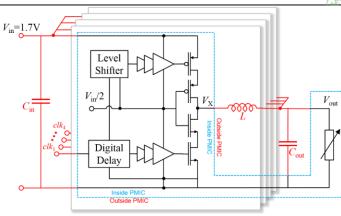

### **CarrlCool Hybrid iVR Implementation**

- Provide accurate voltage regulation for conversion ratios < 1</li>

- Very simple/robust topology

- IVR challenges:

- Switches and control circuits: perform better if low loss. Can make use of the latest CMOS technology

- Inductors (and capacitors): require large structures, can't be compact enough for silicon. Don't need cutting-edge process.

| Paramete<br>r           | Description                    | Value        |

|-------------------------|--------------------------------|--------------|

| V <sub>in</sub>         | Input voltage                  | 1.6 V        |

| $V_{out}$               | Nominal output voltage         | 0.8 V        |

| P <sub>out, max</sub>   | Max output Power               | 800mW        |

| η                       | Efficiency                     | ≥ 90%        |

| PD <sub>Chip</sub>      | Power density on PMIC          | ≥<br>30W/mm² |

| PD <sub>Interpose</sub> | Power density on<br>Interposer | ≥ 1W/mm²     |

| ΔV <sub>out, pp</sub>   | Max ripple                     | 8 mV         |

| t <sub>sett, load</sub> | Settling time                  | 40 ns        |

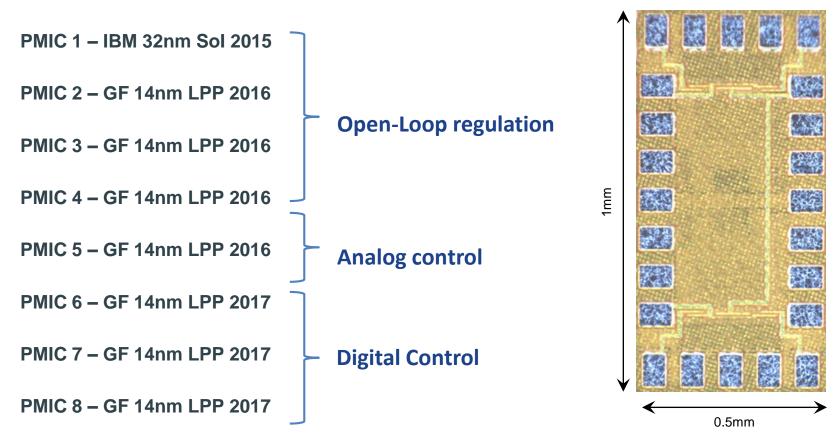

### CarrlCool iVR technologies

#### **PMIC**

32nm IBM Sol process/ 14nm GF Bulk

HITEC, HITEN, & CICMT 2013]

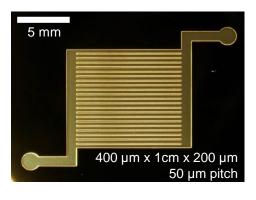

#### **Air-core Inductors**

Fabricated using the RDL layers on the interposer

Solder Bumps

Power FET

Interposter

[yndall

#### Inductors

Planar or Volumetric Inductors using TSVs with Magnetic core material added using thin film deposition

### **Multiple generation of PMICs**

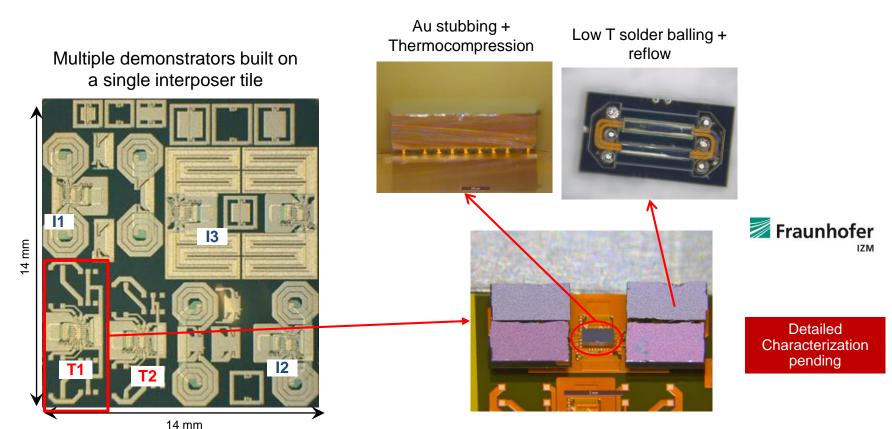

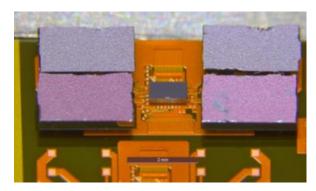

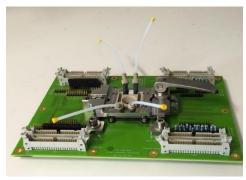

### **CarrlCool iVR demonstrators**

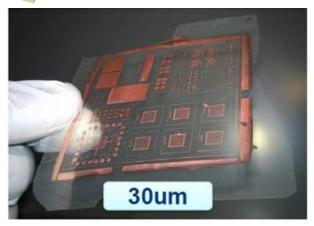

### **Outlook: Exploration of Passive Platforms**

PCB/ organic substrate

Silicon Interposer

Glass Interposer

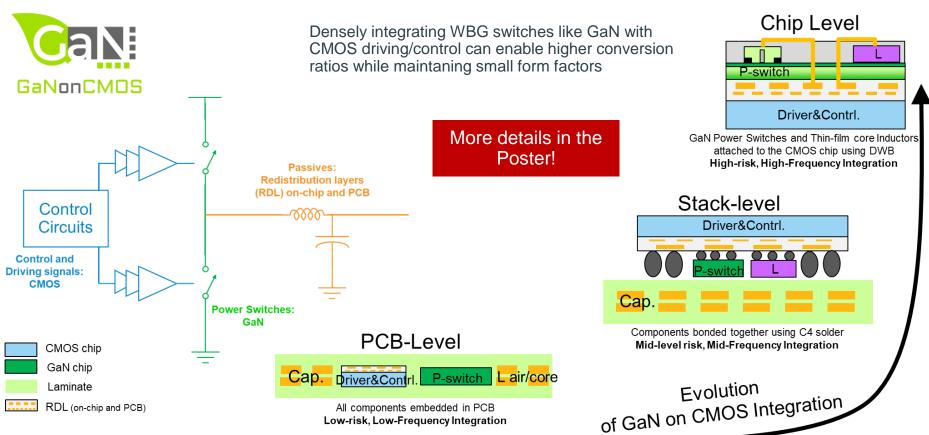

### **GaNonCMOS Project (EU-H2020, 2017-2020)**

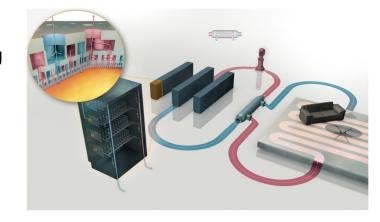

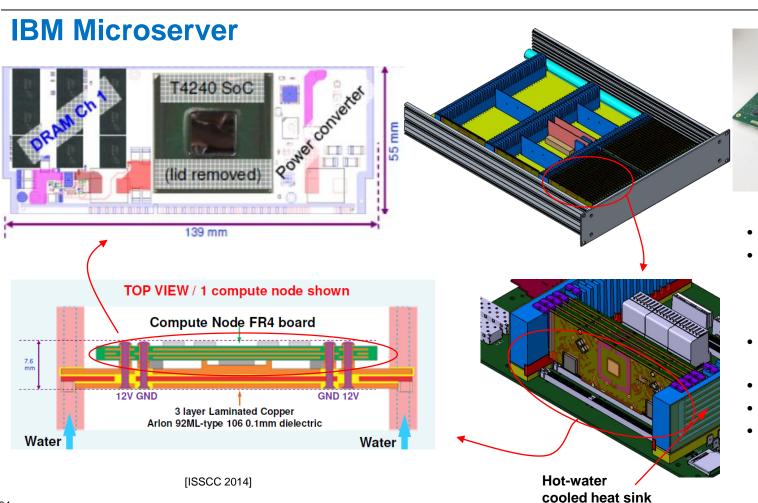

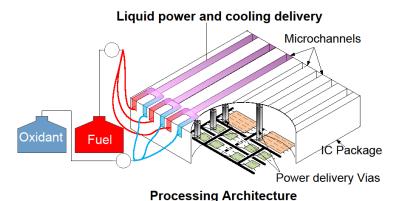

### **Combining Power and Heat**

- Standard 2U Rack

- Low Power/Cost Compute nodes (T4240 1.8GHz, 12 cores)

- 128 nodes 6TB DRAM

- 28 TFLOP

- 1000x Denser

- 10x more efficient than standard HPC Rack

24

### "Electronic Blood" Electrochemical Power Supply on-chip

**Characteristics**

- Chip-level "battery" flow cell array

- Water Soluble redox species

- Co-laminar flow, no membraneless

- Single macroscopic charging unit

- Multiple chip-level discharge units

- Satisfies congruent demand for power delivery and heat removal

#### Test vehicle demonstration

- Process technology feasibility proven

- Challenge: power density order of magnitude lesser than needed

- PCB level scaled flow cell array can still power/cool the CPU

[IEEE Trans Computers 2018]

[International Flow Battery Forum, 2015 & 2017]

**Smarter Energy: Impact Outside of ICT Industry**

**Sustainable generation** Electricity and heat

Fresh water scarcity

Zero-emission datacenter

**High-concentration**

Adsorption heat pump

Membrane distillation desalination

Electrochemical redox energy conversion

© 2017 IBM Corporation

## Thank you!

#### **Organizations**

- IBM Research Zurich Smart Systems Integration Group

- IBM Research Zurich IO Links group

- IBM Research Zurich Heterogenous Cognitive Computing Systems group

- ETH PES group, Zurich Switzerland

- ETH LTNT group, Zurich Switzerland

- EPFL ESL group, Lausanne Switzerland

- Tyndall National Institute, UCC, Cork Ireland

- IPDIA (Murata), Caen France

- Fraunhofer IZM, Dresden Germany

- Fraunhofer IAM, Freiburg Germany

- IHP, Frankfurt (Oder) Germany

#### Funding projects

- EU FP7 CarrlCool

- EU H2020 GaNonCMOS

- SNSF RepCool

- SNSF CMOSAIC

- ASTRON Dome project