# **Embedding Technology Industrialization**

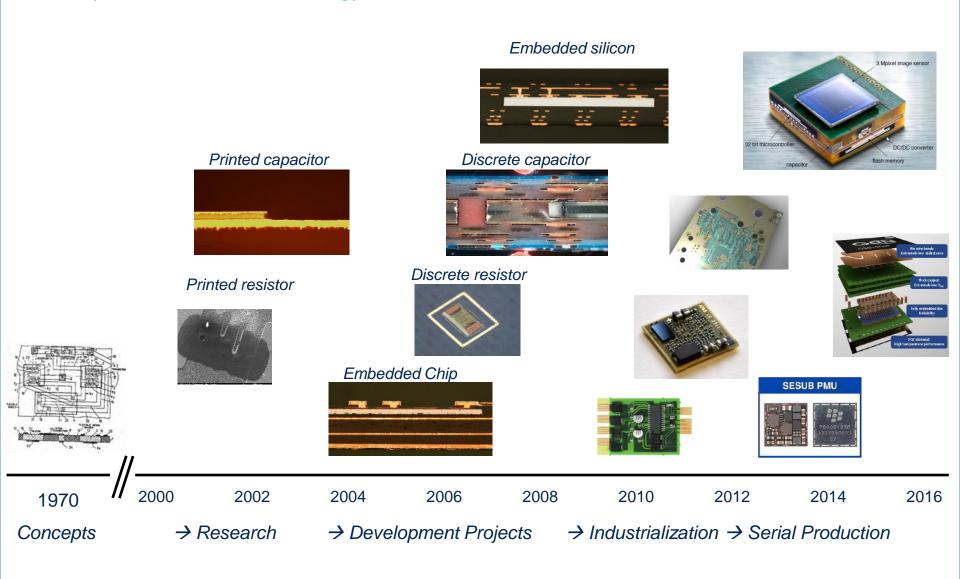

History of embedded Die Technology

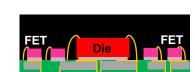

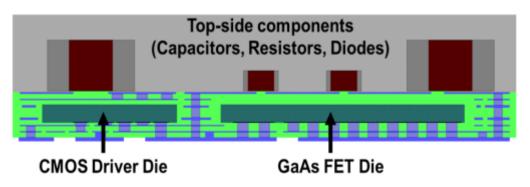

# 3D integration **Chip Embedding** Top-side components (Capacitors, Resistors, Diodes) 3D Interconnect 3D Interconnect Shielding

**CMOS Driver Die**

GaAs FET Die Courtesy of Sarda Technologies, Inc.

Co-Design Lation

SiP Performance (size, electrical & thermal)

# Why Chip Embedding?

| Unique Selling Propositions                                        | in detail                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Miniaturization                                                    | <ul> <li>Footprint reduction</li> <li>Higher component integration (additional assembly layer)</li> </ul>                                                                                                                                              |

| Electrical performance                                             | <ul><li>Improved signal performance (higher data rates)</li><li>Reduction of parasitic effects</li></ul>                                                                                                                                               |

| Mechanical performance                                             | <ul> <li>Higher durability and reliability through copper-to-copper connections (copper filled microvias)</li> <li>Package enables protective enclosure</li> <li>High drop, shock and vibration tolerance</li> </ul>                                   |

| Thermal management                                                 | <ul> <li>Improved heat dissipation through direct copper connection</li> <li>Improved heat dissipation FR4 versus air (compared to SMD)</li> </ul>                                                                                                     |

| Additional functions  - Reduction of overall cost  - EMI shielding | <ul> <li>EMV shielding (partial or full shielding of a package)</li> <li>Package is the housing → no additional molding required</li> </ul>                                                                                                            |

| ECP is supporting the trend towards modularization                 | <ul> <li>Lower set-up costs compared to other packaging technologies (packaging versus PCB processes)</li> <li>Customization of footprint and module versions can be done due to digital imaging - no separate tooling necessary (e.g. QFN)</li> </ul> |

| Anti-Tamper and Security                                           | Hidden electronics preventing reverse engineering and counterfeiting                                                                                                                                                                                   |

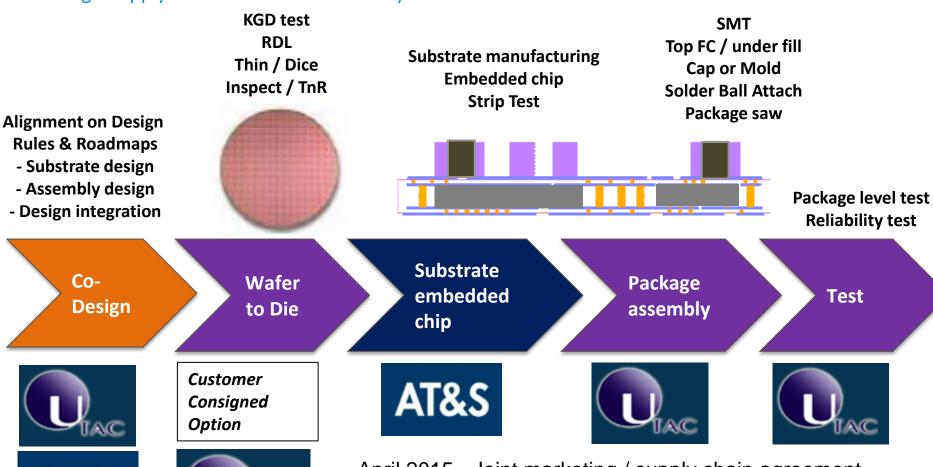

## **Embedding Technology Industrialization**

#### Our collaboration enables customers success

- Global footprint

- Strong R&D focus

- High volume manufacturing experience, capacity and capability

- Brought product portfolio

- Strong customer base

- Long history in embedded technology

### Alignment on

- Business processes

- Aligned technical capabilities

- Common focus on segments and applications

- Global footprint

- High volume manufacturing experience, capacity and capability

- Excellent testing capabilities

- Strong customer base

- Brought experience in backend processing of various applications

# **Supply Chain Offering**

AT&S

Customer

Specs

Strategic supply chain collaboration is a key success factor

April 2015 - Joint marketing / supply chain agreement Between AT&S and UTAC for 3D SiP with embedded chip technology. Collaboration press release April 2016. AT&S over 5 years production embedding experience.

## **UTAC** at a glance

- Outsourced Semiconductor Assembly and Test services (OSAT) provider in support of Analog, Mixed-Signal, Logic, Power and Memory products.

- UTAC 2015 Revenue \$878M; Ranked 6<sup>th</sup> in the Top Ten OSATs

- Focus Assy, Test and Full Turnkey; Test comprises 35% of sales in 2015.

- 1997 Established in Singapore

- Mfg Footprint Singapore, Taiwan, Malaysia, Indonesia, Thailand, China.

- >260K M<sup>2</sup> Manufacturing Space and ~ 12K Employees Globally.

- Sales offices located worldwide.

- Markets: Mobile Phone, Automotive, Security, Wearable's, Industrial & Medical.

## **UTAC** at a glance

## **UTAC Dongguan, China (UDG)**

[Since 1988, >500k sq ft, China Logistics, WW distribution]

BGA, LGA, QFN, Memory Cards, USB, SiP

3D SiP w/ Embedded chip

## **UTAC Thailand (UTL)**

[Since 1973, 640k sq ft, Auto & Security certifications.]

QFN, GQFN, LGA, MIS, MEMS, Power QFN with Cu Clip

## **UTAC Shanghai, China (USC)**

[90k sq ft, WGQ Free trade zone, Focus - Asia customers] QFN, FBGA, LGA, MIS

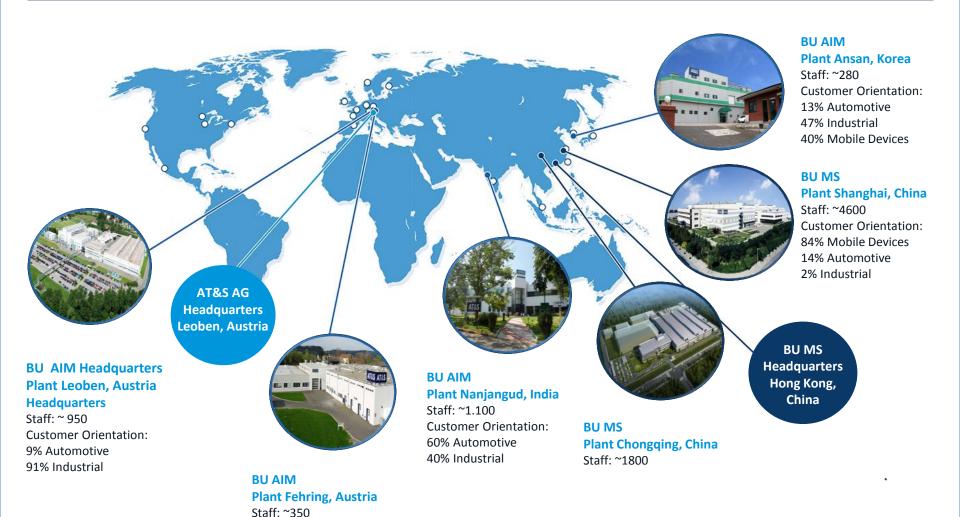

# AT&S – a world leading high-tech PCB company

# High-End Interconnection Solutions

for Mobile Devices, Automotive, Industrial, Medical Applications

9,165 employees

Continuously

Outperforming

market growth

One of the most profitable Players in the Industry:

EBITDA margin of 22% in FY 2015/16

#3

in High-End Technology worldwide

€ 762.9m

Revenue in FY 2015/16, 5.2% organic growth

Cost-competitive production footprint with

6

plants in Europe and Asia

# 1 manufacturer in Europe

# AT&S at a glance & global footprint

**Customer Orientation:**

44% Automotive

56% Industrial

- AT&S AG Headquarters

- o Sales Offices / Representations

- Business Unit Mobile Devices & Substrates (BU MS)

- Business Unit Industrial & Automotive (BU IA)

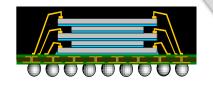

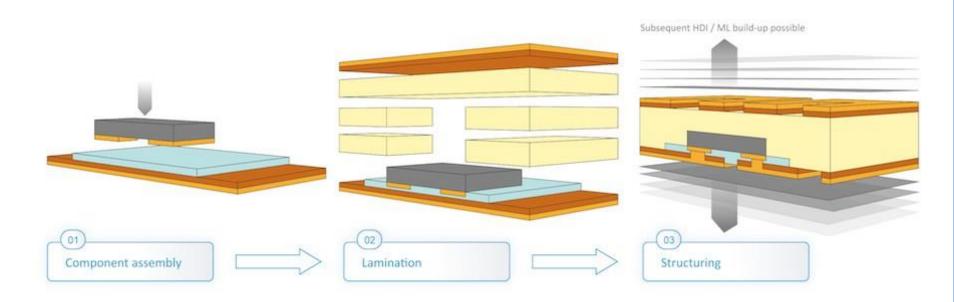

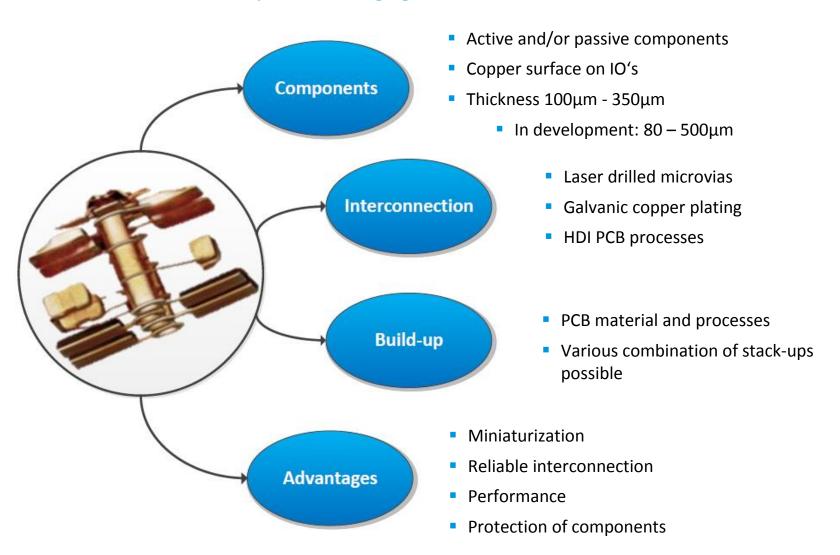

## **ECP®** Basics – What's ECP®

### AT&S ECP® - Embedded Component Packaging

ECP® (Embedded Component Packaging) uses the space in an organic, laminate substrate (Printed Circuit Board) for active and passive components integration

Components embedding into the PCB core with copper plated microvia connections

# **ECP®** Basics – Keyfacts

### AT&S ECP® - Embedded Component Packaging

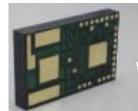

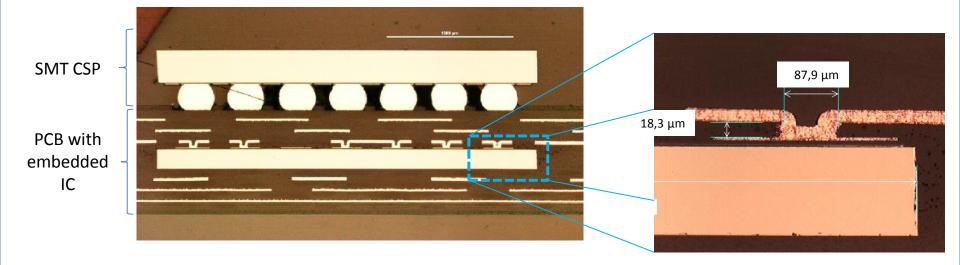

## **Product Illustrations**

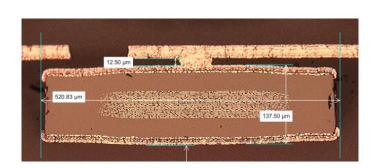

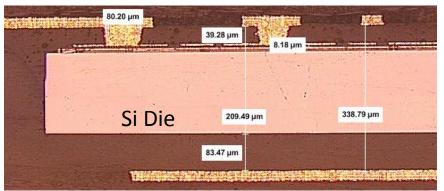

#### X-section of embedded devices

For interconnection, same technology and processes as for HDI/microvia PCBs!

Embedded passives

## **Application Examples**

Package Type: 4.5 x 7.2mm LGA-SIP Highlights: 2 embedded die + 24 passive components on substrate top side

| Package size / Type                                  | 4.5 x 7.2 mm LGA-SIP                           |

|------------------------------------------------------|------------------------------------------------|

| Substrate Thickness                                  | 560 um ± 10%<br>320um core                     |

| Die thickness                                        | 200 um Max.                                    |

| Surface finish (Die DAP)                             | Electrolytic NI/AU                             |

| Surface finish (Land Pad)                            | Electrolytic NI/AU                             |

| # of Passive Component<br>(Top of substrate surface) | 24ea Passive                                   |

| Component Sizes                                      | Passive<br>10ea 01005, 10ea<br>0402, 4ea 0201. |

| # of embedded chip                                   | 2                                              |

| Strip Size                                           | 188x64mm                                       |

| Substrate Metal layer                                | 4 Layer                                        |

### **Assy Layout**

## **UTAC & AT&S Collaboration**

### **Summary**

- System in a package (SiP) is a strategic focus area for UTAC and AT&S

- 3D SiP with Embedded Chip provides integration, size and performance benefits over 2D planar SiP solutions

- 3D Embedded Chip technology adoption is accelerating in Power and High Density Interconnect Applications

- Supply chain collaboration for emerging 3D SiP solutions with embedded chip technology will advanced the technology and provide full turnkey (FTK) supply solutions for customers.

- Flexible business models available to fit to customer requirements