# Monolithic Capacitive Power Converters Towards Higher Voltage Conversion Ratios

Hans Meyvaert Aki Sarafianos Nicolas Butzen Michiel Steyaert

8 October 2014

### **Overview**

Introduction & Motivation

Capacitive AC-DC Step-Down Approach

High Voltage Conversion Ratio DC-DC Approach

Conclusions

### **Problem & Facts**

Although standby power of individual mains connected appliances is low (<1 W), it represent a significant fraction of global electricity consumption due to the large amount of devices

#### **Consumers:**

- TV, VCR, Set-top, Stereo

- Computer

- Kitchen appliances

- External power supplies

- Ceiling fans

#### **Consumption:**

**Annual Domestic Percentage**

- France 2000: 7%

- UK 2004: 8%

- Other: up to 13%

#### **Problem & Facts**

Although standby power of individual mains connected appliances is low (<1 W), it represent a significant fraction of global electricity consumption due to the large amount of devices

#### **Consequence:**

- Emissions: International Energy Agency attributes 1% of 2007 global CO<sub>2</sub> emissions to vampire power

- **⇔** 3% CO<sub>2</sub> due global air traffic

- CO<sub>2</sub> Global warming

- $SO_2$   $\rightarrow$  Acid rain

- Fire risk : Heat dissipation

#### Goal

- Provide low power from the mains with an auxiliary power supply enabling a low loss standby power consumption

- Main power supply fully off

- Low cost

- Low volume

- Low input power

- Optimal power throughput

### **Large Voltage Conversion Ratio Required**

## Bridging the voltage gap

- 1 Series impedance

- Resistor

- Very lossy due to high voltage ratio

- Series capacitor

- Lossless in ideal case

- Large impedance as result of low mains frequency

- V<sub>AC,low</sub>

- Direct mains connection

- Stacked voltage domains (high VCR / Extensive stacking)

#### **Overview**

Introduction & Motivation

Capacitive AC-DC Step-Down Approach

High Voltage Conversion Ratio DC-DC Approach

Conclusions

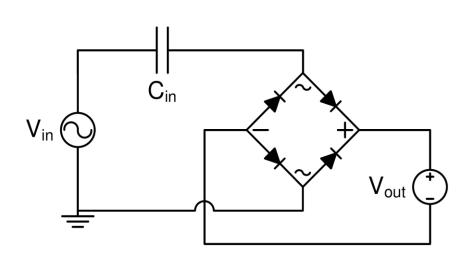

## A Capacitive AC-DC Step-Down Converter

#### Ideal model

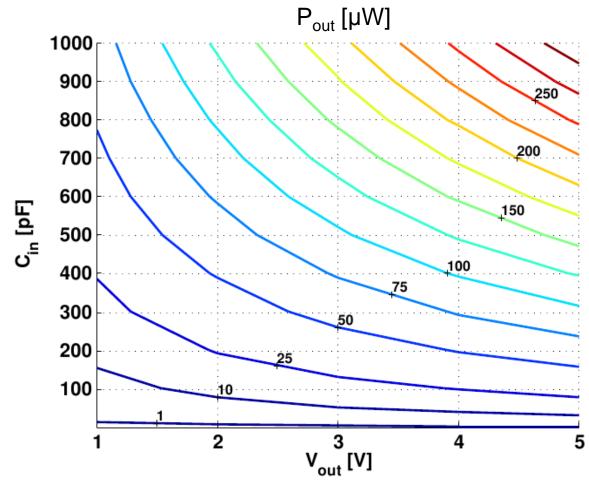

$$-P_{out} = f(V_{out}, C_{in}, f_{mains}, V_{in})$$

— f<sub>mains</sub>, V<sub>in</sub> fixed

$$V_{in}(t) = \sqrt{2}V_{in}sin(2\pi f_{mains}t)$$

$$V_{C_{in}}(t) \approx (\sqrt{2}V_{in} - V_{out})sin(2\pi f_{mains}t)$$

$$i_{C_{in}}(t) = C_{in}\frac{dV_{C_{in}}}{dt}$$

$$= C_{in}(\sqrt{2}V_{in} - V_{out})cos(2\pi f_{mains}t)$$

$$<|i_{C_{in}}|>=4f_{mains}C_{in}(\sqrt{2}V_{in}-V_{out})$$

$$P_{out} = \langle |i_{C_{in}}| \rangle V_{out}$$

## Modeling result

- P<sub>out</sub>(C<sub>in</sub>) linear

- P<sub>out</sub>(V<sub>out</sub>) linear for low V<sub>DC</sub>

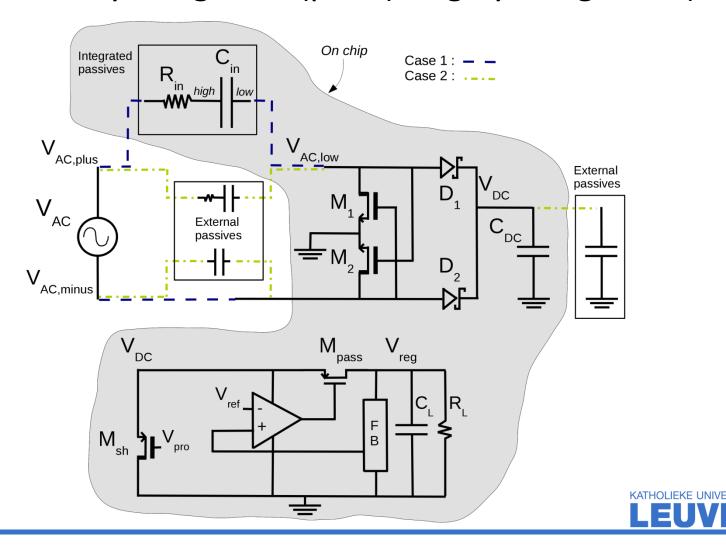

## **Circuit implementation**

2 cases: Fully integrated (μW's), Highly Integrated (mW's)

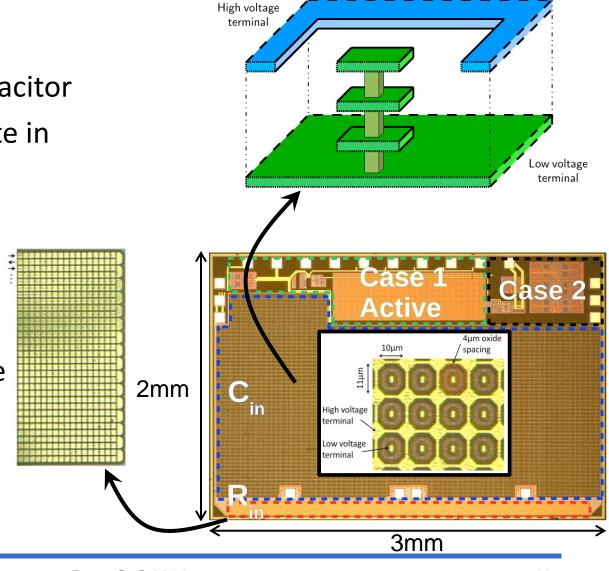

## Chip implementation

#### Capacitor

- Metal-metal capacitor

- High voltage plate in top metal

- 4μm spacing

- -50 pF

#### Resistor

- − 6µm to substrate

- Top metals

- Vias

- $-36 k\Omega$

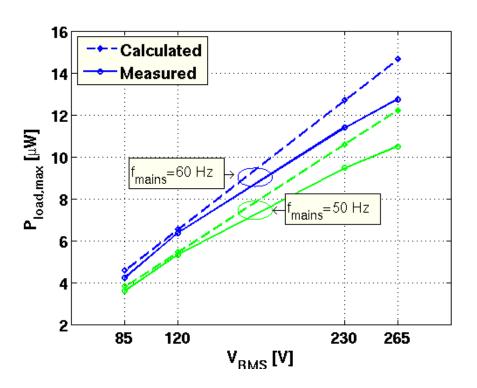

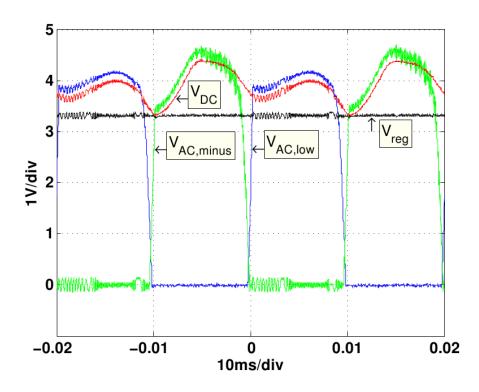

#### Measurements

- Universal mains

- $-85-265V_{rms}$

- 50-60Hz

C<sub>in</sub>: 50pF

US: 6.4 μW

• EU: 9.5 μW

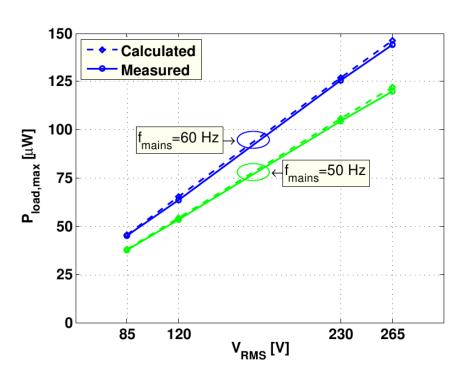

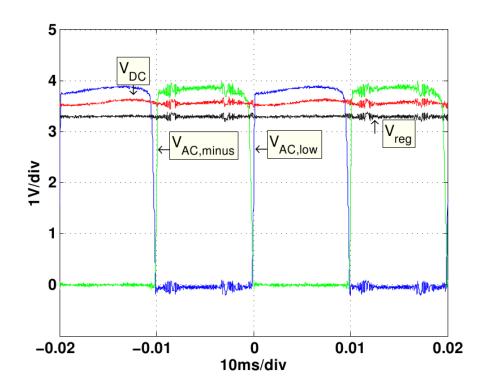

#### Measurements

- Universal mains

- $-85-265V_{rms}$

- 50-60Hz

C<sub>in</sub>: 2x 68nF

US: 4.2 mW

EU: 7 mW

### Measurements

| Reference      | [Tamez, Esscirc'10]   | Cas                  | Case 2 (2x68nF)   |       |       |  |  |

|----------------|-----------------------|----------------------|-------------------|-------|-------|--|--|

| Tech node      | $0.13 \mu \mathrm{m}$ | $0.35 \mu\mathrm{m}$ |                   |       |       |  |  |

| $V_{RMS}$      | 120V                  | 120V                 | 230V              | 120V  | 230V  |  |  |

| $f_{mains}$    | 60Hz                  | 60Hz                 | 50Hz              | 60Hz  | 50Hz  |  |  |

| Power/area     | $0.43 \mu W/mm^2$     | $1.06 \mu W/mm^2$    | $1.58 \mu W/mm^2$ | -     | -     |  |  |

| $V_{reg}$      | 4V                    | 3.3V                 |                   |       |       |  |  |

| $t_{on,diode}$ | 48%                   | 91%                  | 93.5%             | 91%   | 93.5% |  |  |

| $P_{out,max}$  | $1.5 \mu W$           | $6.4\mu W$           | $9.5\mu W$        | 4.2mW | 7mW   |  |  |

### **Overview**

Introduction & Motivation

Capacitive AC-DC Step-Down Approach

High Voltage Conversion Ratio DC-DC Approach

Conclusions

## **Concept & Goal**

- High voltage conversion ratio from a high input voltage with a monolithic IC

- **Switched Capacitor approach?**

- Duty cycle 50%

- **→** Inductive DC-DC converter : PWM

- Monolithic integration

- Voltage domain stacking/serialization

### **Problem considerations**

- What do we <u>need</u> to make a high VCR converter?

- VCR is topology dependant

- Min #capacitors set by Fibonacci Limit (Makowski)

- Higher VCR requires more components

- Switches & Capacitors

- Voltage ratings set by topology

- Control

- Getting signals from start to finish throughout voltage domains

#### **Problem considerations**

What do we have to make a high VCR converter?

Switches

**Impact**

Low voltage: GO1, GO2, (GO3)

'high' f<sub>sw</sub> Ok

High voltage: DMOS

'low' f<sub>sw</sub> only

Capacitors

Low voltage: GOX cap, (MIM cap)

'low' density

High voltage: Fringe cap

'very low' density

#### **Problem considerations**

- What do we need to pay attention to in a monolithic high VCR converter?

- How does VCR influence component requirement?

- Component rating

- Component utilization

- Parasitics related to components

- Ex. parasitic capacitor coupling to substrate with V<sub>c,rated</sub>

Where are the loss contributions coming from?

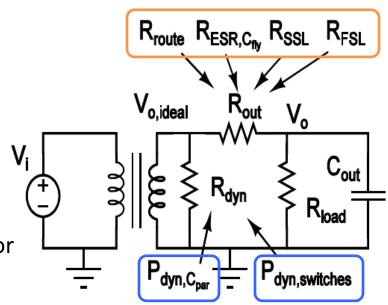

### **CMOS** considerations

- Where are the loss contributions coming from?

- Intrinsic losses

- R<sub>out</sub> related

- Extrinsic losses

- R<sub>dyn</sub> related

- Parasitic capacitor coupling factor

- Parasitic capacitor swing

- $M_{sw} = \sum a_{c,i} V_{Cpar,swing,i}^2$

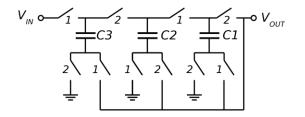

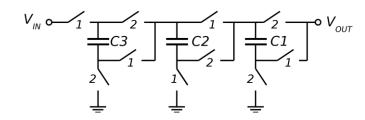

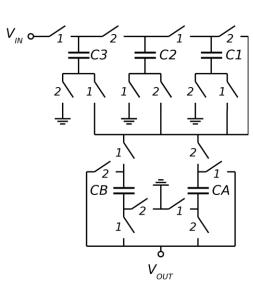

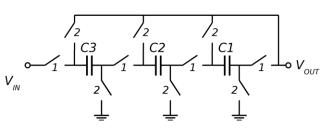

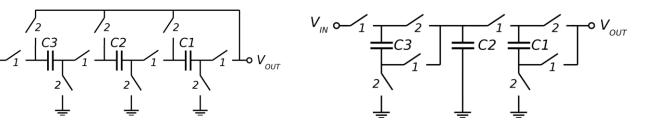

## Investigated topologies

Known to have efficient capacitor utilization

#### (a) Dickson Star 4:1

#### (c) Fibonacci 5:1

#### (d) Dickson Star Embedded Cascade 8:2:1

#### (b) Series parallel 4:1

#### (e) Doubler 4:1

# **Topology results**

|                                                                            | Dickson Star                                 | Series Parallel                             | Fibonacci                            | Dickson Star                                                           | Doubler                                                                                                              |  |  |  |

|----------------------------------------------------------------------------|----------------------------------------------|---------------------------------------------|--------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                            | Diekson Star                                 | Series Taraner                              |                                      | Embedded Cascade                                                       |                                                                                                                      |  |  |  |

| # columns $= k$                                                            | k = N - 1                                    | k = N - 1                                   | $Fib_{k+2} = N^{-a}$                 | $k = \frac{N}{2} - 1^{b}$                                              | $k = 2log_2(N) - 1$                                                                                                  |  |  |  |

| $k_c$                                                                      | $\left[\frac{1}{N} \dots \frac{1}{N}\right]$ | $\left[\frac{1}{N}\ldots\frac{1}{N}\right]$ | $[Fib_1 \dots Fib_k]$                | $\left[\frac{1}{N}\dots\frac{1}{N}\ \frac{1}{4}\ \frac{1}{4}\right]^b$ | $\left[\frac{1}{2} \frac{1}{2^2} \frac{1}{2^2} \frac{1}{2^3} \frac{1}{2^3} \dots \frac{1}{2^N} \frac{1}{2^N}\right]$ |  |  |  |

| $V_{C,rated}$ [ $V_{out}$ ]                                                | $[1 \ 2 \ 3 \dots N-1]$                      | $[1\dots 1]$                                | $[Fib_2 \dots Fib_{k+1}]$            | $[2\ 4\ 6\dots(\frac{N}{2}-1)\ 1\ 1]^{\ b}$                            | $[1\ 2\ 2\ 4\ 4\dots\frac{N}{2}\frac{N}{2}]$                                                                         |  |  |  |

| $V_{sw}$ [ $V_{out}$ ]                                                     | $[1\dots 1]$                                 | $[1\ 2\ 3\dots N\text{-}1]$                 | $[Fib_1 \dots Fib_k]$                | $[2\ldots 2\ 1\ 1]^{\ b}$                                              | $[1 \ 2^1 \ 0 \ 2^2 \ 0 \dots 2^{log_2(N)} \ 0]$                                                                     |  |  |  |

| $M_{sw}$                                                                   | $\frac{N-1}{N}$                              | $\frac{1}{N} \sum_{i=1}^{N-1} i^2$          | $\frac{1}{N}\sum_{i=1}^{k}(Fib_i)^3$ | $2.5 - \frac{4}{N}$                                                    | $\frac{1}{2} + \sum_{i=1}^{(\log_2 N) - 1} 2^{i-1}$                                                                  |  |  |  |

| $K_c = (\sum_{i=1}^{N}  k_{c,i} )^2$                                       | $(\frac{N-1}{N})^2$                          |                                             |                                      |                                                                        | $(\frac{1}{2} + \sum_{i=1}^{(\log_2 N) - 1} 2^{-i})^2$                                                               |  |  |  |

| $K_c, N = \infty$                                                          |                                              |                                             | 1                                    |                                                                        | 2.25                                                                                                                 |  |  |  |

| $M_{sw}, N=2$                                                              | $\frac{1}{2}$                                | $\frac{1}{2}$                               | $\frac{1}{2}$                        | $\frac{1}{2}$                                                          | $\frac{1}{2}$                                                                                                        |  |  |  |

| $M_{sw}, N=4$                                                              | $\frac{3}{4}$                                | 3.5                                         | _                                    | 1.5                                                                    | 1.5                                                                                                                  |  |  |  |

| $M_{sw}, N = 8$                                                            | $\frac{7}{8}$                                | 17.5                                        | 4.62                                 | 2                                                                      | 3.5                                                                                                                  |  |  |  |

| $M_{sw}, N = 16$                                                           | $\frac{15}{16}$                              | 77.5                                        | _                                    | 2.25                                                                   | 7.5                                                                                                                  |  |  |  |

| $M_{sw}, N = 64$                                                           | $\frac{63}{64}$                              | 1333.5                                      | N = 55 - 89 $220.6 - 578$            | 2.375                                                                  | 31.5                                                                                                                 |  |  |  |

| $M_{sw}, N = \infty$                                                       |                                              | $\infty$                                    | $\infty$                             | 2.5                                                                    | $\infty$                                                                                                             |  |  |  |

| $a \ Fib_1 = 1, Fib_2 = 1$ $b \ N > 2$ and $N$ even and $\frac{N}{2}$ even |                                              |                                             |                                      |                                                                        |                                                                                                                      |  |  |  |

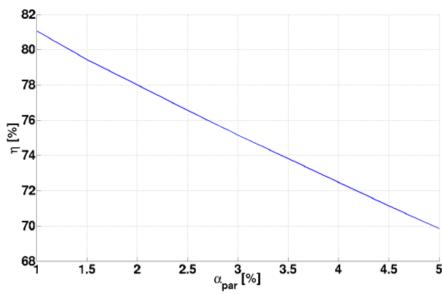

## **Topology Simulations**

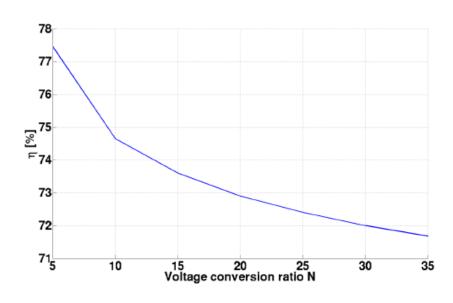

#### Validation of Dickson Star: η[α], η[VCR]

(a) Dickson Star topology with parasitic reduction at VCR=11,  $f_{sw}=10 \mathrm{MHz},~V_{in}=41.7V,~V_{out}=3.3V, P_{out}=40 \mathrm{mW},~C_{tot}=2.9 nF$

(b) Evolution of the converter efficiency with rising voltage conversion ratio,  $f_{sw}=10 \mathrm{MHz}, \ \alpha_{par}=3\%, \ V_{out}=2.5V, P_{out}=20 \mathrm{mW}, \ C_{tot}/V_{in}=1.94 nF/19V$  for N=5 to 2.86 nF/100.5V for N=35

# Inclusion of practical C<sub>fly</sub> voltage rating

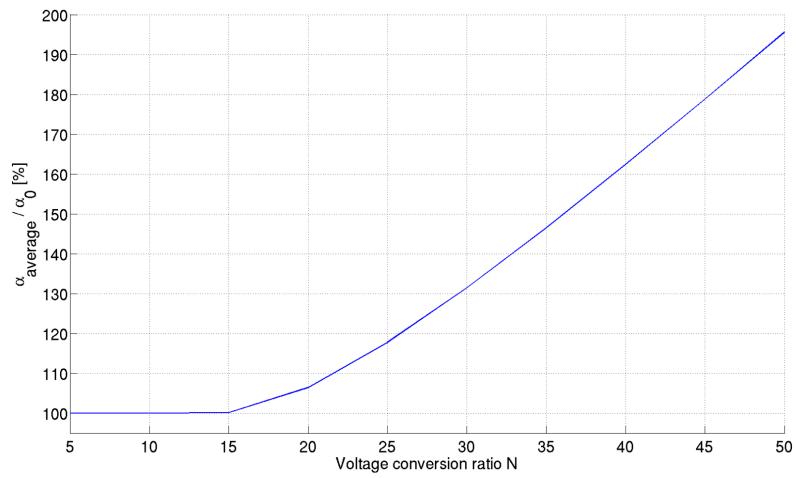

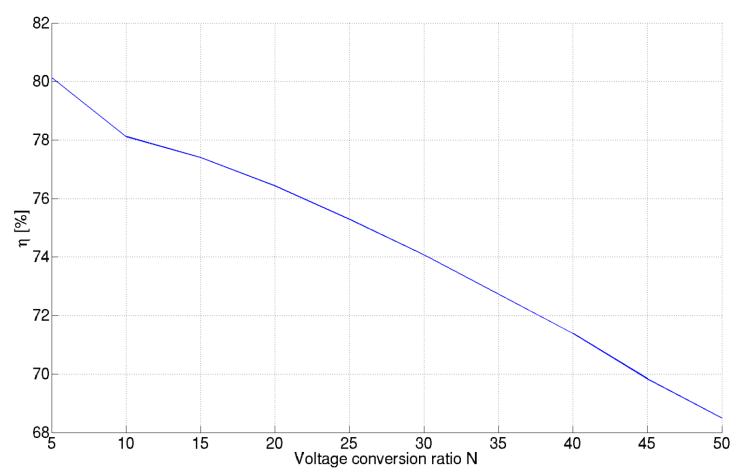

• Variable VCR;  $V_{out}=1.8$ ,  $\gamma=0.88$ ,  $f_{sw}=15MHz$ ,  $P_{out}=20mW$

# Inclusion of practical C<sub>fly</sub> voltage rating

• Variable VCR;  $V_{out}=1.8$ ,  $\gamma=0.88$ ,  $f_{sw}=15MHz$ ,  $P_{out}=20mW$

# Inclusion of practical C<sub>fly</sub> voltage rating

• Variable VCR;  $V_{out}=1.8$ ,  $\gamma=0.88$ ,  $f_{sw}=15MHz$ ,  $P_{out}=20mW$

#### **Overview**

Introduction & Motivation

Capacitive AC-DC Step-Down Approach

High Voltage Conversion Ratio DC-DC Approach

Conclusions

## High VCR topology conclusion

- M<sub>sw</sub> highly volatile over investigated topologies

- Dickson Star clearly differentiates and outperforms

- Highest possible capacitance utilization

- Lowest possible M<sub>sw</sub> metric (converges!)

Decreasing η drop with increasing VCR

- Good match for CMOS implementation

- Embedded D\* Cascade not better than D\*

- Even though it is a single stage conversion

#### **Conclusions**

#### High VCR AND Monolithic integration

- $-\,\alpha_{\text{par}}\,\text{and}\,\,V_{\text{Cpar,swing}}\,\,\text{have}\,\, \frac{\textit{large}}{\textit{large}}\,\,\text{impact on solution}$  space

- Dickson Star topology very promising:

- Converging f<sub>ac</sub>

- Converging M<sub>sw</sub>

- Large component count no issue

Thank you!

## **QUESTIONS?**