## POWER DELIVERY CHALLENGES FOR NEXT GENERATION HIGH PERFORMANCE SOCS

Stephen Kosonocky

**AMD Senior Fellow**

## AGENDA

High Performance APU Overview

- Voltage rail requirements

- IP components

- Fine grain power gating

- SVI2 interface

- Package Power Delivery Constraints

- Physical constraints

- Potential issues for integrated voltage regulator (IVR) solutions

- System AC Response

- Simplified power distribution model

- Variable frequency clocks

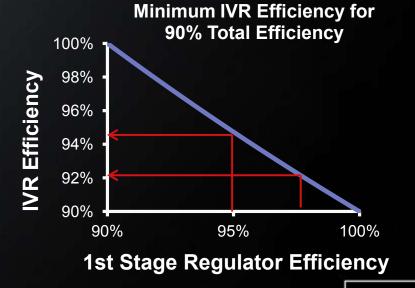

- Minimal IVR efficiency requirement

- Concluding remarks

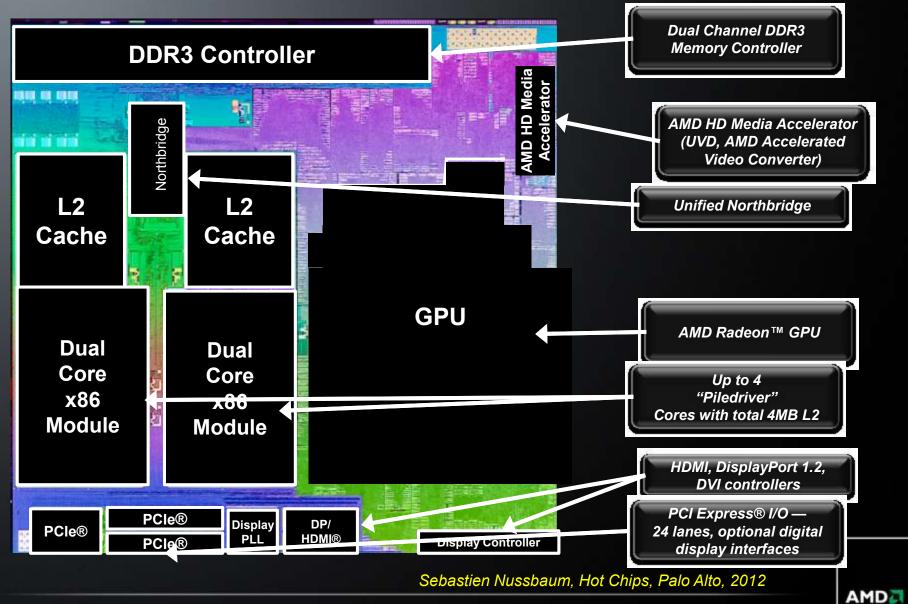

## HIGH PERFORMANCE APU "TRINITY"

- "Piledriver" Cores

- Quad CPU Core with total of 4MB L2

- Ind-Gen AMD Radeon™ with DirectX<sup>®</sup> 11 support

- 384 Radeon™ Cores 2.0

- HD Media Accelerator

- Accelerates and improves HD playback

- Accelerates media conversion

- Enhanced Display Support

- 3 Simultaneous DisplayPort 1.2 or HDMI/DVI links

- Up to 4 display heads with display multistreaming

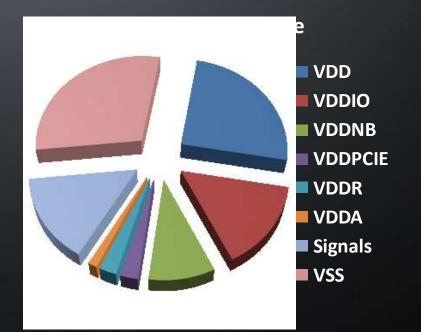

|       | Nominal<br>Voltage (V) | TDC (A) | Max Load<br>Step (A) |

|-------|------------------------|---------|----------------------|

| VDD   | Variable               | 50      | 42                   |

| VDDNB | Variable               | 29      | 37                   |

| VDDIO | 1.5                    | 3.2     | -                    |

| VDDR  | 1.2                    | 3.5     | -                    |

| VDDP  | 1.2                    | 4       | -                    |

| VDDA  | 2.5                    | 0.75    | -                    |

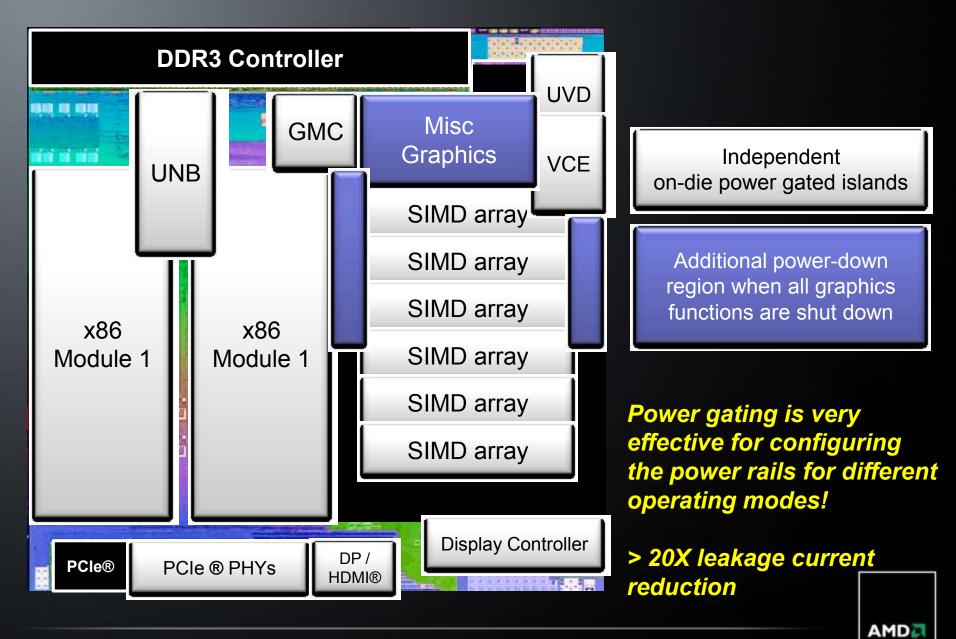

#### **"TRINITY" APU** 32nm SOI, 246mm2, 1.303BN TRANSISTORS

Multiple, mode configurable IP blocks Provides performance on demand

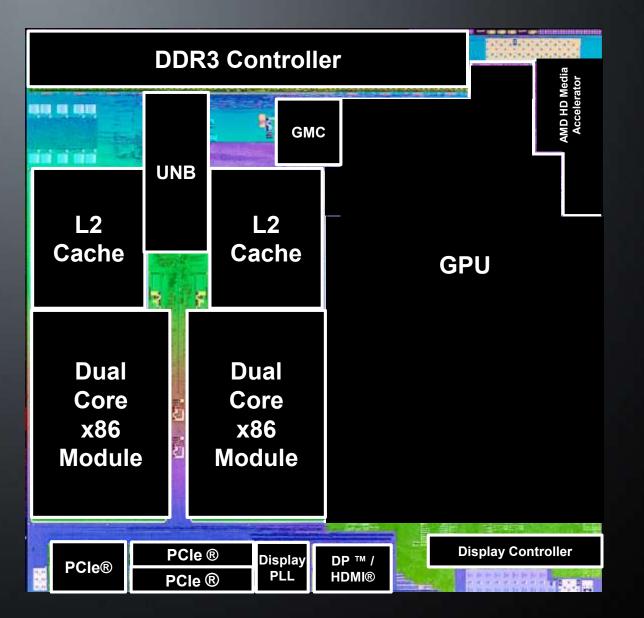

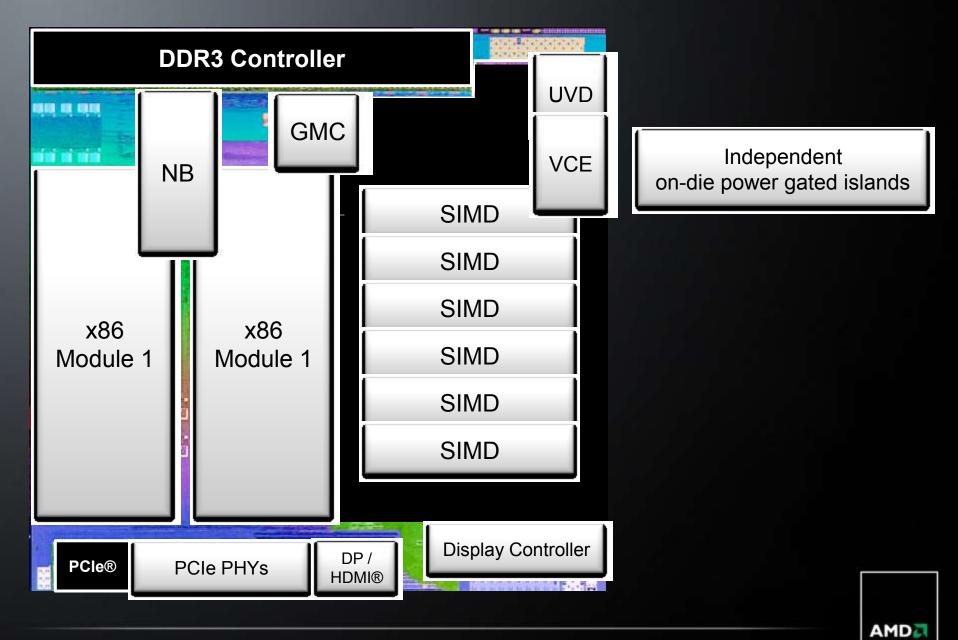

#### "TRINITY" APU FINE-GRAIN POWER GATING ISLANDS

## "TRINITY" FINE-GRAIN POWER GATING ISLANDS (2)

## "TRINITY" FINE-GRAIN POWER GATING ISLANDS (3)

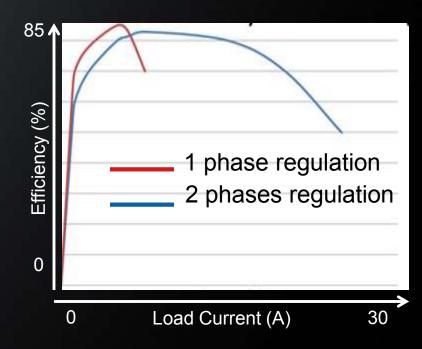

## PLATFORM POWER SAVINGS AMD SERIAL VOLTAGE INTERFACE 2.0 (SVI2)

- SVI is the interface which allows the system power management unit to communicate information to and from voltage regulator

- SVI2 enables quicker power state transitions

- Faster data transmission rates (33Mhz)

- Adds regulator response when transition is complete

- 80+% improvement in 500mV set point change latency over SVI1

- Power efficiency features

- Multiple Power State Indicators sent to regulator

- PSI0 Current low enough that regulator can shed phases

- PSI1 Current low enough that regulator can use pulse skipping / diode emulation

- Load Line trim, offset

- Ability to adjust DC offset and load line slope based on APU state

#### SVI2 provides a fast power management control path

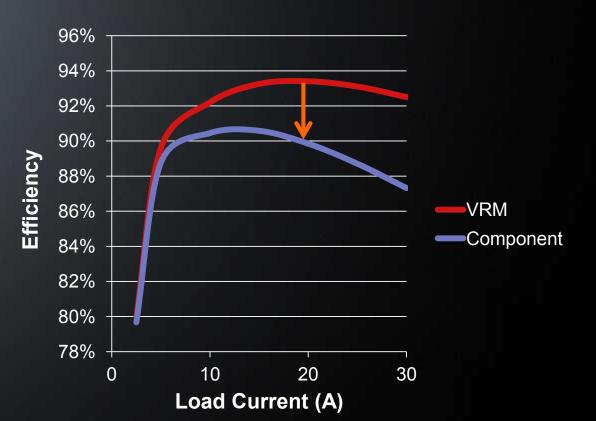

#### Regulator Efficiency vs. Load

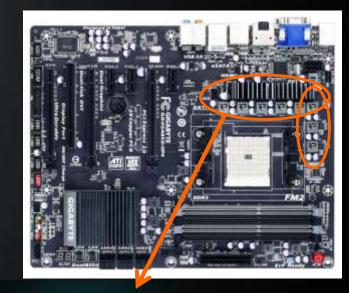

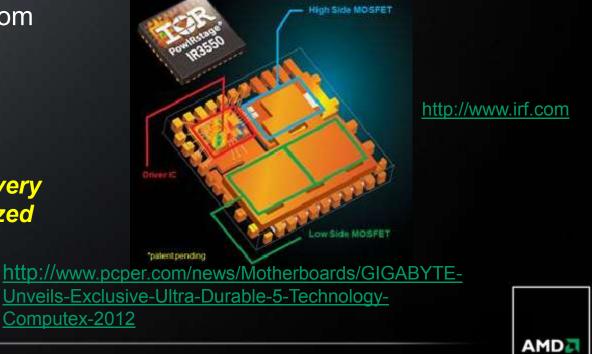

## CLIENT FM2 MOTHERBOARD

- Example Client configuration

- IR3550 "PowIRstage" ICs from International Rectifier

- 2X Copper PCB routes

- High current Ferrite Core Chokes rated up to 60A

- Minimal resistive losses from VRM to APU are possible

- Rs < 1mOhm typical (as seen in similar systems)

Today's system power delivery solutions are highly optimized for low loss and efficiency

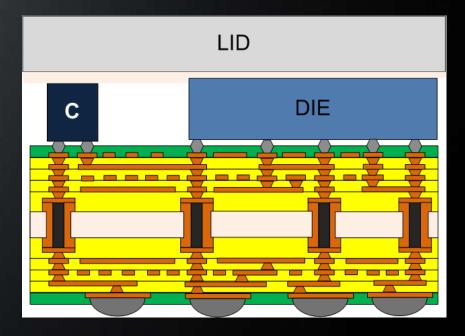

## TYPICAL PACKAGE CONSTRUCTION

- Package resources limitations

- Limited number of metal layers

- Competing resources

- z-height constraints

- Dielectric maximum voltage limits

Additional layers or size increase costs

#### Typical package cross-section

Package design is optimized for power delivery and signal integrity

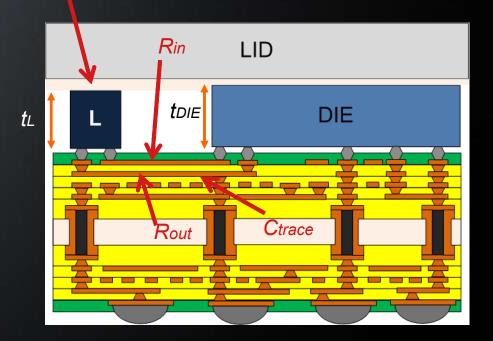

## PACKAGE LEVEL DISCRETE SURFACE MOUNT INDUCTOR

#### Not as simple as it sounds

- Thermal heating of inductor

- I<sup>2</sup>R heating in inductor can be significant

- Physical height should match die

- Variations can cause problems

- Can have poor thermal conduction to heat spreader

- Power loss of route

- I<sup>2</sup>R loss in package trace

- CV<sup>2</sup>f loss in package trace

- Skin effect loss at high Fsw

#### Thermal Conduction

# Integrated voltage regulation presents numerous challenges

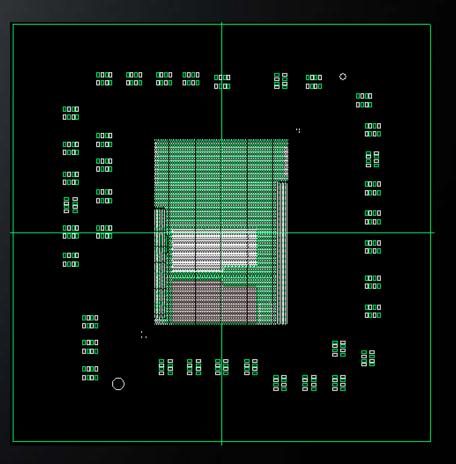

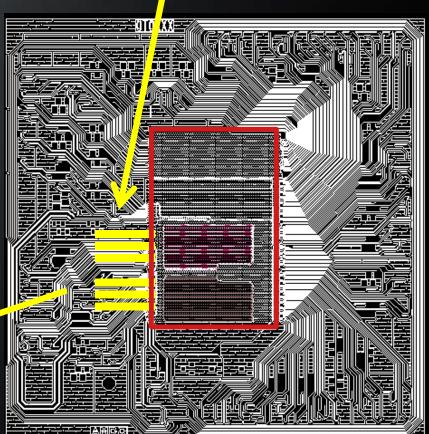

## PACKAGE SPACE CONSTRAINTS

- Limited number of locations available for passive components

- Keep-out regions add further limitations

- Back-side cavity locations can provide some relief

- At the cost of inductive connections

- Multi-chip packages

- Additional cost and complexity

- Possible IVR components

- Controller IC

- Power FETs

- Inductors

- Capacitors

Physical package size is a major constraint for an integrated voltage regulator solution

AMD

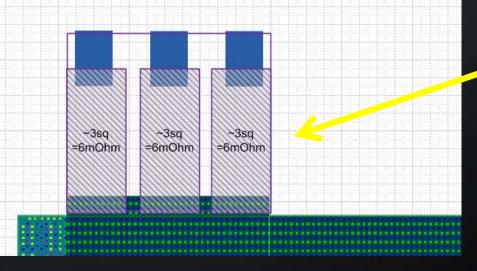

## **IVR ROUTING CONSTRAINTS**

- Top level metal already very congested with I/O routing

- New chip floorplans are required to optimize connections to discrete components

- Package routes still have significant resistance

- Resistance in the single digit mOhm range for reasonable metal usage

#### Potential routes to discrete inductors

An IVR solution must compete with signal routes and external supplies

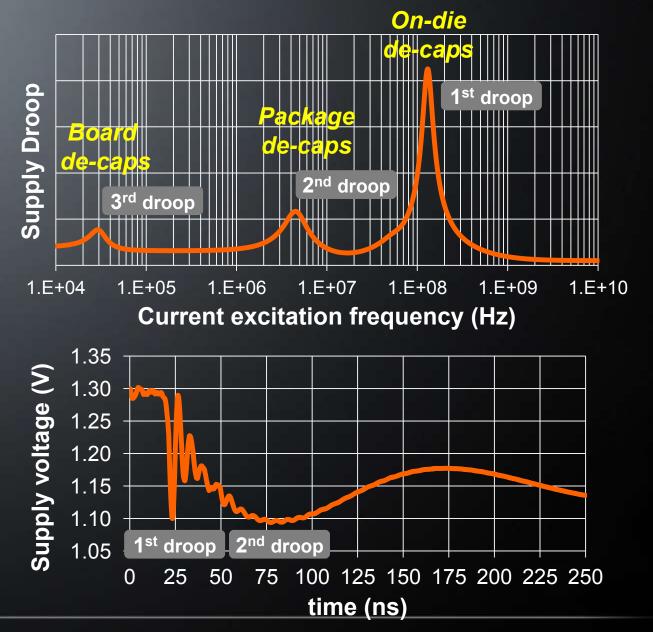

#### TYPICAL FREQUENCY AND TRANSIENT STEP RESPONSE

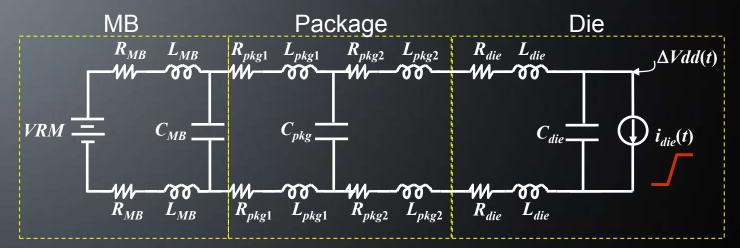

## TYPICAL MICROPROCESSOR POWER DELIVERY NETWORK

#### Simplified power distribution lumped model

- Different resonance frequencies (100s of MHz KHz)

- Sudden changes in load  $(i_{die}(t))$  cause undershoot/overshoot in supply

- De-cap added at different levels to suppress this supply noise

- On-die de-cap typically < 100nF per voltage rail</p>

- Not enough to satisfy the demands of a high performance processor

- Significantly more will require expensive MIM cap technology

- IVR designs will require large filter capacitance

- Package mounted capacitors would have similar ESL as today's VRM based designs

Transient response to noise would be very similar between an IVR and non-IVR solution

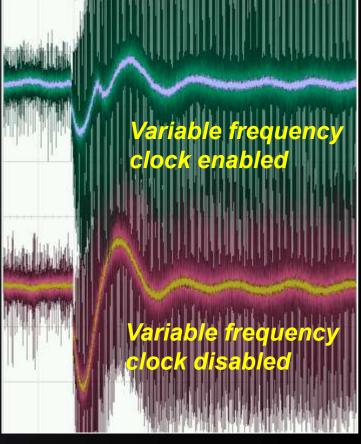

#### NON-IVR SOLUTIONS FOR DI/DT NOISE

- 1<sup>st</sup> droop occurs very fast

- ~5ns from onset of current step

- Caused by the depletion of the low ESL on-die decoupling capacitance

- Variable frequency clocks can provide high speed adaptation to di/dt events at low cost

- VFCG PLL dynamically reduces the CPU clock when supply goes below a threshold

- > 5% performance increase for same power supply

- > 10% power saving at same performance level

#### Techniques like variable frequency clocks can reduce the need for very high speed regulator response

Alain Artieri: "Embedded Multicore in Mobile Platforms", presented at the Power/Performance Optimization of Many-core Processor SoCs, ISSCC Forum, San Francisco, Feb 2012.

#### SINGLE PHASE POWER DELIVERY EXAMPLE

- Today's VRM efficiencies can be very high

- Does not include PWM controller power

- High quality power components

- Low DCR inductor

- Low loss PCB routes

- Switching Frequencies

- 200KHz 1MHz

- Losses to board component

- I<sup>2</sup>R DCR loss

- I<sup>2</sup>R PCB route loss

- Multiple phases can further reduce losses

+90% Efficiency across wide load range typical today

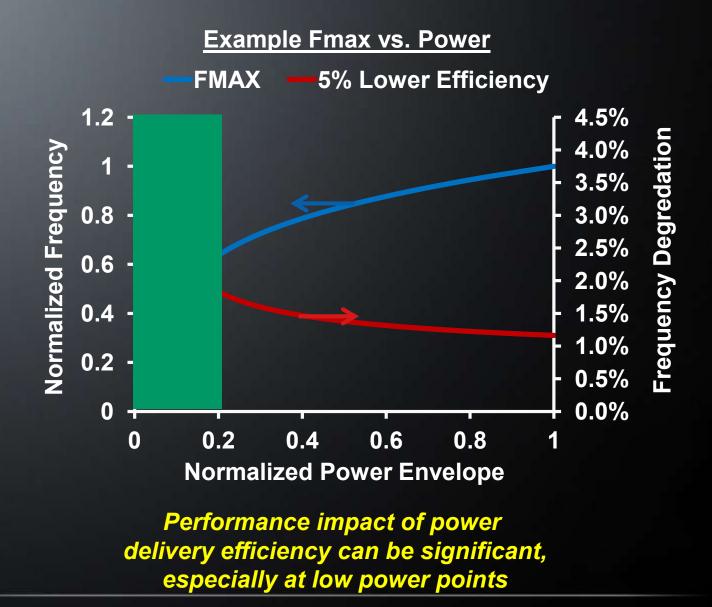

#### SYSTEM CONSTRAINED POWER SENSITIVITY TO VRM POWER EFFICIENCY

AMD

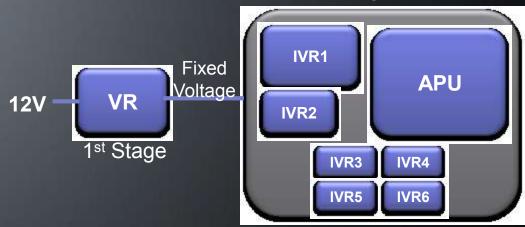

## HIGH CURRENT IVR REQUIREMENT

#### **Potential IVR based system**

#### Break Even Requirement

- Assume Today's VRM Efficiency > 90%

- 1<sup>st</sup> stage regulation efficiency needs to be very high to avoid excessive loss

- Need enough package space to support components for all rails

- +2 High current rails, +4 low current rails

- Difficult to accommodate many high current multi-phase designs

#### **CONCLUDING REMARKS**

- High performance SOC's are integrating more and more IP blocks

- Additional voltage rails will open up more possibilities for advanced power management

- Fine grain power gating has proven to be an effective solution for powering down unused IP blocks

- IVR solutions must compete with computational sprinting techniques

- SVI2 provides fast power state transitions and power management control

- Phase shedding

- Pulse skipping

- Load line trimming

- State-of-the-art external VRMs and good board design can provide a high efficiency power delivery solution

- Present solutions set a very high bar, integrated solutions need a high ROI

- Package constraints limit number and placement of discrete components on package

- We don't have unlimited space

- Variable frequency clocks can provide a low cost solution to *di/dt* droops

- High speed regulator response is not a large motivation

## CONCLUDING REMARKS (CONTINUED)

The three most important criteria for an integrated voltage regulator solution:

- 1. Efficiency

- 2. Efficiency

- 3. Efficiency

- At low cost

#### **DISCLAIMER & ATTRIBUTION**

The information presented in this document is for informational purposes only and may contain technical inaccuracies, omissions and typographical errors.

The information contained herein is subject to change and may be rendered inaccurate for many reasons, including but not limited to product and roadmap changes, component and motherboard version changes, new model and/or product releases, product differences between differing manufacturers, software changes, BIOS flashes, firmware upgrades, or the like. There is no obligation to update or otherwise correct or revise this information. However, we reserve the right to revise this information and to make changes from time to time to the content hereof without obligation to notify any person of such revisions or changes.

NO REPRESENTATIONS OR WARRANTIES ARE MADE WITH RESPECT TO THE CONTENTS HEREOF AND NO RESPONSIBILITY IS ASSUMED FOR ANY INACCURACIES, ERRORS OR OMISSIONS THAT MAY APPEAR IN THIS INFORMATION.

ALL IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE ARE EXPRESSLY DISCLAIMED. IN NO EVENT WILL ANY LIABILITY TO ANY PERSON BE INCURRED FOR ANY DIRECT, INDIRECT, SPECIAL OR OTHER CONSEQUENTIAL DAMAGES ARISING FROM THE USE OF ANY INFORMATION CONTAINED HEREIN, EVEN IF EXPRESSLY ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

AMD, the AMD arrow logo and combinations thereof are trademarks of Advanced Micro Devices, Inc. All other names used in this presentation are for informational purposes only and may be trademarks of their respective owners.

AMD, the AMD Arrow logo and combinations thereof are trademarks of Advanced Micro Devices, Inc. in the United States and/or other jurisdictions. Other names used in this presentation are for identification purposes only and may be trademarks of their respective owners.

AMD

© 2012 Advanced Micro Devices, Inc. All rights reserved.