# ipdia

### **The 3D Silicon Leader**

High Density Silicon based Capacitors for Power Electronics System Integration

> Powersoc ,November 2012 Catherine Bunel

#### Outline

- Introduction

- 3D Silicon Capacitor density roadmap

- A new worldwide record of capacitor density

- High voltage capacitors

- Examples of applications

- Conclusion

#### Introduction

#### Who are we?

- Independent Company located in Caen, Normandy, France

- Dedicated to manufacturing of leading edge Integrated Passive Devices

- 20 M\$ revenues, 100 people and operating own Silicon wafer fab

- Strong R&D team and collaborations with leading research institutes

#### What do we do?

High performance, high stability and high reliability silicon passive components to customers in communication, harsh environment, industrial, lighting, and medical markets.

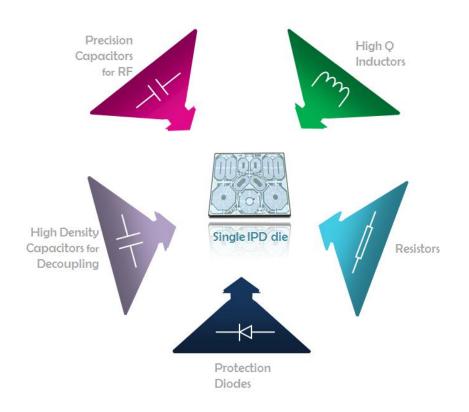

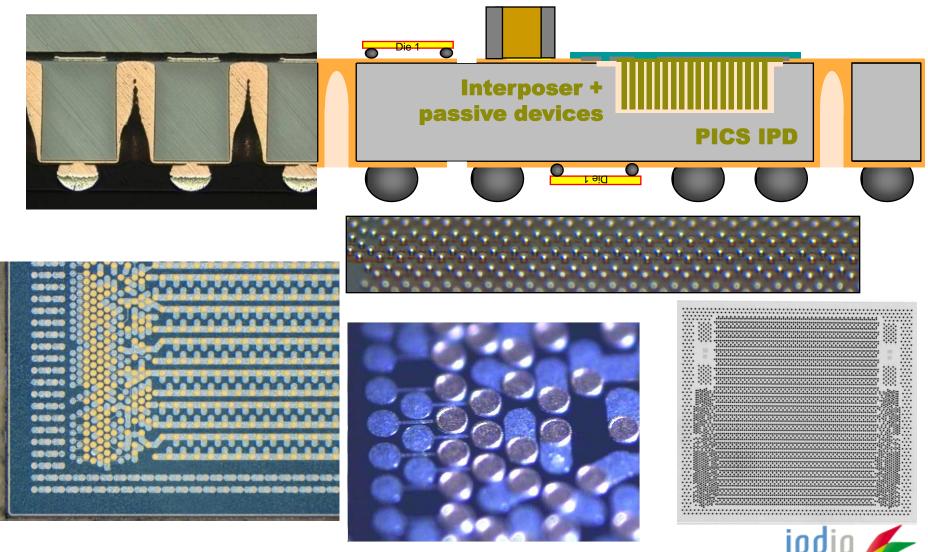

#### **PICS-IPD**, a Unique Technology

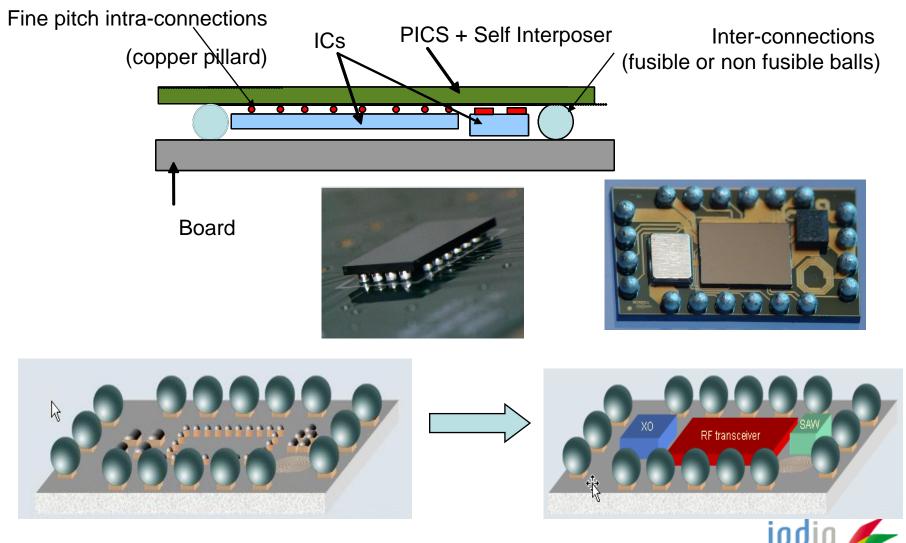

#### Passive Integration Connecting Substrate

Up to 100's of passive components can be integrated

Value proposition is: •Size •Cost •Performance

#### IPDIA value proposition: Technology that enables

#### Miniaturization of application

- Module: High density integration

- High PCB area saving (e.g. > 40%)

- Silicon die with embedded passives as replacement of external SMD components

- Compatible with standard wire bonding or reflow assembly according to scenarios

#### Reduced Cost

- BOM level

- Simpler manufacturing with module

- Simpler application with less components to place

#### Enhanced Performance

- Very high stability vs temperature,

-55°C to +210(\*)°C operating range

- High stability vs voltage, time...

- High reliability (no cracking & very low failure rate<2ppm)</li>

- Efficient decoupling with low ESR/ESL by full integration on silicon

- Lower battery life time with very low leakage current

- PCB influence cancelled

#### **Greater Flexibility**

- One configurable IPD allowing a set of output voltages

- (\*): limited by the active part, up to 250°C is possible with our passive integration

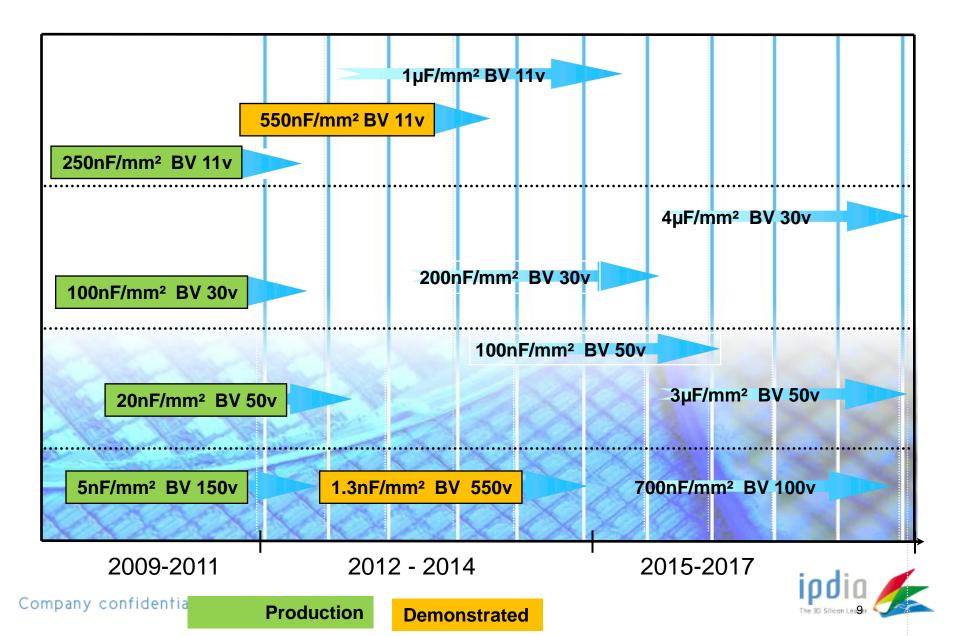

#### 3D CAPACITOR DENSITY ROADMAP

#### **3D Capacitor Density Roadmap**

#### PICS4=550nF/mm<sup>2</sup> A NEW WORLDWIDE RECORD

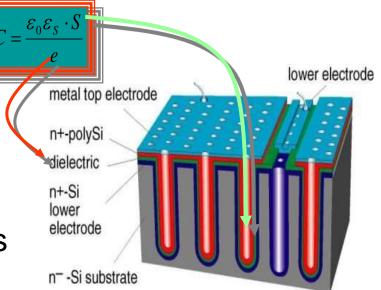

#### Key features for highly integrated Capacitors

- Increase the effective capacitor c surface by etching 3D structures with high aspect ratio.

- Suitable high k material with appropriate deposition techniques

- High permittivity

- High breakdown voltage > 10V

- Low leakage current <1nA/µF</li>

- Excellent temperature and voltage linearity < 100ppm/°K & < 100ppm/V</li>

- Failure in Time < 1</li>

27/11/2012

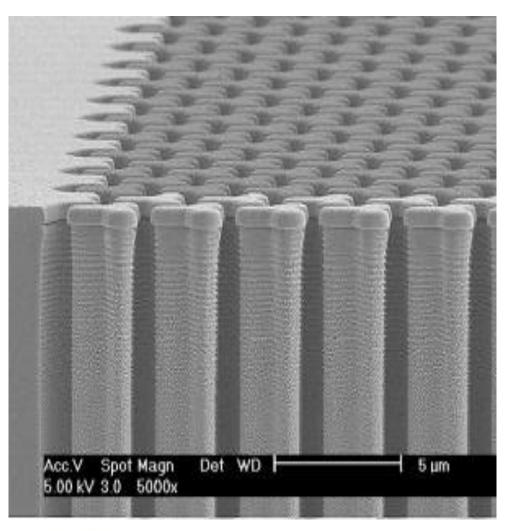

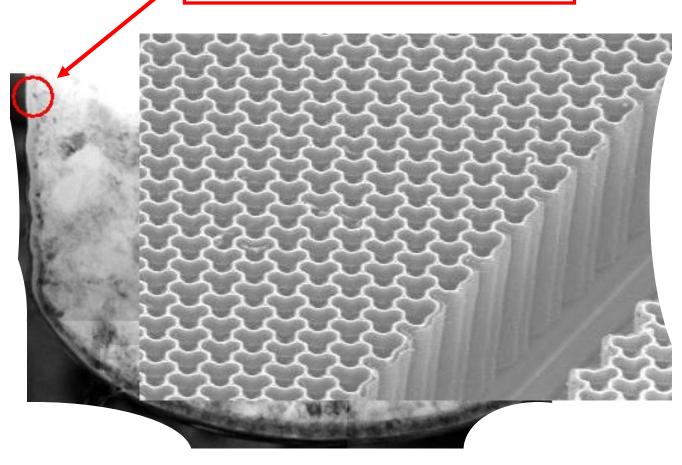

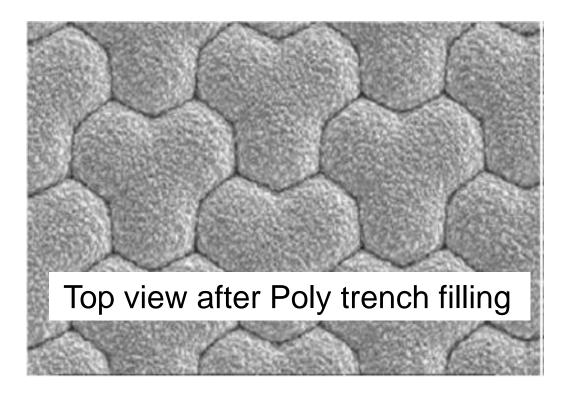

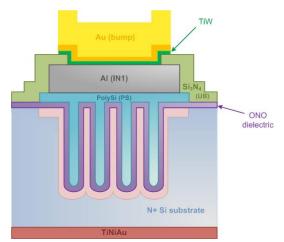

#### **Key features for highly integrated capacitors :The deep Silicon etching**

**Tripod shape**

with Aspect Ratio up to 60

Company confidential

27/11/2012

12

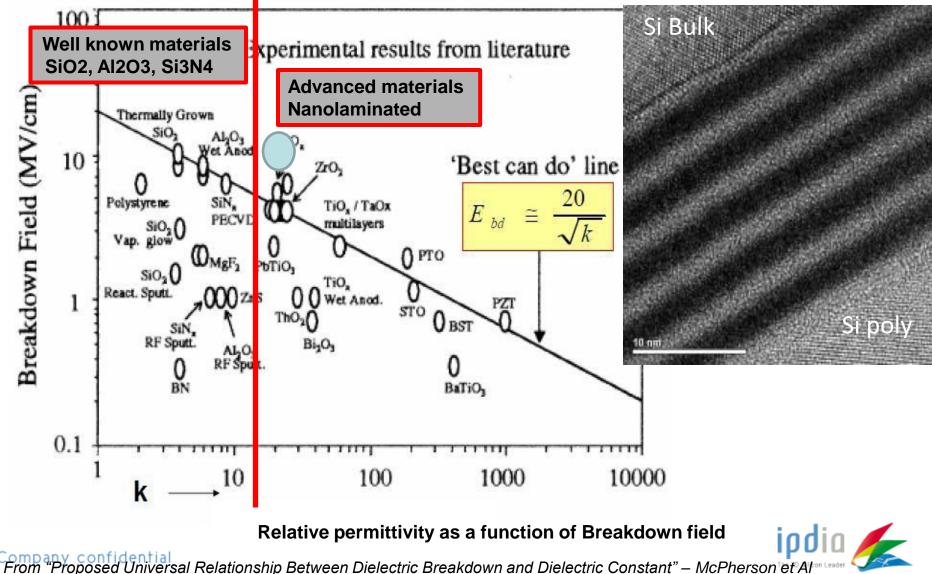

#### **Key features for highly integrated** capacitors : The dielectric

#### **Key features for highly integrated capacitors : The dielectric deposition**

Step coverage is key !

#### **Key features for highly integrated capacitors :**

## The trenches filling and the thermal budget seen by the 3D structures

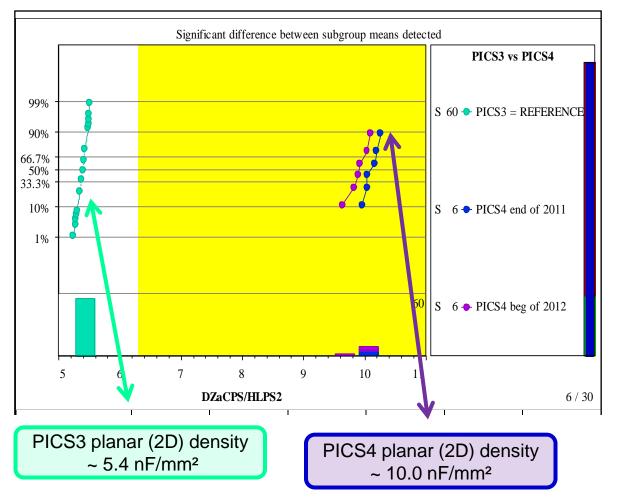

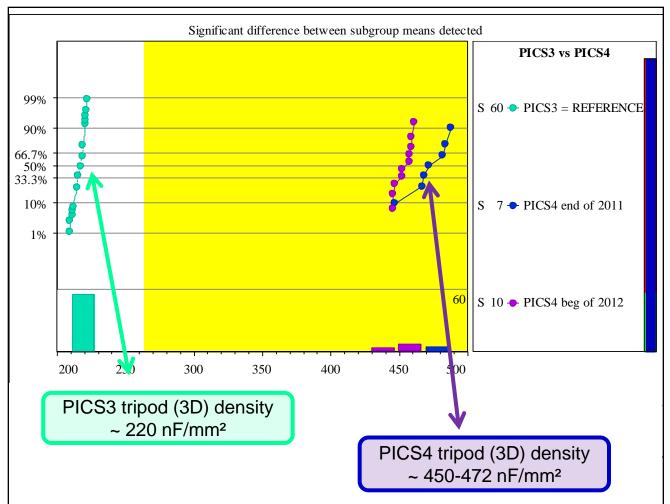

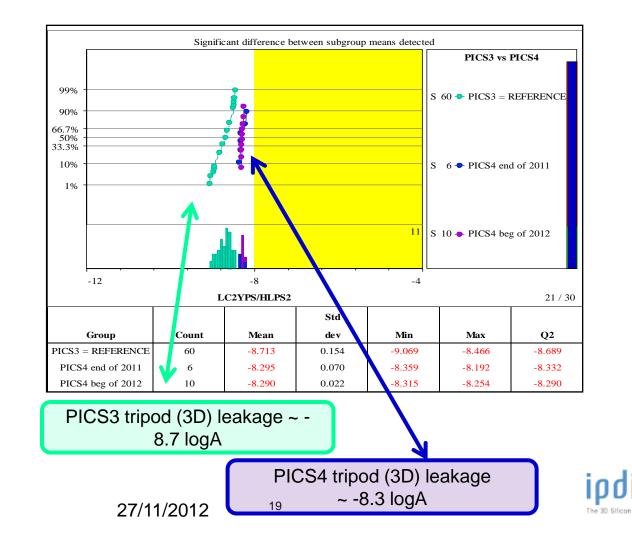

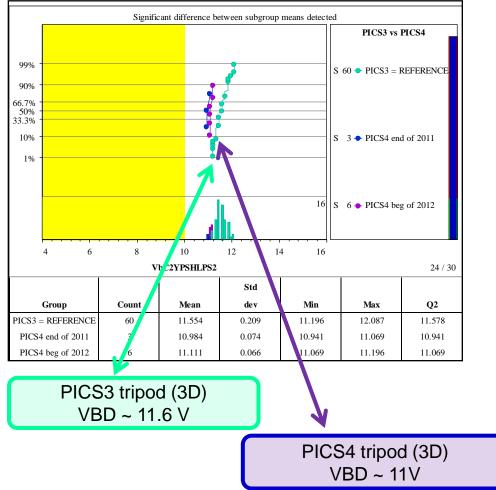

- Batches were characterized at PCM level (Process Control Modules)

- Investigated parameters are those corresponding to leakage through the dielectric, capacitance density and also breakdown voltage for both 2D and 3D capacitors

- Results were obtained from Keithley (raw PCM results).

- Two sets of measurements

### 2D capacitor densities of the PICS4 wafers compared to a PICS3 reference batch :

Company confide

### 3D capacitor densities of the PICS4 wafers compared to a PICS3 reference batch :

Company conf

### 3D capacitor leakage of the PICS4 wafers compared to a PICS3 reference batch :

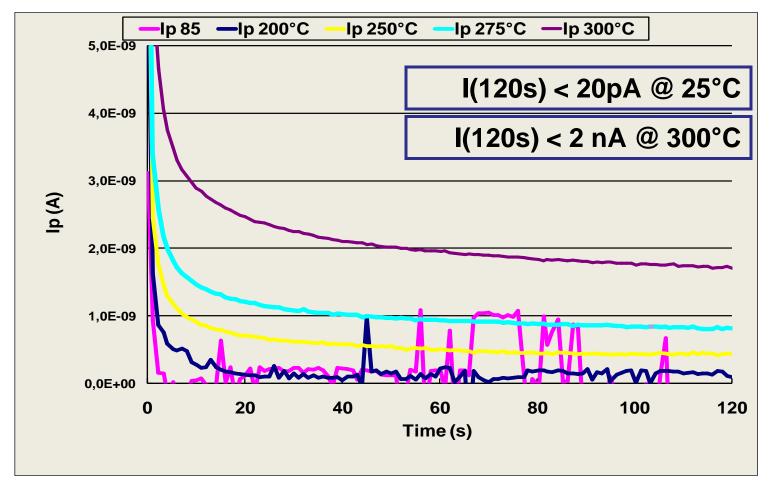

#### **DC leakage current** at high Temperature C= 100nF (Amps @ 3V)

### 3D (CAPY) capacitor V<sub>BD</sub> of the PICS4 wafers compared to a PICS3 reference batch :

- Capacitance density calculation at PCM level is impacted by the area required to connect to the electrodes.

- As a consequence, PCM densities are lower than the density measured on the products.

- The real capacitance densities are the following :

- 2D = 11.40nF/mm<sup>2</sup> in PICS4 (6.15nF/mm<sup>2</sup> in PICS3 on the ref batch)

- $3D = 542.44nF/mm^2$  in PICS4 (243.96nF/mm<sup>2</sup> in PICS3 on the ref batch)

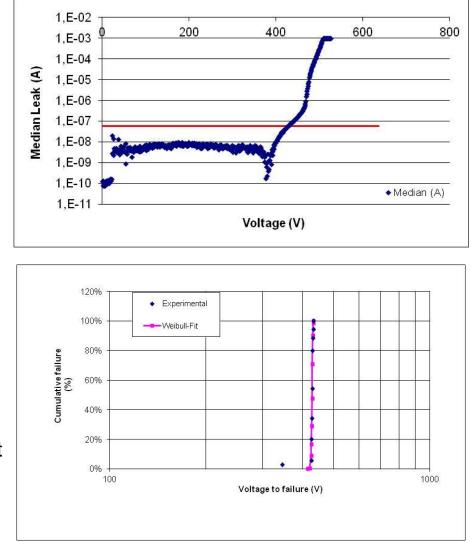

#### PICS High Voltage

#### **PICS High Voltage**

Larger pores to introduce a thicker dielectric Deeper pores to keep high capacitance density

C=1.35nF/mm<sup>2</sup>

Vuse = 421 V (0.1% cumulative failure) at room temperature

#### **Examples of application**

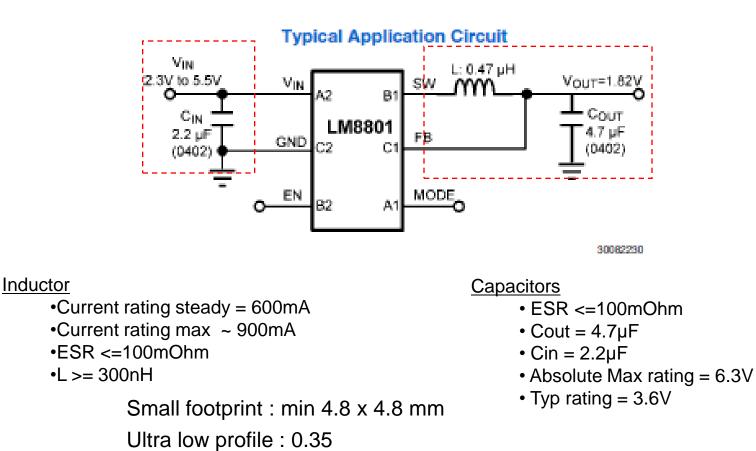

#### **DCDC converter** LM8801 overview\*

\* Courtesy NationalSemi. see application brochure for details

Several assembly options : WLCSP or FlipChip

#### **Integration capabilities with PICS**

#### **Through Silicon Vias**

### Conclusion

#### Conclusion

IPDIA 3D Silicon Capacitor is offering many advantages :

- ✓ High capability of integration, low profile

- ✓ Very high stability with an outstanding behaviour at 250°C

- ✓ Extremely low failure rate .No burn-in test .

- ✓ Ultra Low leakage.

- ✓ High quality manufacturing process

- ✓ High flexibility

Coming soon : higher integration in the power system management thanks to higher Capacitor density !