International Workshop on Power Supply on Chip (PwrSoC) 2023

# Next-Generation Switched-Capacitor Converters using High-Density on-die MIM Capacitors

Nicolas Butzen Research Scientist – Intel Labs

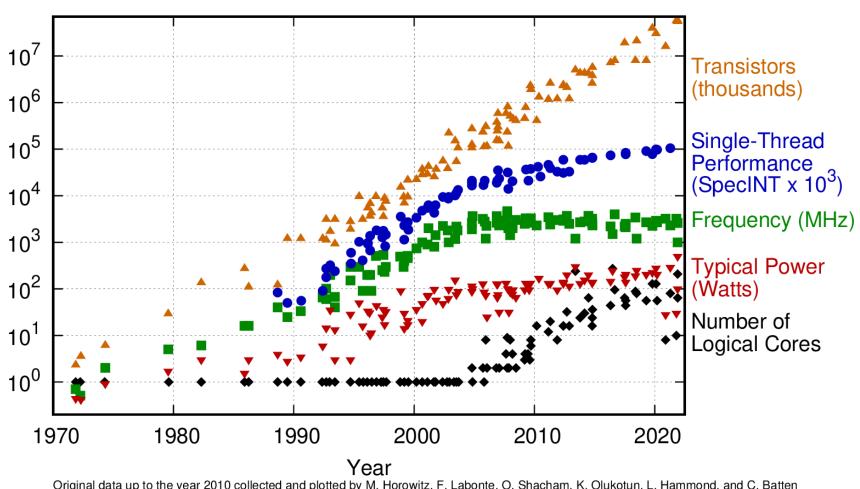

### Moore's Law

50 Years of Microprocessor Trend Data

Original data up to the year 2010 collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, and C. Batten New plot and data collected for 2010-2021 by K. Rupp

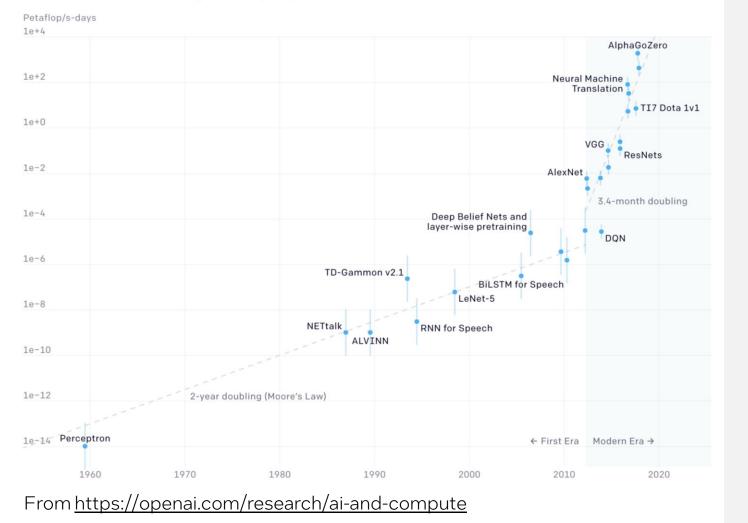

# Compute Trends

- Al compute requirements have been increasing faster than Moore's Law

- Large Language Models Gold Rush

#### Two Distinct Eras of Compute Usage in Training AI Systems

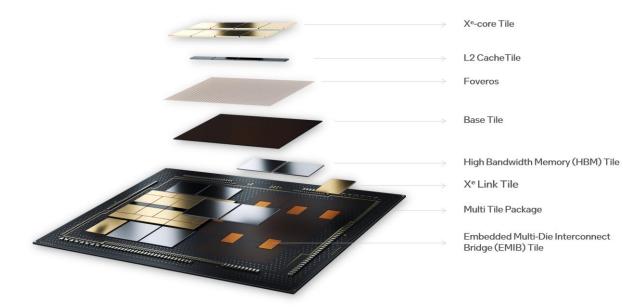

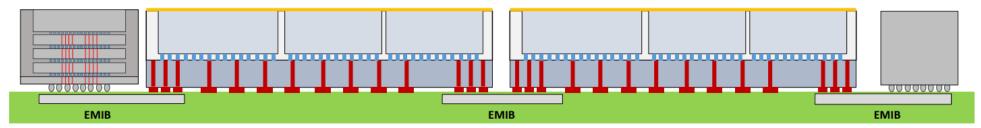

# Semiconductor Trends

- Increase in compute density

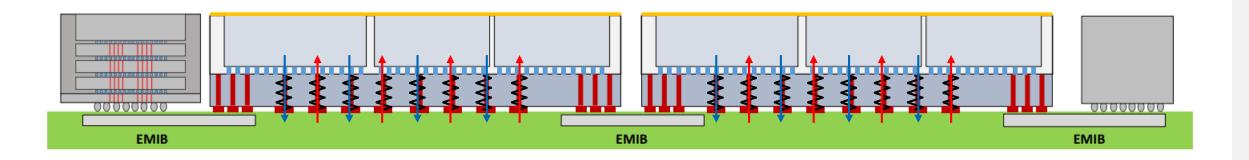

- On-package High-Bandwidth Memory (HBM)

- 2.5D and 3D Advanced Packaging

- Several process technologies

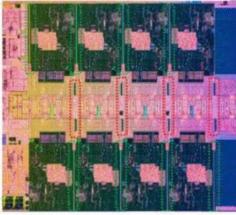

Intel Data Center GPU MAX Ponte Vecchio

4

# Impact on Power Delivery

A lot of current!

- Increase in package TDP

- Reduction of compute voltage levels

- Increase in number of power domains

- Increased input/output parasitic impedances

→ Need for ultra-small, high-current, high-efficiency, voltage regulators

# Integrated Voltage Regulators

#### Linear Regulator

From M. Zelikson ISSCC2023

- + Small, can be close to load

- + Maintains efficiency vs lout

- No Transformer effect

- Sensitive to input impedance

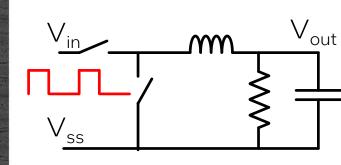

#### Inductive Buck

From <u>C. Schaef ISSCC2022</u>

- + Good Efficiency vs VCR

- + Transformer effect

- Inductors are <u>*Large*</u>, don't scale to small sizes

6

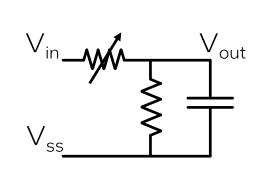

- Footprint heavily relies on Capacitor Density

+ Good efficiency across lout and VCR\*

#### + Transformer effect

# out $V_{ss}$

Integrated Voltage Regulators

+ Small volume, can be integrated monolithically; co-located with load

Switched-Capacitor VR

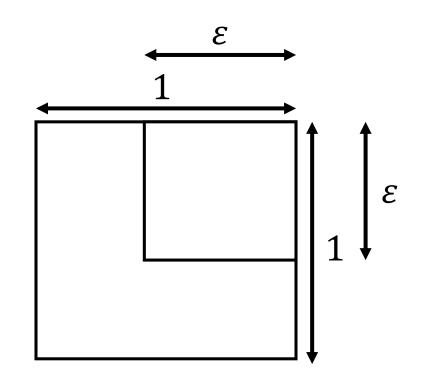

### Monolithic VRs

SCVRs get better as they get smaller

- Capacitors:  $C \sim \varepsilon^2$

- Transistors:  $G \sim \varepsilon^2$

- Interconnects:  $R \sim 1$

→ Inherent VR losses\*: P~1 →Normalized interconnect losses\*: P~ $\epsilon^2$

\*Normalized to output power, iso-power-density.

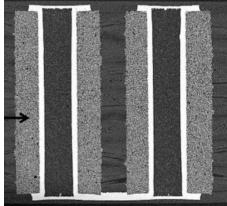

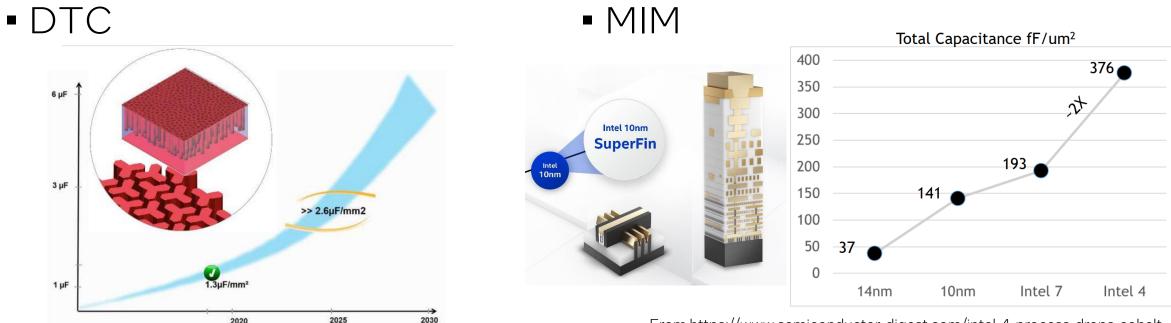

# On-die Capacitor Technologies

From Shunsuke ABE, PowerSoC 2021

- Can not co-exist with transistors

- Shift towards passive interposer/chiplet implementations

From <u>https://www.semiconductor-digest.com/intel-4-process-drops-cobalt-interconnect-goes-with-tried-and-tested-copper-with-cobalt-liner-cap/</u>

- Lower density

- Can be on top of powerfets / load domain

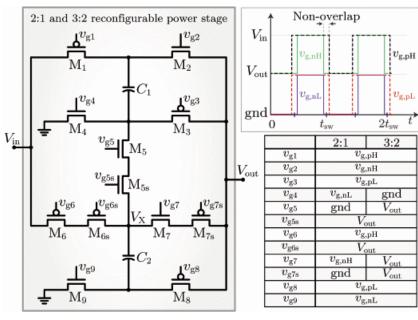

#### Switched-Capacitor Topologies

- 'Conventional' Fixed-ratio

- + Excellent peak-efficiency near ideal Voltage Conversion Ratio

- Bad 'Regulation' efficiency

From <u>T. Andersen, ISSCC 2014</u>

From <u>T. Andersen, ISSCC 2014</u>

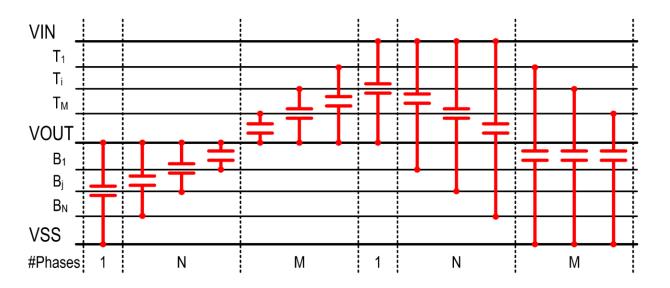

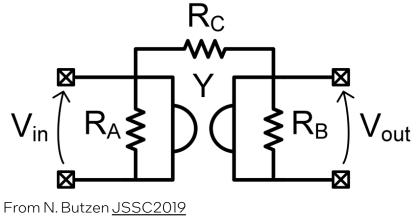

# Switched-Capacitor Topologies

Continuously-Scalable Conversion Ratio (CSCR)

- + Efficient operation vs VCR

- + Output current proportional to Vin

- Requires larger transistor footprint

- Scaling towards higher input voltages

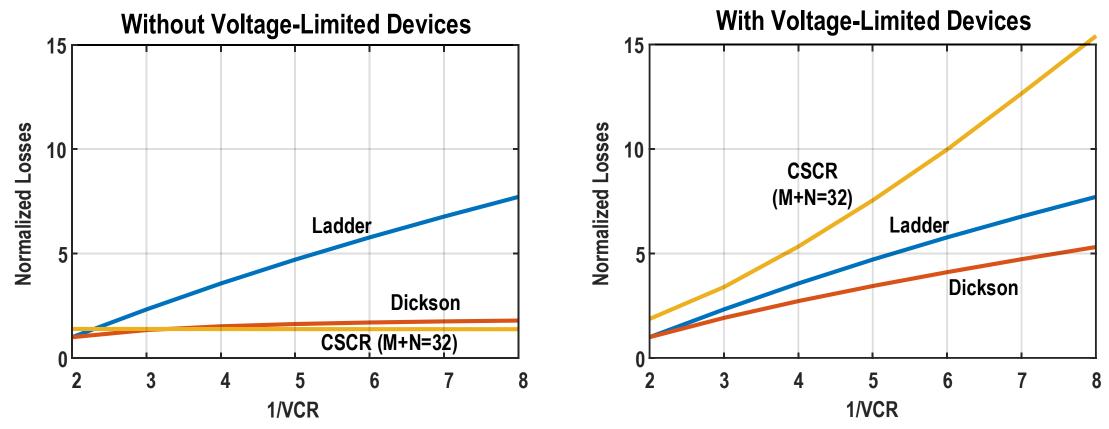

# **Theoretical Comparison**

$\rightarrow$  CSCR SCVR has excellent performance at lower Vins

$\rightarrow$  Fixed-Ratio is better at higher Vins (relative to process technology)

Efficiency • *BUT* .... **Conversion Ratio** VOUT VIN  $I_{LOAD} \sim \Delta V$ **Fixed-Ratio**  $\rightarrow$ Can never run in **SCVR** 'optimal' point\* VSS VOUT VIN  $I_{LOAD} \sim V_{in}$ **CSCR**  $\rightarrow$  Much less sensitive to input variation

# Comparison fixed-ratio to CSCR

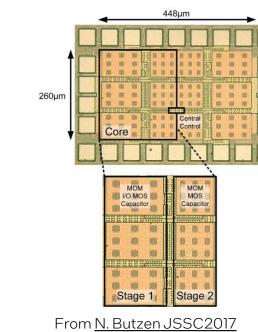

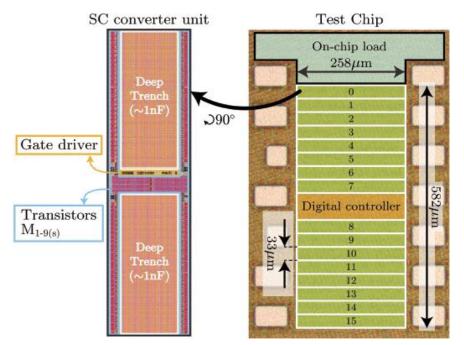

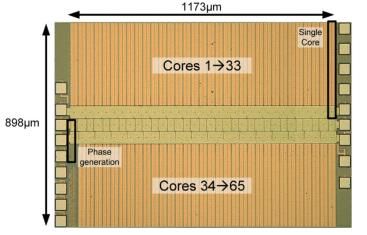

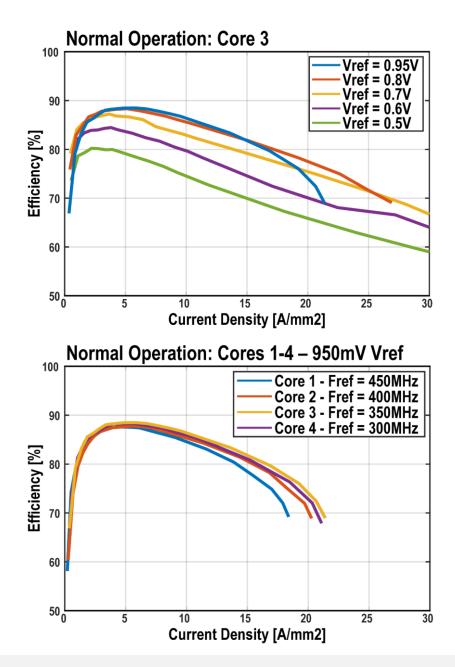

Case Study 1: On-die CSCR SCVR

From N. Butzen, et al. ISSCC2023

- 1.3∨ → 0.5-0.95∨

- MIM capacitors overhanging load domain

- 4 Independently controlled VR Cores

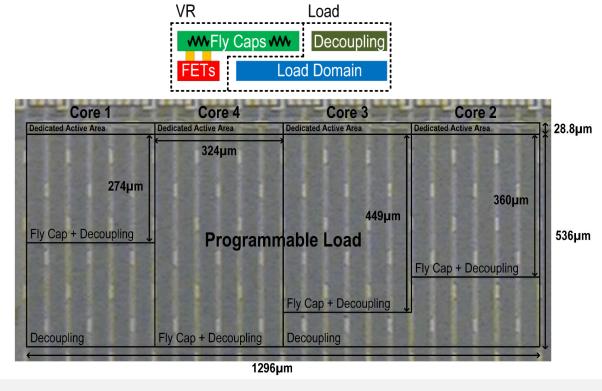

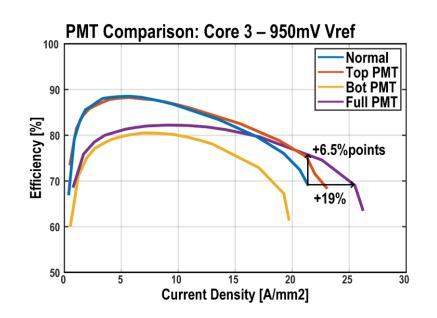

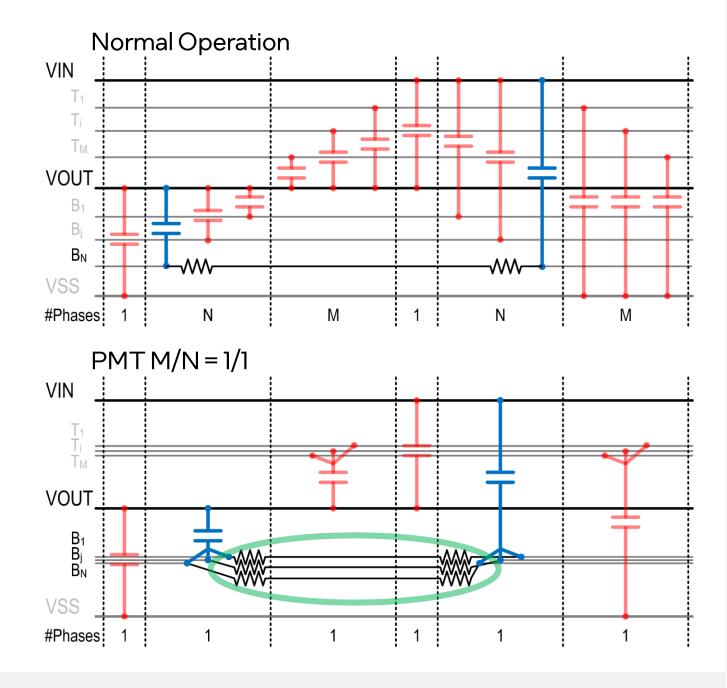

Phase-Merging Turbo

From N. Butzen, et al. ISSCC2023

- Reconfigure M/N

In the Configure figure

- $I_{LOAD} \approx V_{in}C_{fly} \frac{f_{phase}}{2(1+N+M)}$ ,  $I_{MAX} \sim \frac{1}{R_{path}}$

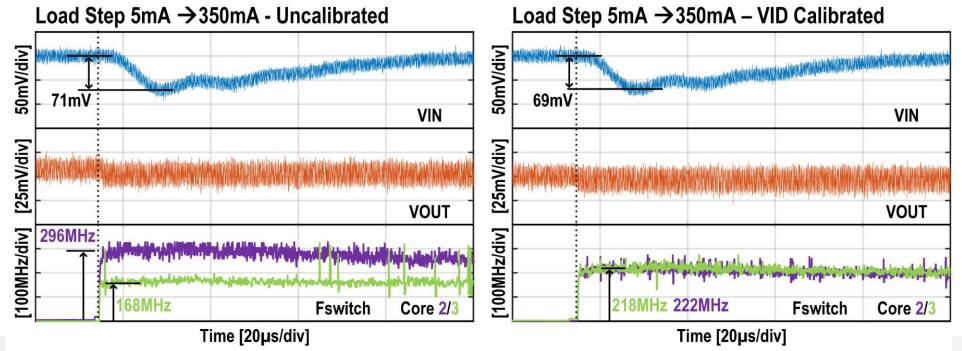

# **Communication-less Ganging**

From N. Butzen, et al. ISSCC2023

- CSCR SCVRs current range is [0, Imax] (frequency limited)

- No danger of VR cores sinking/sourcing at the same time

- No danger of runaway current event

- Lower-bound hysteretic controller

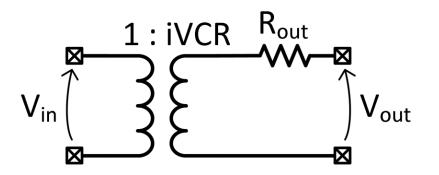

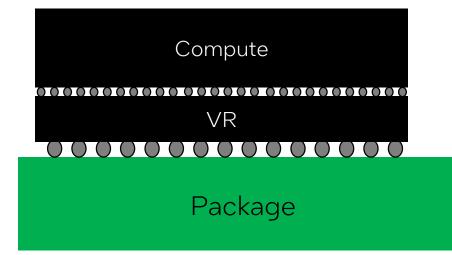

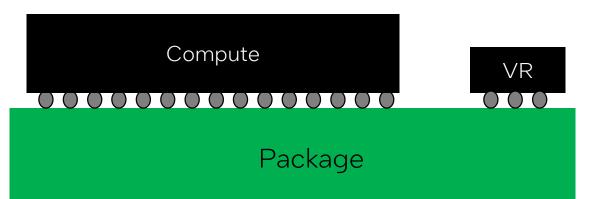

# Case Study 2 : High Voltage VR Chiplet

- Disaggregated VR

- Reintegrated using 2.5D or traditional packaging

- Cheap process, fine-tuned for VR

- → Better performance/cost

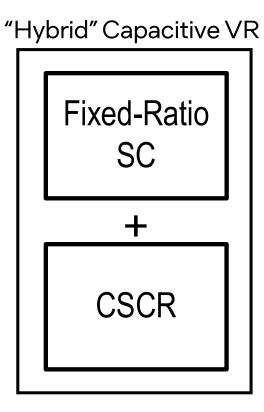

# Case Study 2 : High Voltage VR Chiplet

- How to get to higher input voltages?

- $\rightarrow$ Combine fixed-ratio and CSCR elements

- + CSCR can remain low-voltage and do regulation

+ Fixed-ratio converters can be in 'optimal' point

+ ....

Up to 3V input, >10W/mm<sup>2</sup>, >90% Peak-Efficiency, Fully Monolithic, CSCR behavior

- Compute demands and Advanced Packaging will continue to strain power delivery systems into the Future

- Monolithic Switched-Capacitor Converters offer the highestperformance with respect to volume

- Recent advancements in on-die MIM are boon for SCVRs

- Continuously Scalable Conversion-Ratio topologies offer excellent theoretical and practical performance.

- Demonstrating >88% efficiency and high output power

# Acknowledgements

Harish Krishnamurthy, Jingshu Yu, Zakir Ahmed, Sheldon Weng, Krishnan Ravichandran, James Tschanz, Michael Zelikson, Ramez Hosseinian Ahangharnejhad, James Waldemer, Chris Pelto, Jonathan Douglas