2021 PwrSoC – Integrated Magnetics

## Magnetic Inductors for Next Generation IVR

Kaladhar Radhakrishnan

Intel Fellow, Technology Development

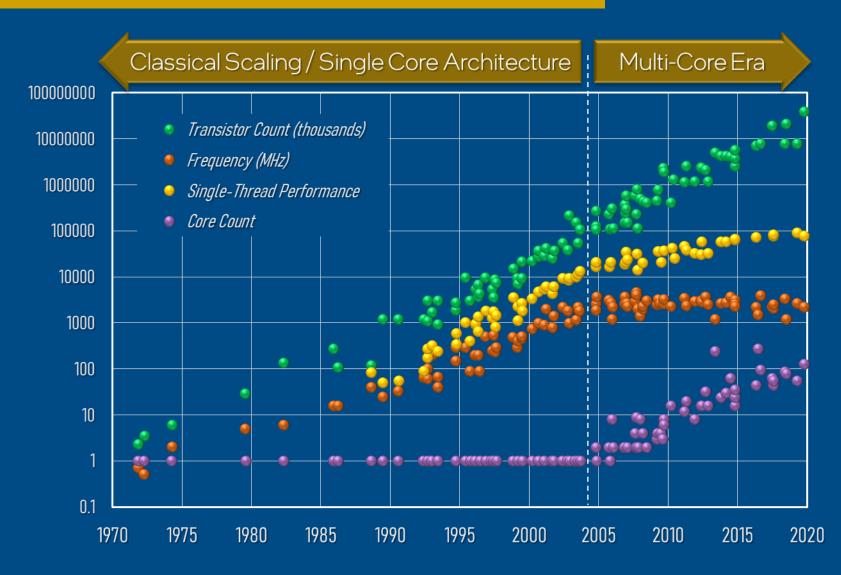

## Semiconductor Industry Trends

https://www.karlrupp.net/2018/02/42 -years-of-microprocessor-trend-data/

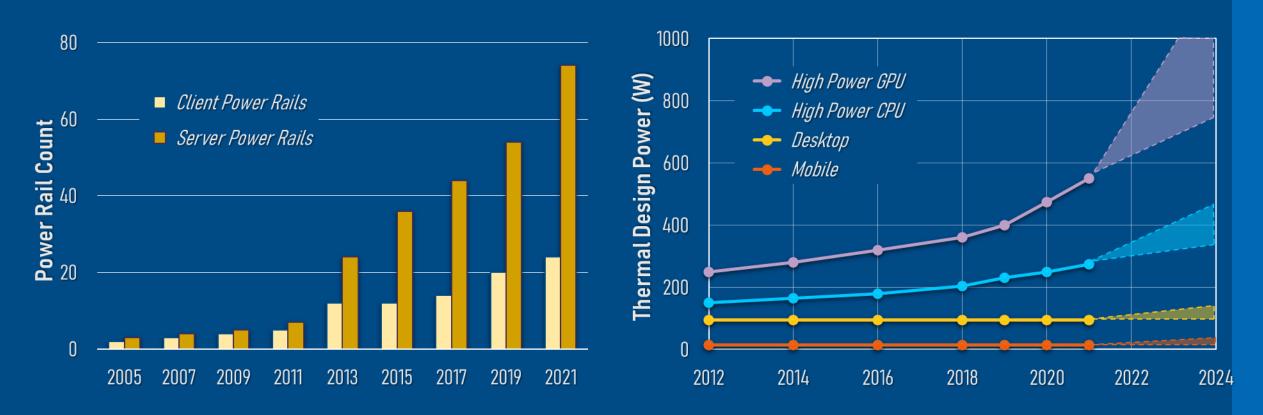

## Motivation for IVR

- The number of power rails has been scaling up with the core count

- Overall power levels have been going up in the high-power segments

## Integrated Power Delivery

#### **Power Gate**

- Key Components

- Power FETs

- Easy to integrate on Silicon

- No voltage regulation

#### LDO Regulator

- Easy to integrate on Silicon

- Restricted to low power rails

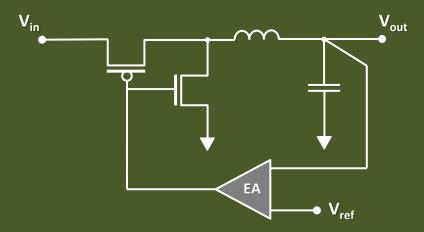

#### **Buck Regulator**

- Key Components

- Power FETs

- Inductor

- Output Filter Capacitor

- More expensive & difficult to integrate

- Typically used for high power rails to take advantage of their high efficiency

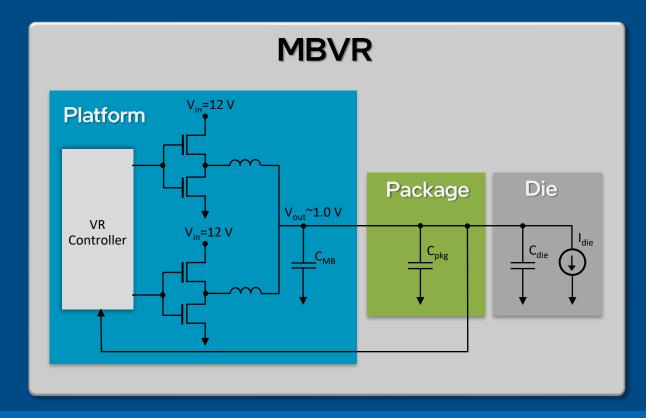

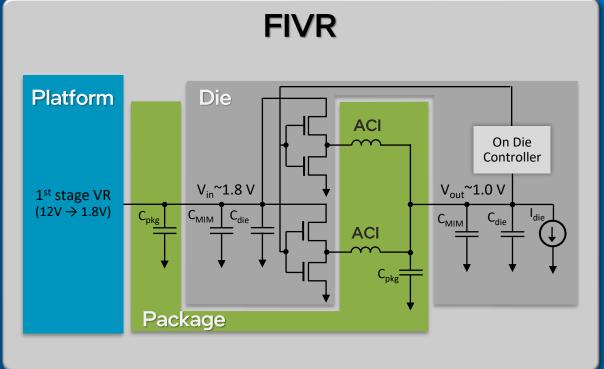

## Fully Integrated Voltage Regulator

- Fully Integrated Voltage Regulator (FIVR) was first introduced on the 4th Generation Intel® Core™ Processor

- The high frequency of operation enabled the use of Air Core Inductors (ACI) as the energy storage element

## First Generation FIVR

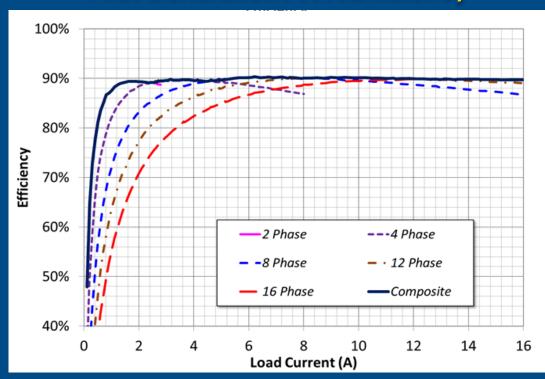

#### First Generation FIVR Efficiency

#### **ACI on First Generation FIVR**

- First generation of FIVR achieved an efficiency of 90% at full  $V_{out}$  (1.08 V)

- First generation FIVR ACI had a high Q-factor due to a large XY footprint and a 700um core

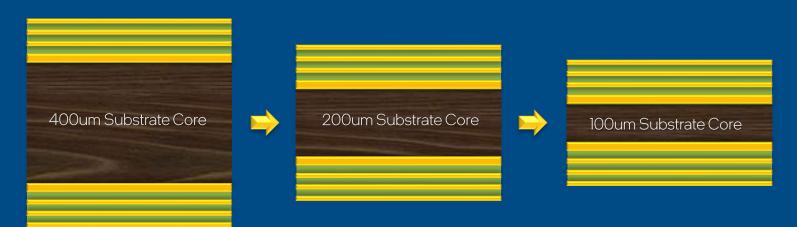

## **ACI Scaling Challenges**

- Process scaling reduces the core area and shrinks the XY footprint of the ACIs

- The push to thin and light devices has reduced the substrate core thickness which hurts ACI performance

#### Progression of Core Thickness in Mobile Segments

#### Inductor Footprint Scaling

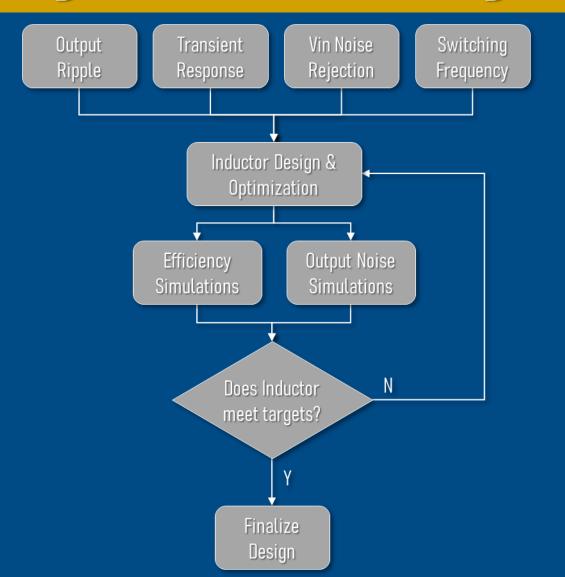

## Magnetic Inductor Design

| Parameter      | Design Target | Comments                     |

|----------------|---------------|------------------------------|

| Frequency      | 140 MHz       | Minimize RFI in Wi-Fi Band   |

| Inductance     | 2.5 – 3.0 nH  | Approx. 2 x ACI Inductance   |

| DC Resistance  | < 20 m0hm     | Less than 2 x ACI RDC        |

| Area/Inductor  | < 0.5 mm2     | Approx half the ACI size     |

| Thickness      | < 180 um      | To ensure MB clearance       |

| 1-Phase Ripple | < 20 mV       | Enable 1-phase operation     |

| Δη w.r.t ACI   | > 2% Peak Eff | Better light load efficiency |

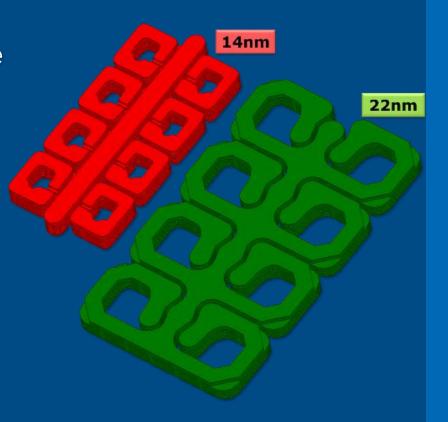

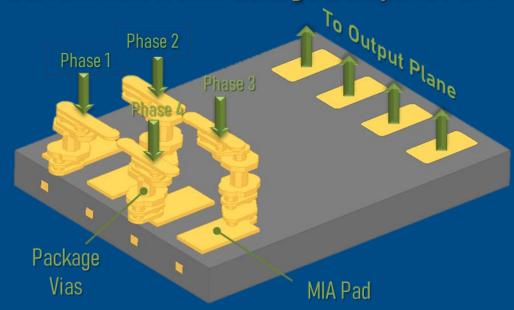

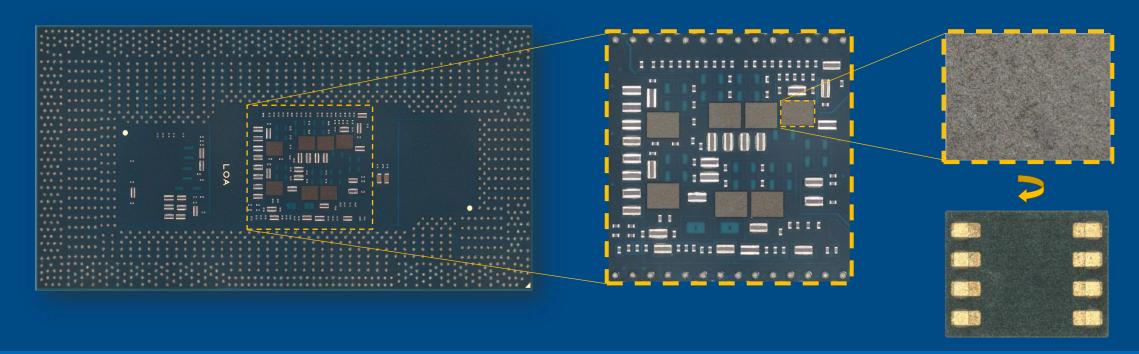

## Magnetic Inductor Array

- Custom Magnetic Inductor Array (MIA) module developed in collaboration with our supplier to meet the design targets

- Trace width and spacing chosen to meet inductance, resistance, mutual coupling and area targets

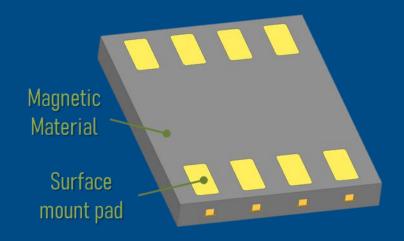

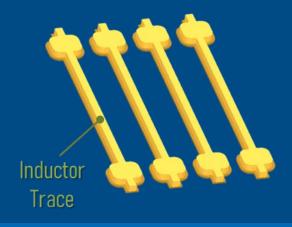

#### MIA Module

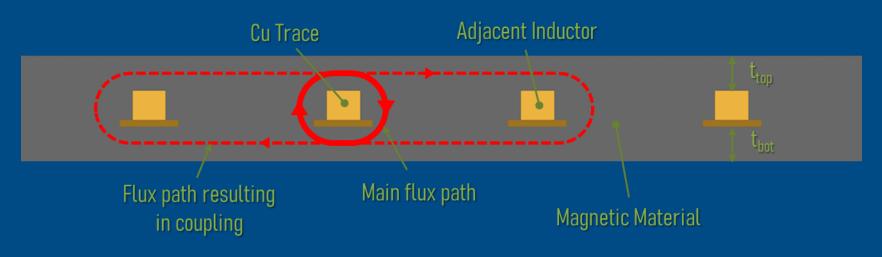

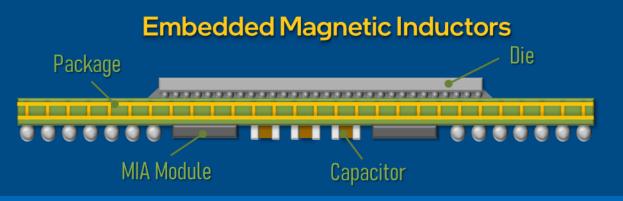

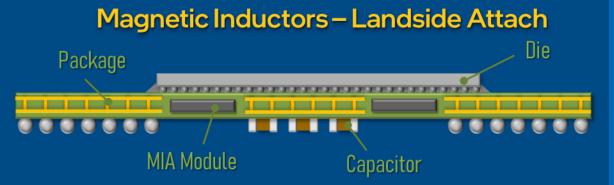

#### **MIA Cross-section**

#### Cu Traces in MIA

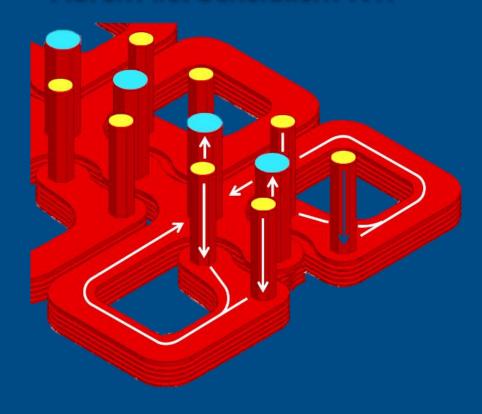

## MIA Assembly

- There are two possible configurations for MIA assembly

- Embedding the MIA module inside the package

- Landside attach of the MIA module

- Decision was made to go with landside attach to avoid core plane voiding and to decouple the MIA height requirements from the substrate core thickness

#### Current flow from Package Bumps to MIA

## MIA on Mobile Processor

- The 10<sup>th</sup> generation Intel<sup>®</sup> Core<sup>™</sup> microprocessors used a number of MIA modules for the different voltage domains

- The MIA modules were used selectively on certain phases to minimize cost

- The remaining phases were designed using standard ACIs

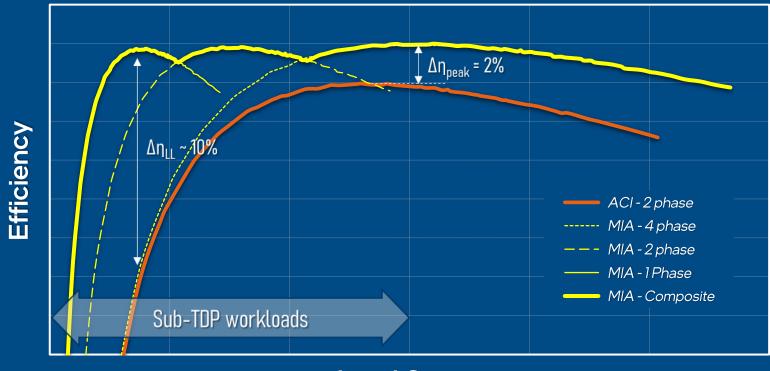

## **Efficiency Comparison**

- FIVR efficiency was measured with different MIA and ACI phase configurations

- MIA improves peak efficiency by 2%

- MIA achieves a light load efficiency of up to 10%

**Load Current**

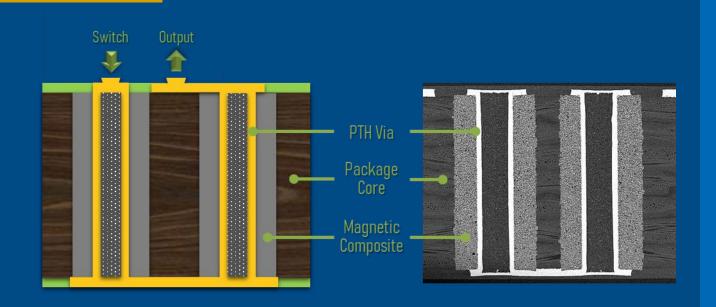

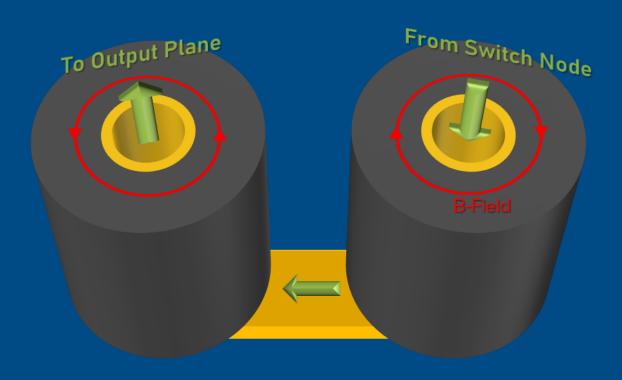

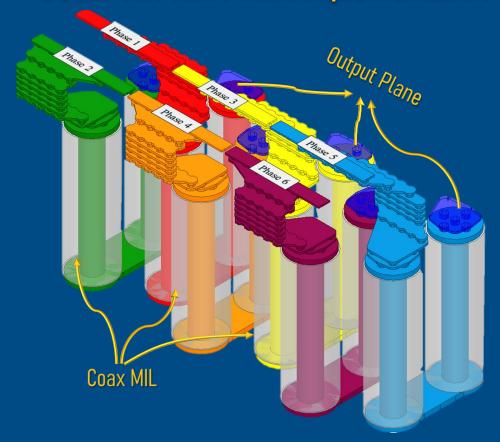

## Coax MIL Inductor

- Coax MIL inductors are fabricated using a magnetic composite plug in the core of the package

- PTH vias are drilled into the magnetic composite to create the coaxial magnetic inductor

#### Manufacturing Process Flow

## Coax MIL Implementation

#### Coax MIL Current Path & B-Field

#### Coax MIL Multi-Phase Implementation

- Coax MIL inductors exhibit low mutual coupling

- Inductors can be packed tightly to achieve a high-density multi-phase design

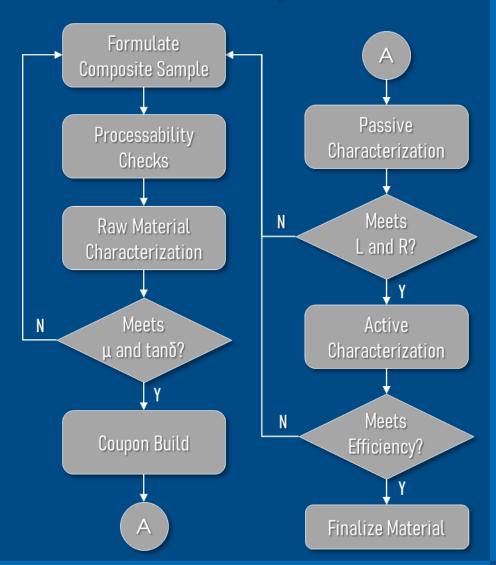

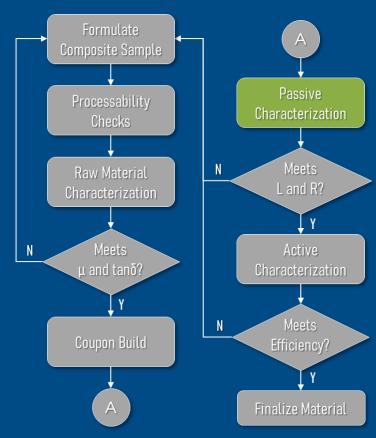

## Magnetic Material Design

- Desired Electrical properties

- High permeability and low loss at switching frequency

- Low coercivity

- Soft saturation with per phase Imax support > 5A

- Processability

- Rheological properties

- Viscosity and flow

- High aspect ratio pluggability (AR ~ 2.5-3.0)

- Substrate process compatibility

- Chemical resistance: Seed layer, etchants

- Mechanical properties

- Mechanical drilling

- Low CTE (<20ppm/°C)</li>

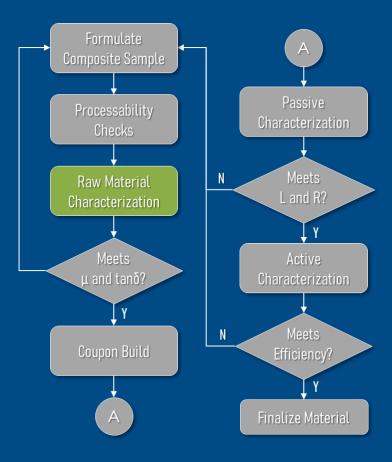

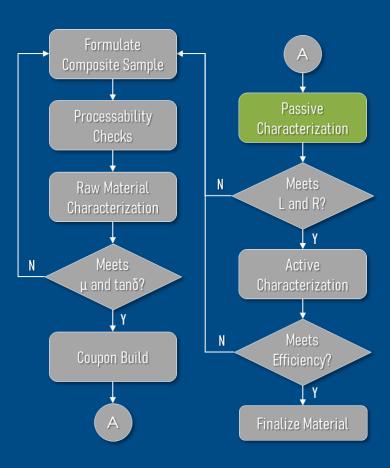

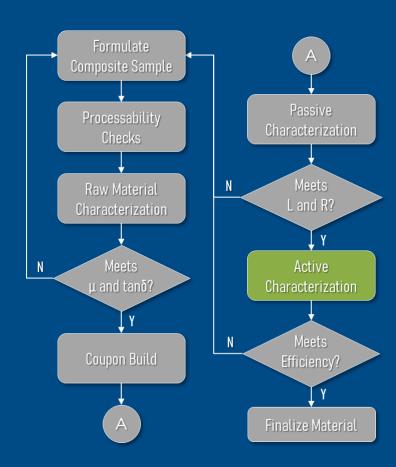

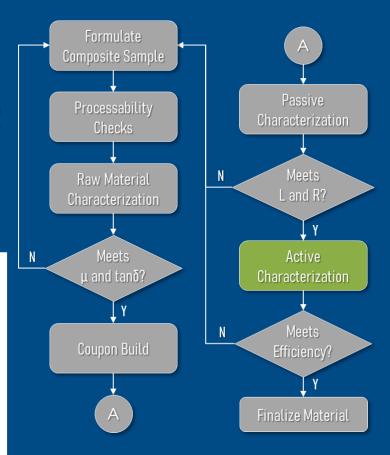

#### **Material Development Flow**

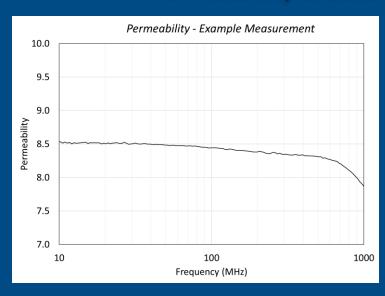

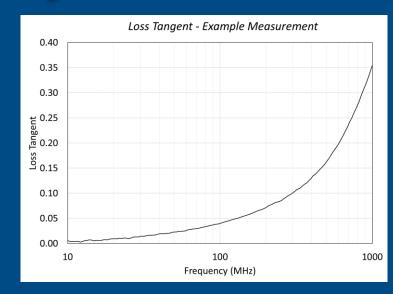

## **Material Characterization**

- Donut shaped rings are cut out of cured magnetic sheets and characterized using an impedance analyzer

- Requires relatively thick samples and accurate dimensional characterization is critical

#### Permeability & Loss Tangent Measurements

## **Passive Characterization**

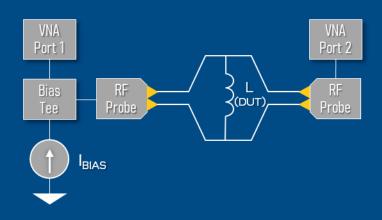

- Two-port shunt measurement used to characterize inductor performance under current bias

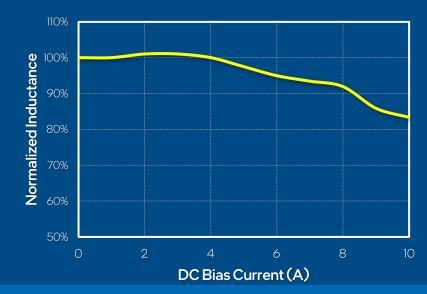

- Coax MIL inductor shows good saturation characteristics with less than 10% drop in inductance at 8A

#### **VNA Setup**

#### **Saturation Characteristics**

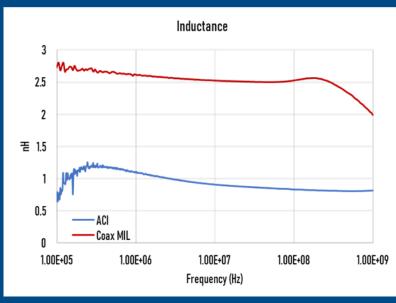

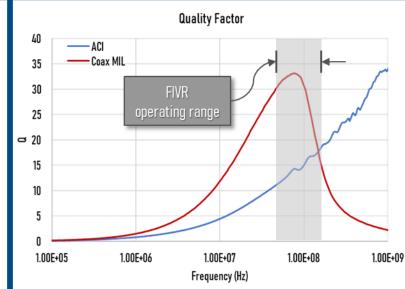

## **Passive Characterization**

- Coax MIL doubles the inductance of an ACI based design while using half the area

- Coax MIL also provides a significant increase in Q-factor over the ACI based design

#### Inductance and Quality Factor vs. Frequency

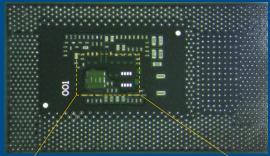

## **Active Characterization**

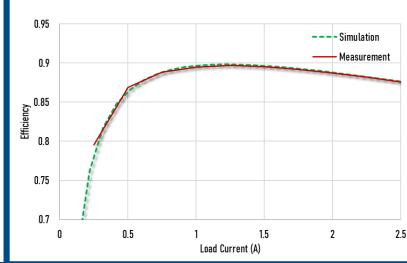

- Standalone active characterization test vehicle used to characterize efficiency of the switching regulator

- Coax MIL inductor performance is compared to simulation and screened for large signal losses

#### **Active Measurement Setup**

Pads for MIA Module

## **Active Characterization**

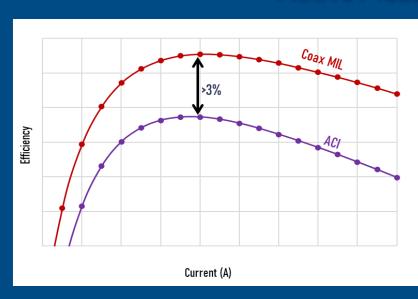

- Coax MIL improves peak efficiency by 3% over an ACI based design while occupying less area

- Peak efficiency matches that of the first generation FIVR while occupying a quarter of the inductor footprint

#### **Active Measurement Results**

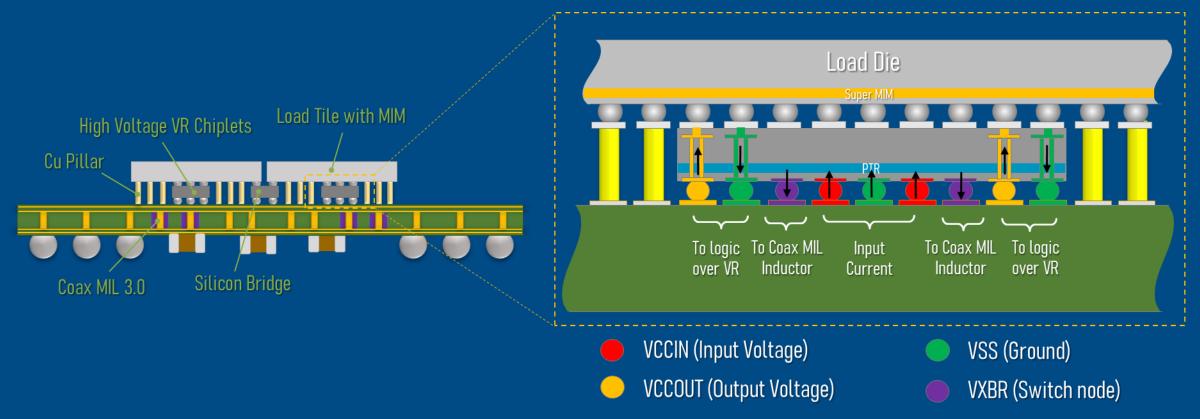

## IVR with Foveros Omni

- Foveros Omni enables the design of next generation high voltage IVR by disaggregating the IVR from the SoC

- Improved inductors (Coax MIL 3.0) would be required to enable this

## Summary

- As power levels and the number of on-die power rails go up, some for of integrated voltage regulation is required to keep the platform PD requirements manageable

- FIVR, an on-die buck regulator, was introduced on the 4<sup>th</sup> generation Intel<sup>®</sup> Core<sup>™</sup> microprocessor with air core inductors

- Core area scaling has caused the quality of the ACIs to deteriorate impacting overall efficiency

- Magnetic inductors are being used to replace ACIs to recover the efficiency loss

- Magnetic Inductor Array (MIA) was used on thin core mobile processor

- Coax MIL will be introduced on Xeon microprocessors with a thicker package core

- Work is ongoing to scale the performance of the Coax MIL inductors

- FIVR with Coax MIL 2.0 can achieve an efficiency of 92% for 1.75 to 1.0 V conversion

- IVR with Foveros Omni and Coax MIL 3.0 can achieve high voltage (Vin = 5V) conversion by disaggregating the power delivery from the SoC

## Acknowledgement

Krishna Bharath, Mike Hill, Beomseok Choi, Siddharth Kulasekaran, Huong Do, Anne Augustine, Mat Manusharow, Leigh Wojewoda, Bill Lambert, Sriram Srinivasan Yongki Min, Prithwish Chatterjee, Haifa Hariri, Brent Williams, Tarek Ibrahim, Jonathan Douglas, Srikrishnan Venkataraman, Chris Schaef

#