# Integrated Power Management for Wearable applications: Opportunities & Challenges

Santosh Kulkarni, Cristiano Azzolini

PwrSoc2020

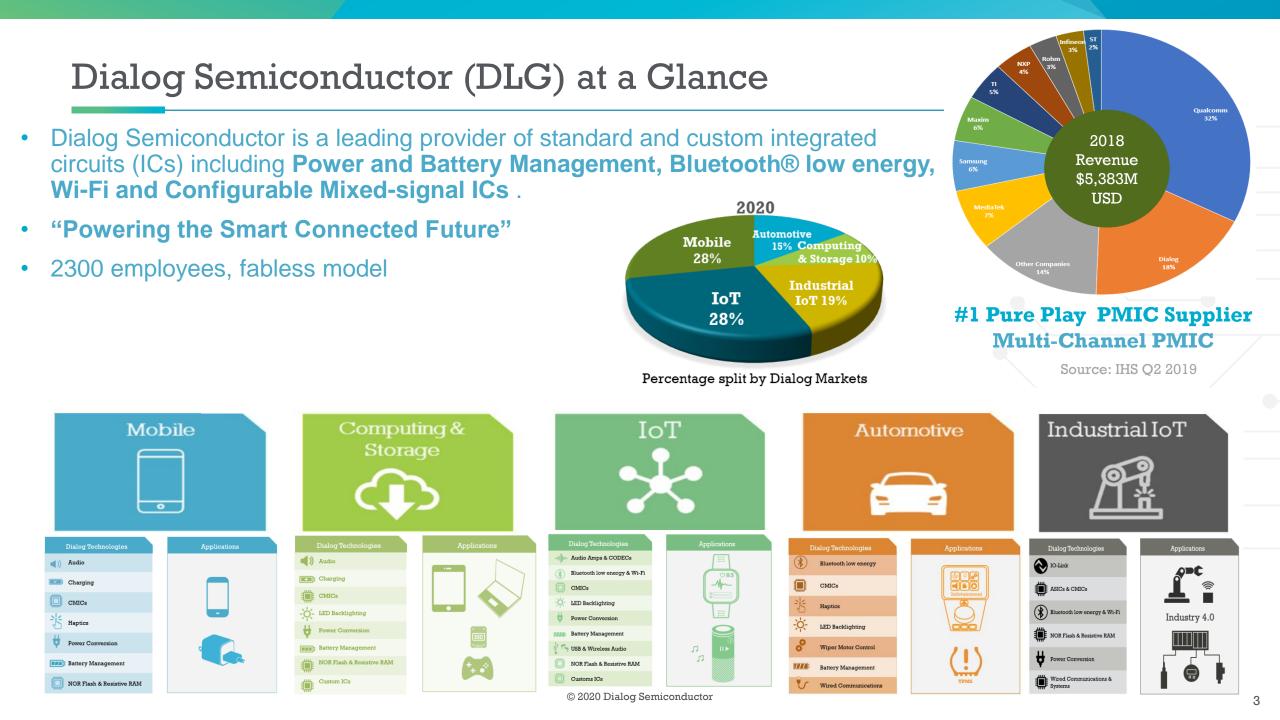

# Agenda

- Dialog Semiconductor

- Integrated Power Management for wearable applications: opportunity, markets, complexity, requirements

- Dialog's solutions for novel Integrated Power Management: performance, voltage, size, cost

- Open challenges for the future

### What is wearable?

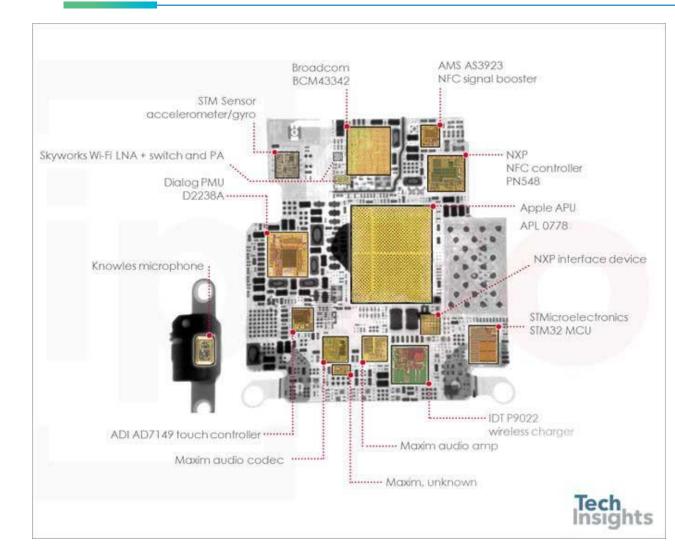

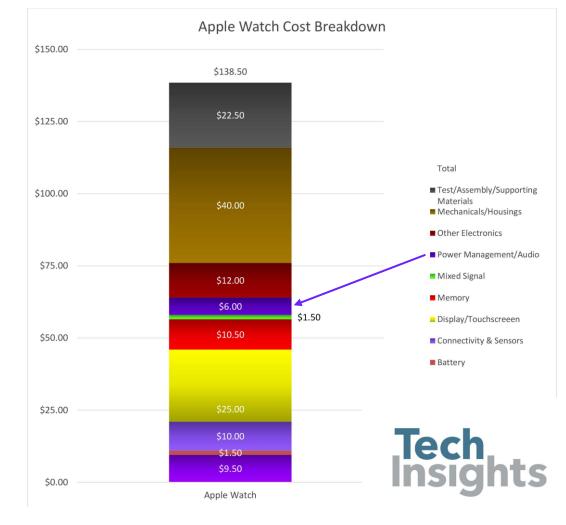

Wearable devices driving stronger need for integration of technologies including power management for battery chargers, displays, SoC, sensors, audio.

### Opportunity: growth of wearable market

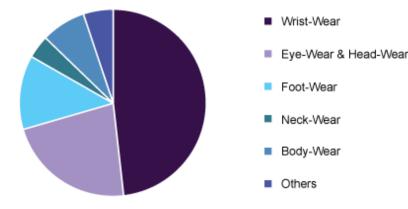

7.06 6.18 2016 2017 2018 2019 2020 2021 2022 2023 2024 2025 2026 2027 Eve-Wear & Head-Wear Foot-Wear Wrist-Wear Neck-Wear Body-Wear Others

U.S. wearable technology market size, by product, 2016 - 2027 (USD Billion)

Source: www.grandviewresearch.com

Global wearable technology market share, by application, 2019 (%)

#### Hearables/TWS

- Key Trends: Rapidly growing market segregating into

- High-end (Tier-1 OEM): high integration, power, complexity

- Mid-end (Tier-2 OEM): more features fuel gauge, communication protocols (PLC)

#### AR/VR

- Advancements in display technology (µLED) are key to AR success

- VR systems are increasing in capability. Popularity and shipments are growing

#### Smartwatch

- Key Trends: transition to AMOLED for broader market

- Increased functionality with simultaneous increase in battery life

- SAM growing annually at double-digit %.

## **Opportunity: Integrated Power Management for Wearables**

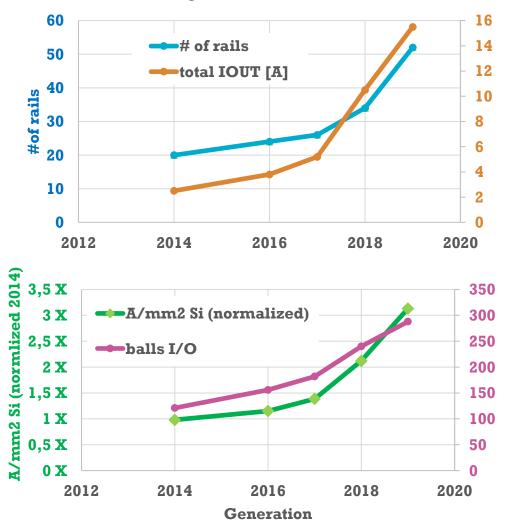

### PMIC for Wearables: trends

#### Ultra-high-end wearable PMIC

#### Medium-end wearable PMIC

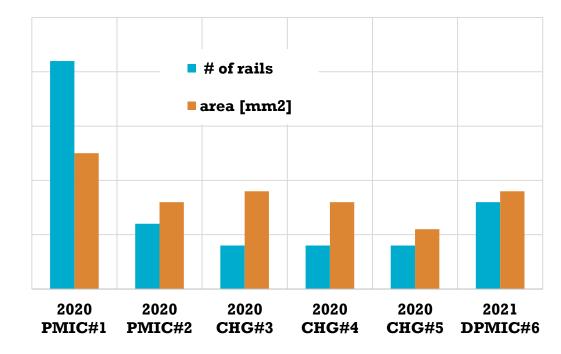

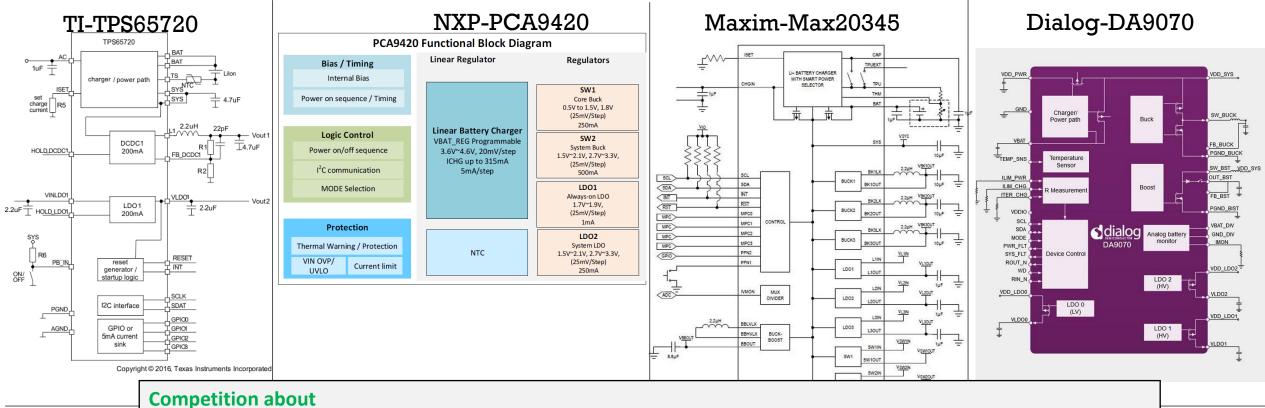

## **Typical PMIC products for Wearables**

#### PMIC includes- Battery charger, DC-DC, LDOs, I2C interface

- ✓ Compact size

- ✓ Low Quiescent Current

- ✓ Noise performance / EMI mitigations

- ✓ Increased functionality and integration

### Challenge: Requirements of Integrated Power Management for Wearables

- Performance requirements (Iq, transient, efficiency)

- Ship mode: wake-up circuits <100nA. Significant challenge on power FETs.

- Sleep mode(s): <500nA with regulators on

- Voltage requirements

- Li-Ion batteries dominate

- 2.2-5V are must-have. Strong demand for supporting 2V minimum (transient of some ms = DC...)

- USB interface 20V support (up to 30V for customer-specific reliability tests)

- Integrated PMIC to generate power **negative** supplies (display): i.e. 5-10W @ -10V

- Integrated PMIC to support +30V and -10V simulateneously, i.e. 40V BCD Process Tech

- Size requirements

- Tier-1: extremely high integration, ~20-40 mm2 PMIC (30+ rails)

- Tier-2: simpler power tree but growing ~8-15 mm2 PMIC (5-15 rails)

- Cost requirements:

- Competing with stand-alone regulators

- LDO ~0.01-0.02 USD optimized for low cost

- DC/DC ~0.05 USD optimized for low cost

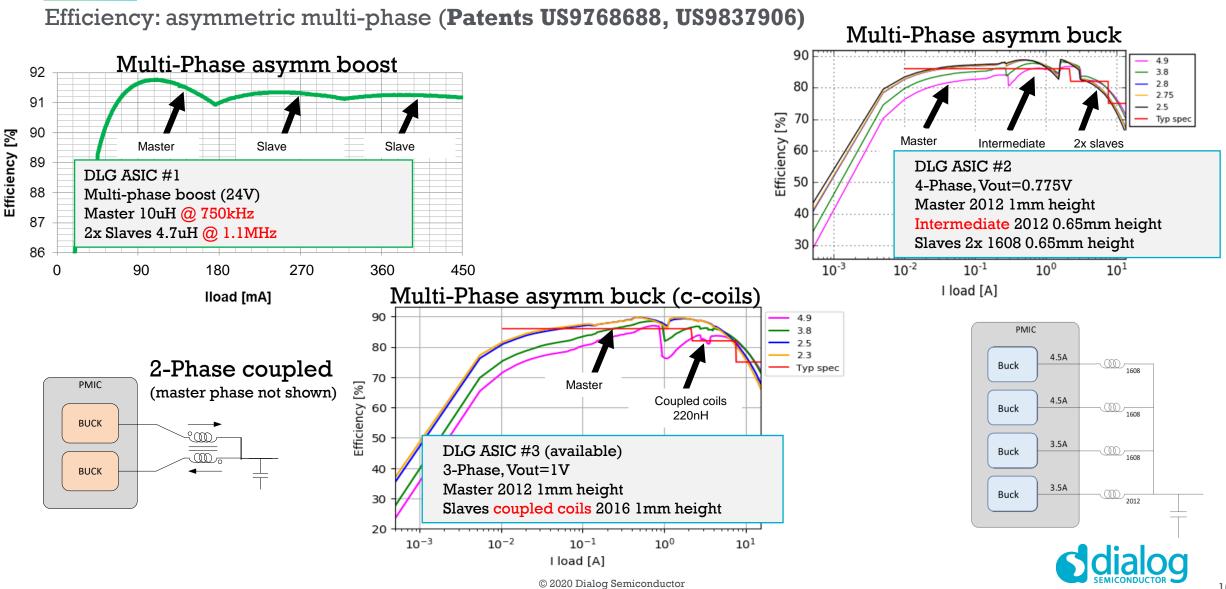

### DLG Solutions: Architectures for **performance** requirements

## DLG Solutions: Architectures for **performance** requirements

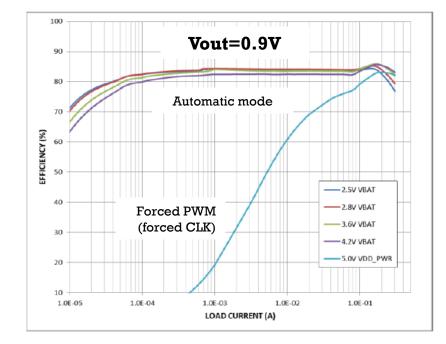

#### Ultra-low-IQ PMIC

- Bucks:

- 600nA

- >80% efficient at 10uA load, 1.8V, 3.3uH, 10uF

- Programmable VOUT 0.6V to 1.9V, IOUT 300mA

- ±2.5% Output Voltage Accuracy

- Dynamic Voltage Scaling (DVS)

- 20mV Load transient response 0-50mA t<sub>R</sub>=1us

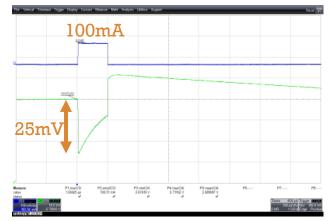

#### LDOs:

- 300nA

- 25mV load tran (0-100mA, trise = 1us)

- Programmable VOUT 1.8V to 3.3V, IOUT 100mA

- Design techniques:

- Dynamic bias

- Feedforward paths (transient)

- Process technology

- Leakage control

- IQ vs size: compact device

COUT=1uF, PW=200us, VIN=3.8V, VOUT=2.7V, room temp

© 2020 Dialog Semiconductor

#### DLG Solutions: Architectures for **voltage** requirements

- Trend: power-tree tend to move from pure Buck to Buck-Boost

- Mostly driven by system with multiple batteries, example wearable TWS (charging case + earbuds)

- Driven by Li-Ion batteries min transient voltages (i.e. 2.0V) while analog sensors voltage don't scale (i.e. CMOS camera Vpixel 2.85V)

- Stable voltage (no OV/UV/glitches) during mode transitions.

- Challenges to optimize area/Iq of loop control for Buck-mode, Boost-mode and Buck-Boost-mode.

- Challenges of die-size (+50% switches, additional control loop circuitry)

- Push on technology to optimize FETs FoM (mOhm\*mm2)

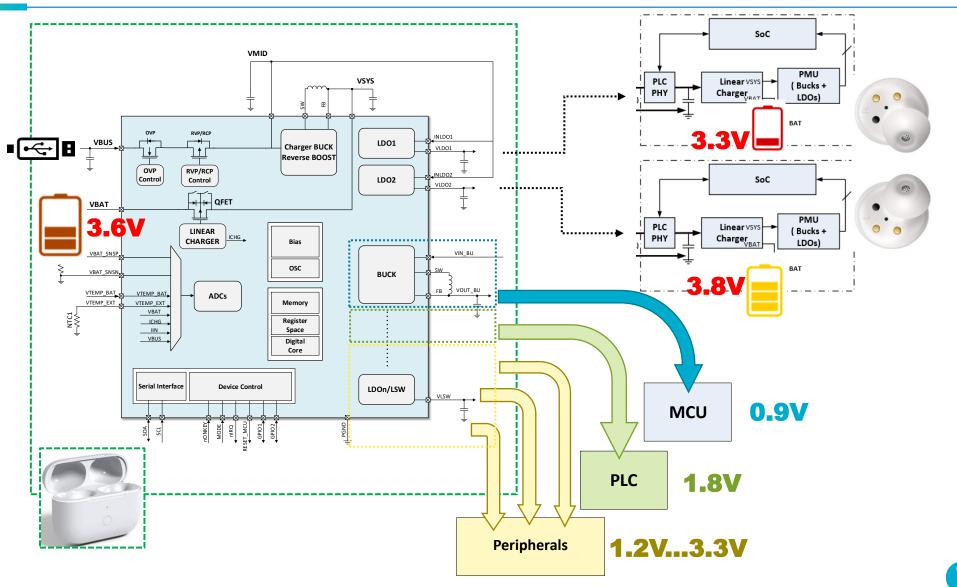

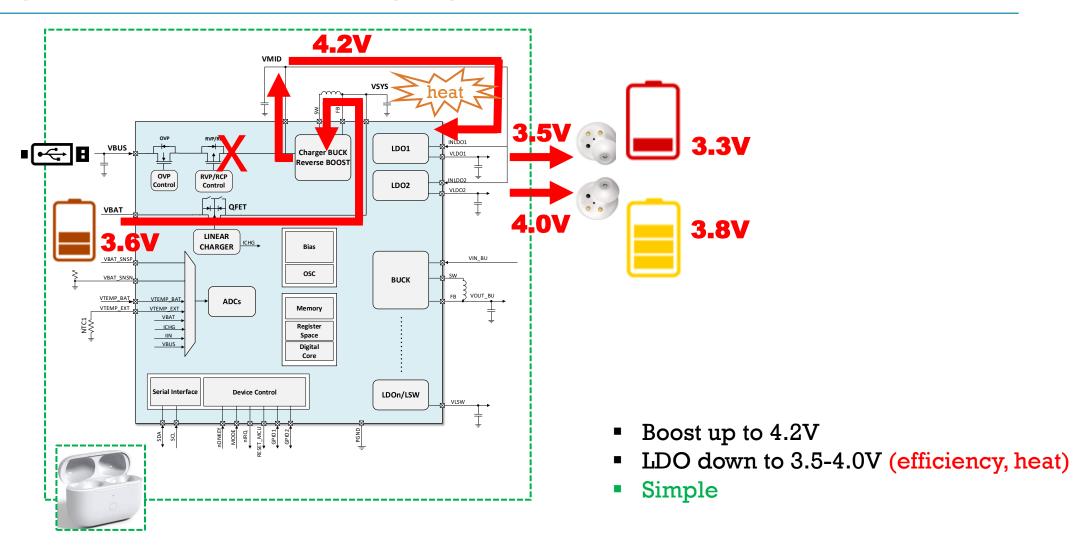

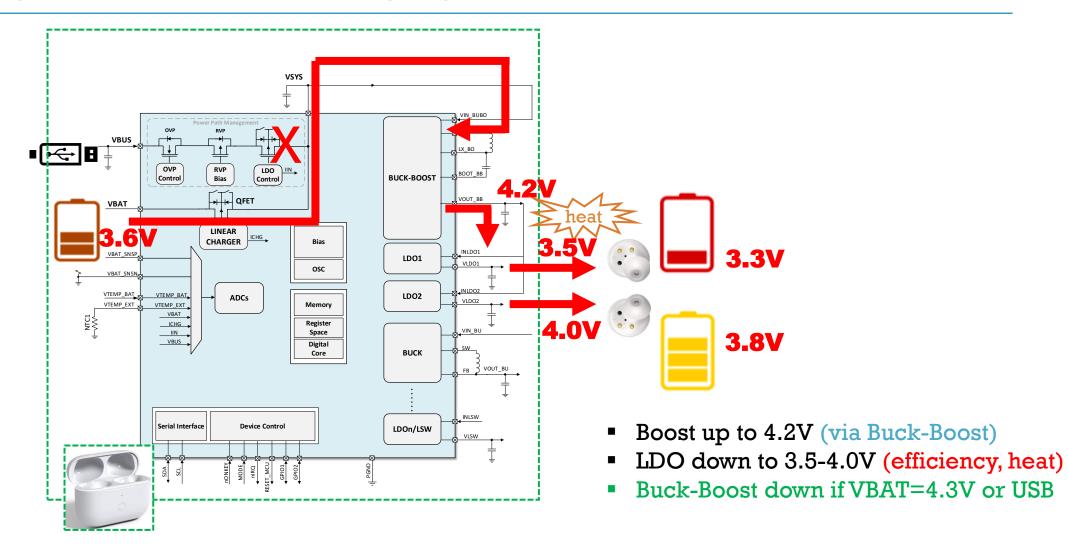

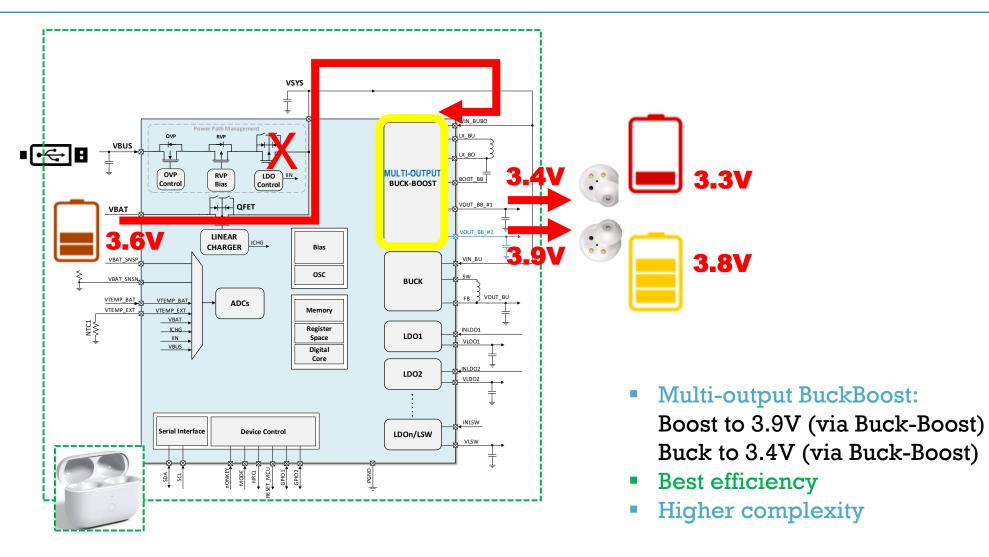

#### DLG Solutions: Architectures for voltage requirements. Example TWS

© 2020 Dialog Semiconductor

## Charging TWS batteries (charging case and earbuds) - I

### Charging TWS batteries (charging case and earbuds) - II

## Charging TWS batteries (charging case and earbuds) - III

## DLG Solutions: Architectures for voltage requirements

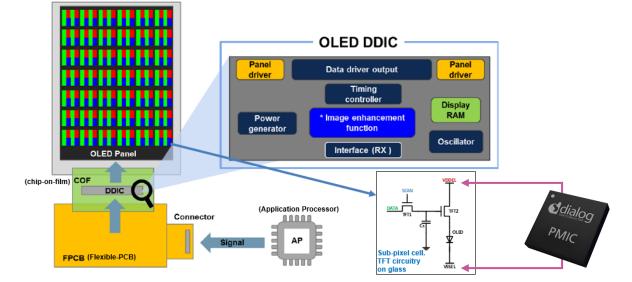

#### Negative voltages for OLED Displays

| Vout [V] | Iout [A] | Pout [W]               | Note                                                       |

|----------|----------|------------------------|------------------------------------------------------------|

| -115     | 0.21     | 510<br>(from neg rail) | Eff >90% @3.8 Vin, -5 Vout<br>Single phase and multi-phase |

Display PMIC is often a Chip-On-Film: PDN + pulsed loads is a challenge (over/under-shoots, stability, etc.)

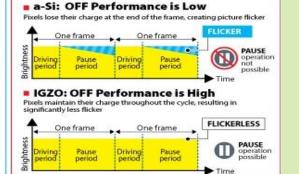

#### **#1 Pixel technology**

#### ENERGY USE

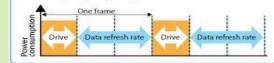

New Operating Method (pause-operation)

With less leakage, IGZO pixels remain charged and therefore can be driven in pulses, saving energy

#### PERFORMANCE

Low-leakage IGZO TFT: pulsed load 0-100%

#### #2 Panel substrate technology

## DLG Solutions: Architectures for solution size requirements

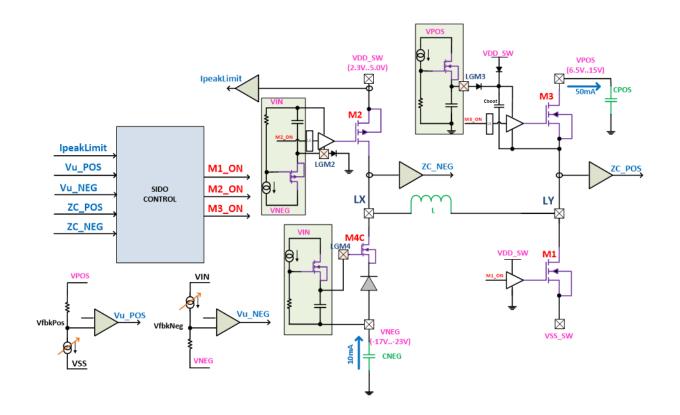

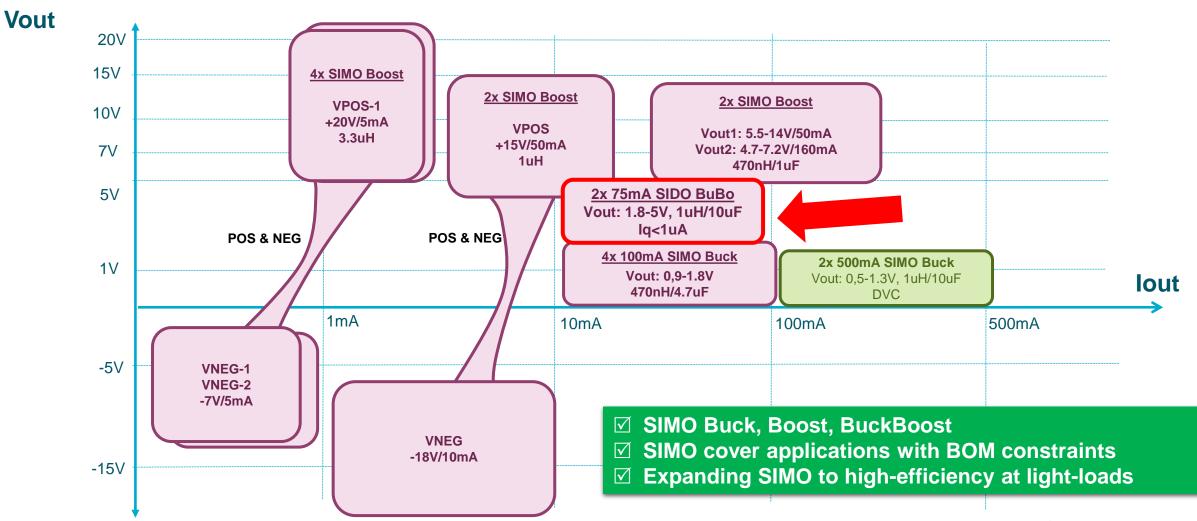

Single-Inductor-Multiple-Output Architectures (i.e. positive/negative boosted rails)

#### **Key Features**

- DLG SIMO BOOST IP generates one positive boosted rail and one negative boosted rail using a single coil.

- Minimum BOM and independent programmable outputs range. Example IP:

- VPOS = 6.5V to 15V @50mA

- VNEG = -10 to -15V @10mA

- Full H-bridge.

- Current limit adaptive with conditions for ripple optimisation.

- SIMO BOOST IP portfolio expands to 2X VPOS boost and 2X NEG boost, 4X SIMO

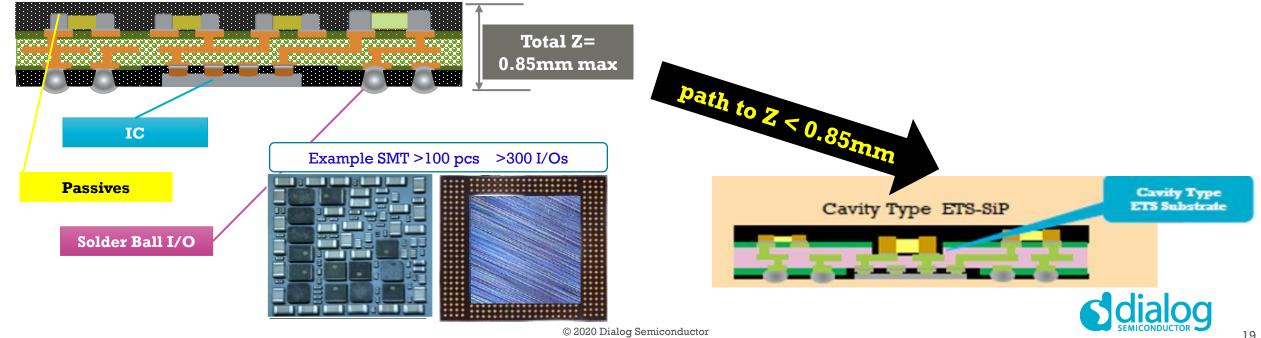

## Solution size requirements: integrated PMICs in package

- Opportunity for integrating passives as packaged solution rather than monolithic solution

- Total height to be <0.85mm or <0.65mm

#### Package Passives

- Require low AC losses: to minimize AC losses, higher inductance in smaller volume is required

- DLG offer ETS 2.5D & eWLP SiP solutions

- Cross-section of DLG ETS 2.5D SiP (US Patent Appl. 15718080, DE Patent Appl. 102018207060.1)

### DLG Solutions: Architectures for **cost** requirements

Cost targets

- Competing with stand-alone regulators

- LDO ~0.01-0.02 USD optimized for low cost

- DC/DC ~0.05 USD optimized for low cost

- Power sequencing moves from MCU to PMIC → not always accounted for when calculating solution cost (SW footprint, MCU wake-up energy)

- Strong push on Process Technology with high-performance FETS (Rdson, FoM, BV)

- Add value: integration of more features into single ASIC (power, charging, sensing, fuel-gauging)

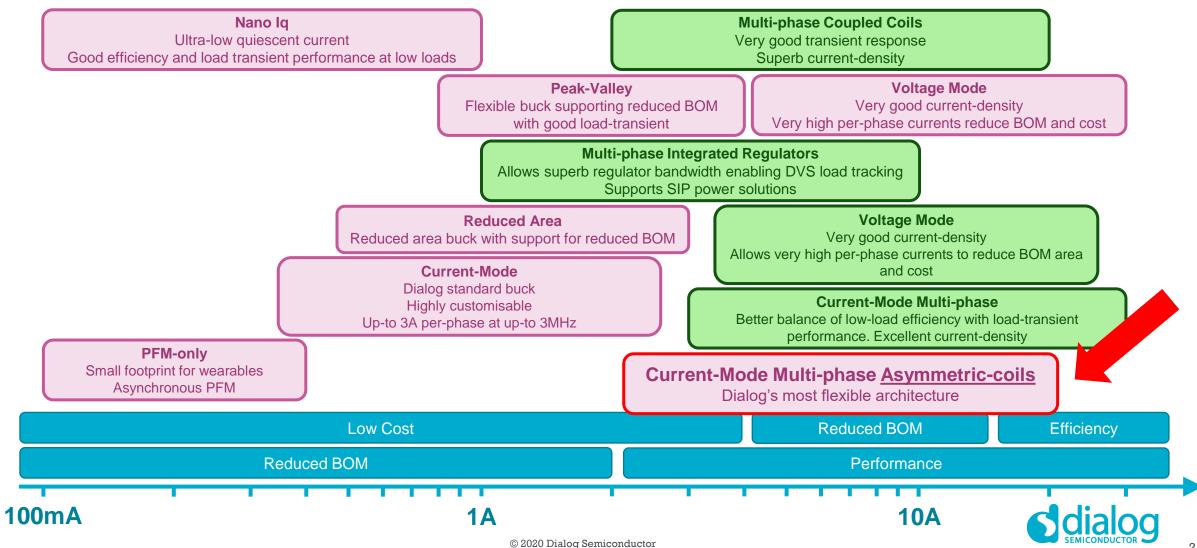

## DLG technology portfolio: DC/DC bucks

Best suited for other applications

## DLG technology portfolio: DC/DC boosts

WLED drv WLED drv 24V 24V/50mA 24V/450mA 20V SIDO Boost μLED VPOS PMOLED/MIP/HRM 15V/1.2A 20V 18V/100mA 1-10mA **SIDO Boost** OTG boost **General Purpose** VPOS 5V-15V, Audio 10V 12V/400mA **10W POUT** +15V/50mA 10V/1A TFT/LED Vboost capacitive TFT/AMOLED SIDO Boost 9V/150mA General 7.4V/300 VPOS Purpose OTG/Flash-Torch drv 4V-8V 7V/700mA OTG 6V/2A Gen. Purpose 10mA 5V/3A 5V 5.6V/250mA Wireless Charger TX (HV input) 6-16V, 5W Pout 2.0A 50mA 1.0A 3.0A 0.5A 10mA 1mA lboost AMOLED SIDO -5V -6V/300mA Boost TFT/AMOLED VNEG (capacitive) -1/-7V -7V/80mA AMOLED 1-5mA Multi phase -7V **SIDO Boost** -5...10V/1A **VNEG** -15V/10mA -15V © 2020 Dialog Semiconductor 22

Best suited for Wearable

Best suited for other applications

## DLG technology portfolio: multi-output DC/DC

© 2020 Dialog Semiconductor

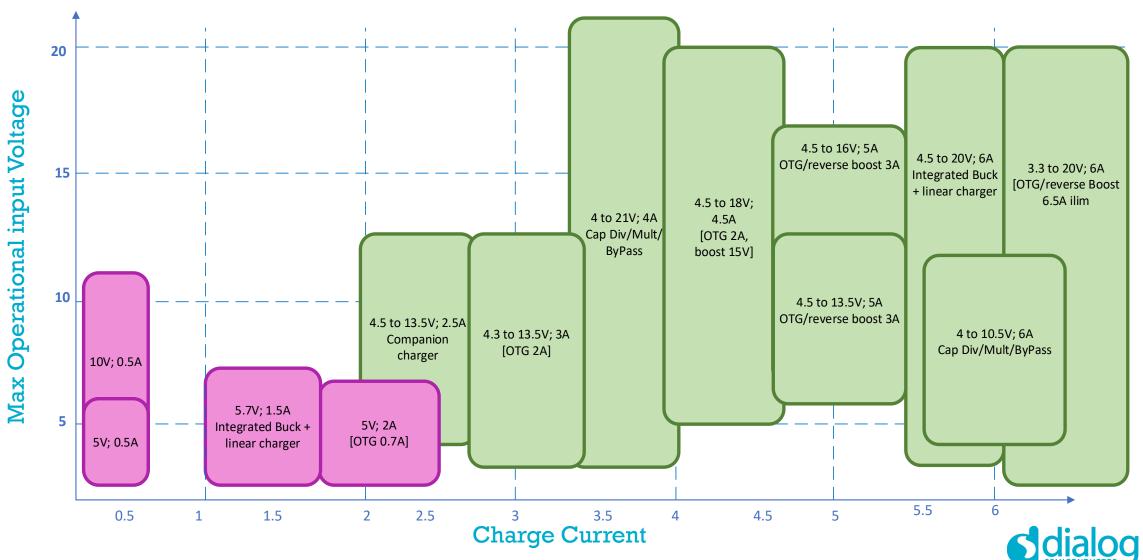

### DLG technology portfolio: DC/DC battery chargers

<sup>© 2020</sup> Dialog Semiconductor

Best suited for Wearable

Best suited for other applications

## Thoughts on Future

#### Wearable requirements driving the need for integrating functionalities & components in PMICs

- System level approach required to address this challenge of highly integrated PMICs

- Novel architectures multi-phase (uncoupled, coupled), ultra-low-lq, SIDO, SIMO

- Novel functionalities SIMO, negative supplies

- Novel external components low profile, low loss passives

- Novel integration technology Ultra-thin 2.5D System-in-Packages

- DLG developing innovative solutions to address all aspects of Wearable PMICs

- DLG working with external partners to develop new passives with improved loss performance, power densities

#### **Open challenges for future**

- Increase output power with reduced solution size

- Hybrid architectures DLG novel "hybrid" inductive/capacitve solutions (patents pending)

- Trade off between higher integration vs performance vs costs

- Adding value to integrated PMIC

# Powering the Smart Connected Future

www.dialog-semiconductor.com

Personal • Portable • Connected

cristiano.azzolini@diasemi.com santosh.kulkarni@diasemi.com

© 2020 Dialog Semiconductor