# Greetings from Georgia Tech

## Integrated Voltage Regulators for **Computing Applications**

Madhavan Swaminathan ckaging & Electromagnetics John Pippin Chair in Micr School of Electrical & Co School of Materials Science & E Director, 3D Systems Packaging Research Center (PRC,

**Georgia** Institute for Electronics **Tech** ∦and Nanotechnology

#### Outline

#### **Overview**

- Low & High Voltage Converters

- □ Integrated Magnetics

- □ Summary

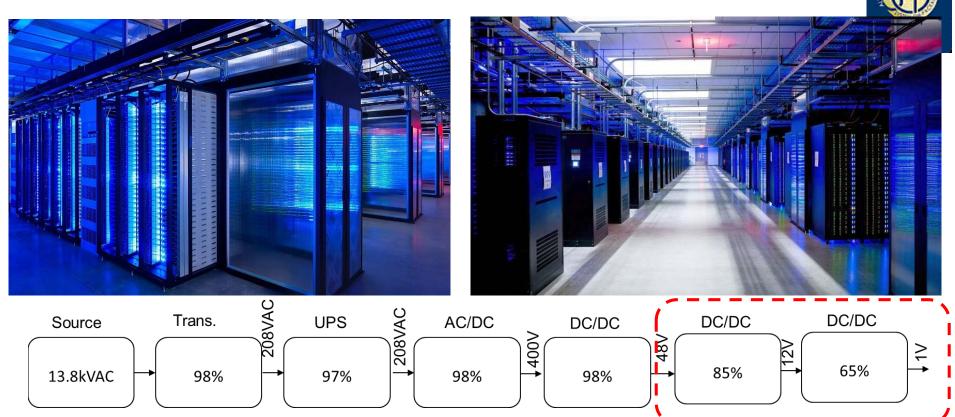

#### **Data Centers & Energy**

- Data Centers consume 70 billion KWh today in USA

- For every <u>2W drawn from the grid only 1W</u> is used by the Data Center

20% improvement in efficiency can translate to 20% reduction in energy consumption

Source: Dept. of Energy, USA

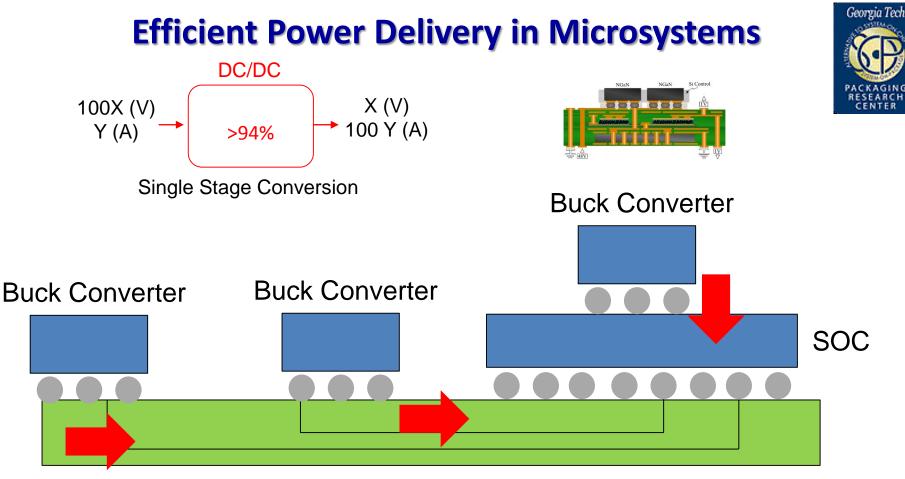

□ Bring the converter (power source) in close proximity to SOC

- Significantly reduce Cu losses due to shorter current paths

- Need: High Efficiency, Highly Integrated, Highly Miniaturized, High Conversion Ratio, Single Stage Converters

- Low energy circuits

PwrPACK Workshop 2019

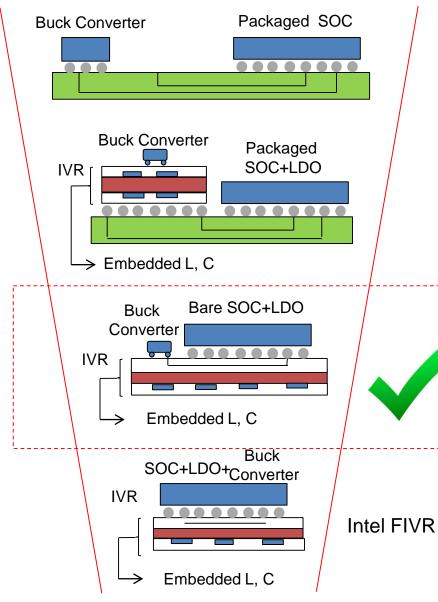

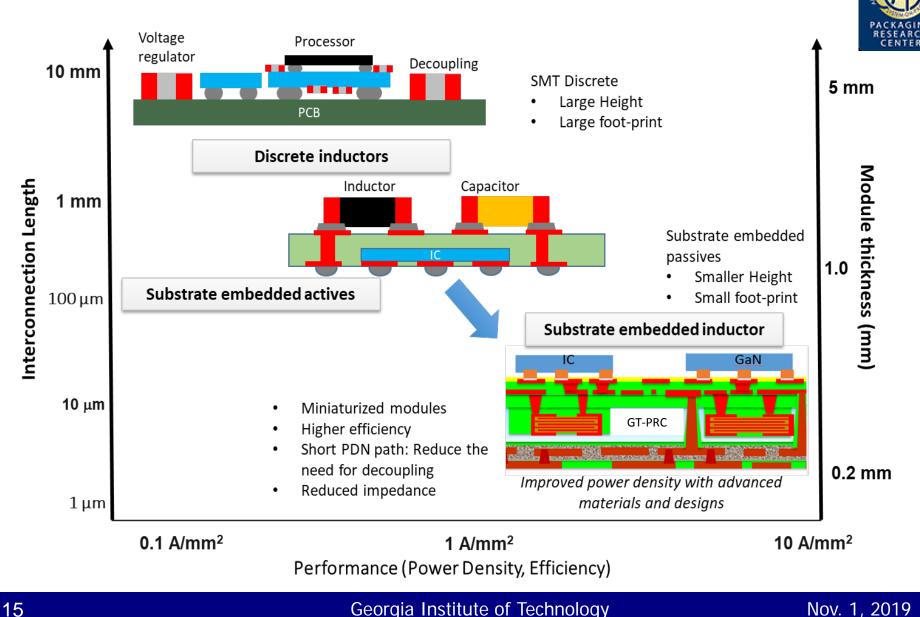

### Voltage Regulation and Integration

Business as usual Advantages: Reasonable signa

<u>Advantages</u>: Reasonable signal and power <u>Integration</u>: Low; Solution: Non-disruptive

New technology: SIP with embedded C & L, Buck Converter to SOC on board <u>Advantages</u>: Slow/fast operation, Medium efficiency, Good Signal and Power Integrity, <u>Integration</u>: Medium; Solution: Non-disruptive

New technology: SIP with embedded C & L, Buck Converter, SOC in package <u>Advantages</u>: High Performance, High Efficiency, Modular, Excellent Signal and Power Integrity, Cost effective, Thermal Mgmt. <u>Integration</u>: Very High; Solution: Disruptive

New technology: SOC with on-chip integrated IVR, embedded C & L in package <u>Advantages</u>: Very High Performance <u>Challenges</u>: Non-modular, Non-scalable, Thermal Mgmt. <u>Integration</u>: Ultra-High; Solution: Disruptive

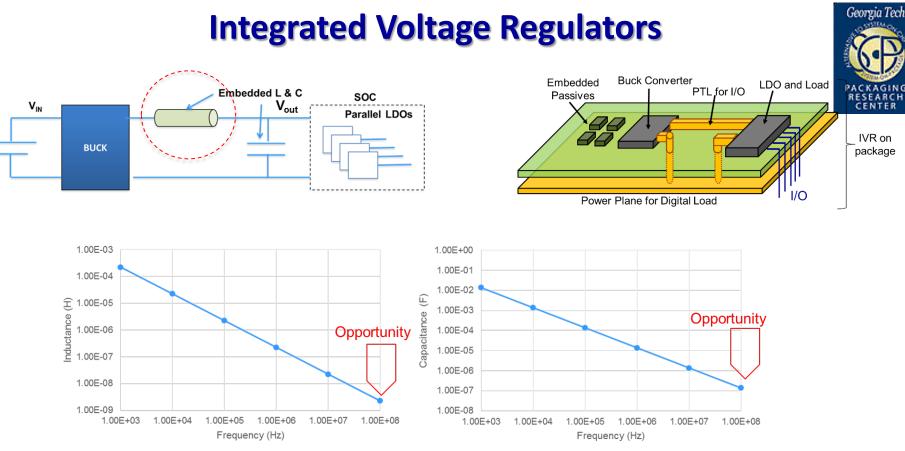

- L and C values reduced by increasing switching frequency

- Provides an opportunity for embedding and miniaturization in <u>package</u> (Reasonable values for L and C)

- However, losses increase as switching speed increases

- Transistor losses

- Inductor losses (DC, eddy current, skin, hysteresis and proximity effect)

- □ But <u>tradeoff</u> possible between speed, component size and technology

PwrPACK Workshop 2019

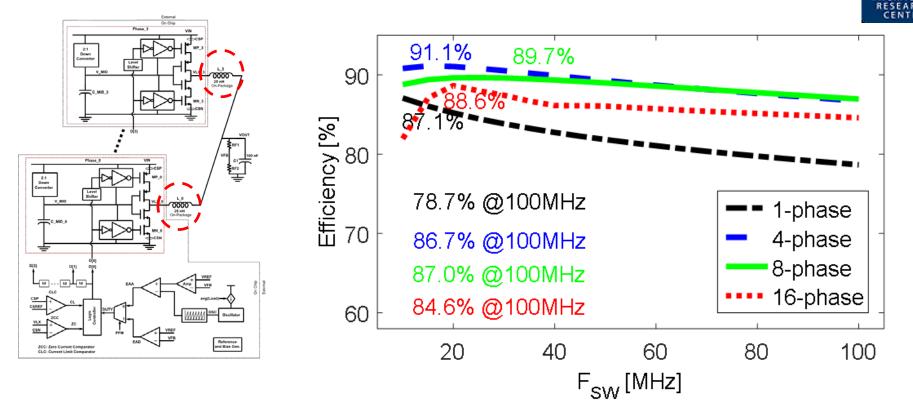

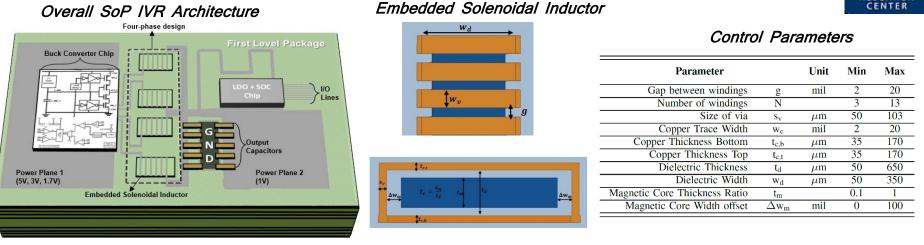

### Design Space Exploration through Chip-Package Co-Design: 1.7V/1V

□ Tradeoff Analysis Critical

- □ Number of phases? (4 phases w/100nH total inductance)

- □ Maximum power efficiency 91% @ 20MHz

- □ Power efficiency improves by ~2% with transistor scaling

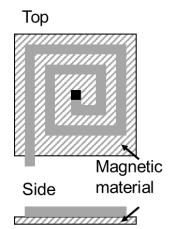

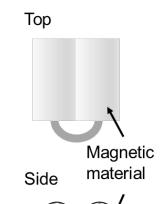

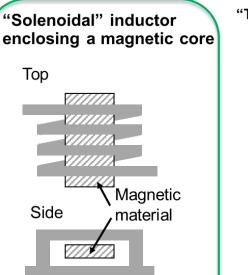

#### **Inductor Design Options**

PwrPACK Workshop 2019

Several inductor designs with magnetic material possible (published in literature)

Copper winding enclosed by

Spiral inductor on or between magnetic material

- Advantage: simple structure / simple fabrication

- **Disadvantage:** Inductances larger than a few nH require high • permeability or large inductor area

a magnetic material

- Advantage: coupling between different inductor phases possible

for DC field cancellation

- **Disadvantage:** inductor uses single winding high permeability required

- Advantage: higher number of windings – higher inductance for a given permeability

- Disadvantage: "3D" structure – challenging fabrication

Advantage: Higher inductance, Q & inductance density Disadvantage: "3D" structure – challenging fabrication

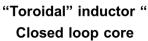

### Inductor Design – An Example

- Final design: 4-phase design with 25nH inductance per phase

- □ Inductor properties as specified below:

|                          | Optimized inductor |  |

|--------------------------|--------------------|--|

|                          | design             |  |

| L [nH]                   | 24.8               |  |

| R <sub>DC</sub> [mΩ]     | 14.7               |  |

| R <sub>AC</sub> [Ω]      | 2.26               |  |

| C [pF]                   | 1.9                |  |

| Area [mm <sup>2</sup> ]  | 11.6               |  |

| L / L <sub>Aircore</sub> | 3.1                |  |

| Peak eff. 5V:1V          | 79.4%              |  |

| Peak eff. 3V:1V          | 88.5%              |  |

| Peak eff. 1.7V:1.05V     | 91.1%              |  |

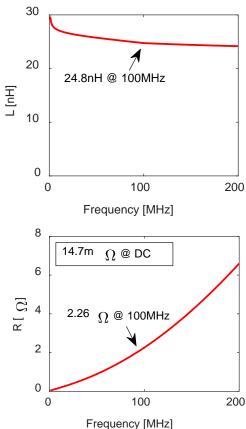

#### **Power Losses**

- □ 1.7/1V 5A Load Current (50% Load)

- 25nH inductance/phase

- 22MHz

- Ferrite Core: 47% FET; 28% Inductor (DC: 18% AC: 10%); 25% PDN

- Air Core: 29% FET; 56% Inductor (DC: 51% AC: 5%); 15% PDN

Magnetic core increases inductance density and lowers DC resistance

Nov. 1, 2019

S. Mueller, Member, M.L. F. Bellaredj, A. K. Davis, P. A. Kohl, and M. Swaminathan, Design Exploration of Package-Embedded Inductors for High Efficiency Integrated Voltage Regulators", IEEE Trans. CPMT, Accepted, 2018.

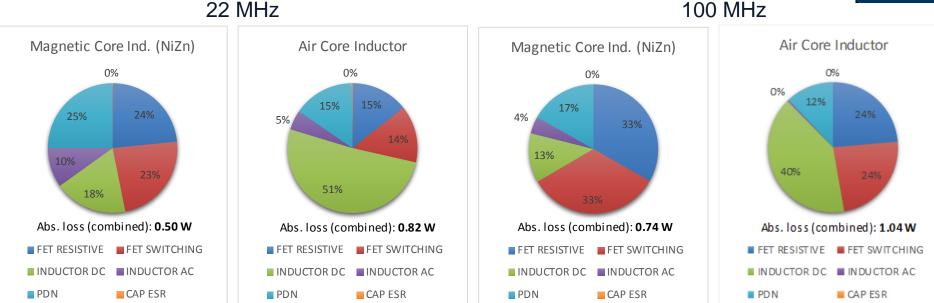

### **Impact of Heating on DC Loss**

□ Impact of inductor heating on overall efficiency [6]:

#### **5V:1V** conversion

- $\rightarrow$  9% of overall loss related to resistance ("inductor DC" and "PDN")

- → Inductor heating changes overall efficiency at 100 MHz from 70.5% to 70.2% (small)

- $\rightarrow$  17% of overall loss related to resistance ("inductor DC" and "PDN")

- → Inductor heating changes overall efficiency at 100 MHz from 86.7% to 86.4% (small)

[6] Modeling and Design of System-in-Package Integrated Voltage Regulator with Thermal Effects, S. Mueller, A. K. Davis,

M. L. F. Bellaredj, A. Singh, K. Z. Ahmed, S. Mukhopadhyay, P. A. Kohl, M. Swaminathan, Y. Wang, J. Wong, S. Bharathi, Y. Mano,

A. Beece, B. Fasano, H. Fathi Moghadam and D. Draper, To be presented at EPEPS, CA, Oct. 23-26, 2016

#### **Recent Work**

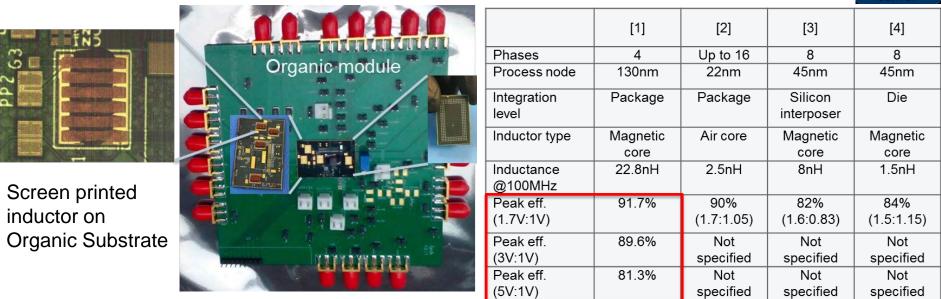

[1] S. Mueller et al, Design Exploration of Package-Embedded Inductors for High Efficiency Integrated Voltage Regulators", IEEE Trans. CPMT, 2018.

[2] E. A. Burton et al., "FIVR - Fully integrated voltage regulators on 4th generation Intel(R) CoreTM SoCs," in 2014 Twenty-Ninth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), 2014.

[3] K. Tien et al., "An 82%-efficient multiphase voltage-regulator 3D interposer with on-chip magnetic inductors,"

in 2015 Symposium on VLSI Technology (VLSI Technology), 2015.

[4] H. K. Krishnamurthy et al., "20.1 A digitally controlled fully integrated voltage regulator with on-die solenoid inductor with planar magnetic core in 14nm tri-gate CMOS," in 2017 IEEE International Solid-State Circuits Conference (ISSCC), 2017. Courtesy: PDES, GT & JUMP-SRC (ASCENT) PwrPACK Workshop 2019

### **Machine Learning for IVR Optimization**

|                    | Hand Tuned           | Non-Linear            | GP-UCB                  | IMGPO                  | тѕво                 |

|--------------------|----------------------|-----------------------|-------------------------|------------------------|----------------------|

| Inductor<br>Area   | 11.3 mm²<br>(+56.1%) | 25.19 mm2<br>(+79.6%) | 5.18 mm2<br>(%0.4)      | 6.64 mm2<br>(%28.1)    | 5.16 mm <sup>2</sup> |

| Peak<br>Efficiency | 79.4%                | 78.6%                 | 84.9%                   | 84.4%                  | 85.1%                |

| CPU Time           | N/A                  | >185 min<br>(+72.9%)  | 117.33 min<br>(+57.4 %) | 115.6 min<br>(+56.7 %) | 50.1 min             |

*Hand Tuned:* S. Mueller *et al.*, "Design of High Efficiency Integrated Voltage Regulators with Embedded Magnetic Core Inductors," ECTC'16. *Optimized: H. M. Torun et al.* "A Machine Learning based Global Optimization Algorithm and its Application to Integrated Systems". TVLSI '18

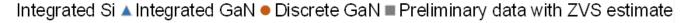

#### **Future Power Delivery Solutions**

HIGH VOLTAGE DC CONVERTER STATE OF THE ART

Georgia Tech

- □ GaN Converter: Up to 10x higher switching frequency at comparable efficiency

- Breakthrough in p-channel GaN FinFET with record on-current a key enabler for GaN-CMOS

- Opportunity: GaN Buck Converters w/ Magnetics for 48V/1V Conversion

Nov. 1, 2019

#### Integrated Voltage Regulators (revisited)

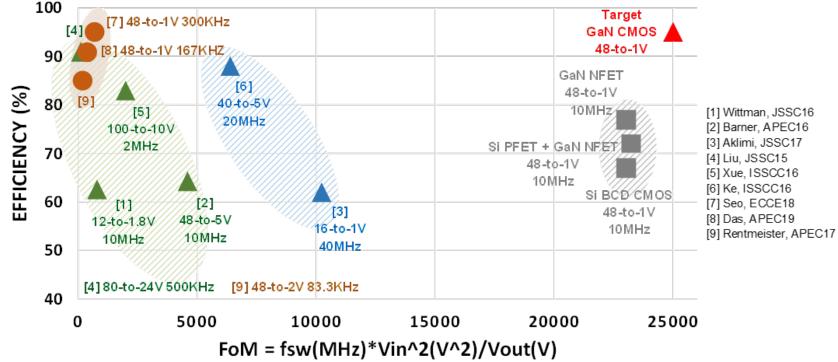

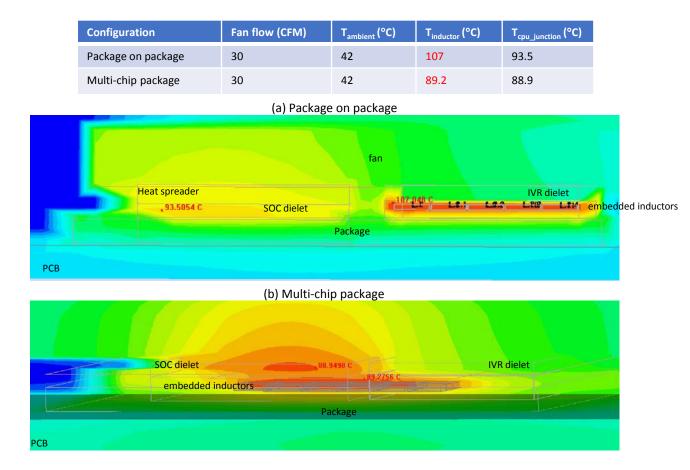

### **Thermal Management**

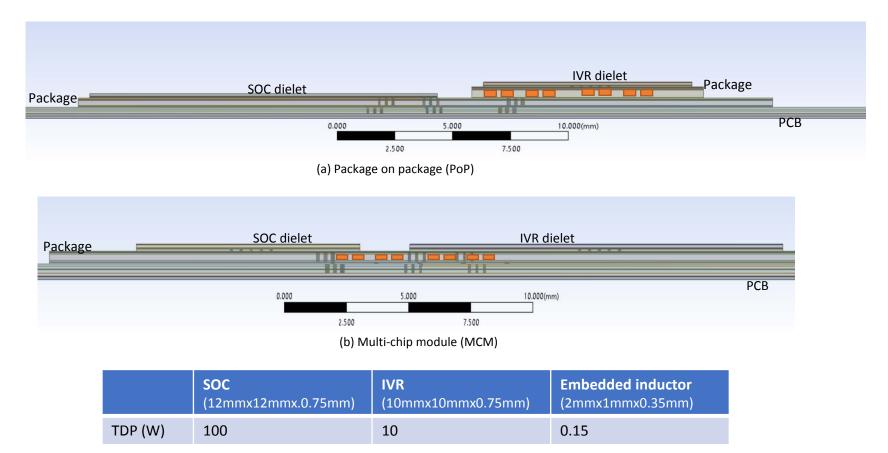

Two heterogeneous architectures being explored

Inductors embedded either in a package or in the substrate of the multi-chip package

### **Thermal Coupling and Joule Heating major issues**

Embedded inductors reach high temperatures in the range of 89-107C

Joule heating <u>neglected</u> here. Inductor temperature expected to increase

### Summary

- Integrated Voltage Regulators (IVR) can lead to significant energy savings

- □ Requires integrated integrated magnetics and dielectrics

- Thermal management critical

- Heterogeneous Integration is the way forward (for various reasons)!

18

Georgia Institute of Technology