# Electrical and Thermal Packaging Challenges for GaN Devices

Paul L. Brohlin

**Texas Instruments Inc.**

October 3, 2016

#### **Outline**

- Why GaN?

- Hard-Switching Losses

- Parasitic Inductance Effects on Switching

- Thermal Challenges of Surface Mount Packages

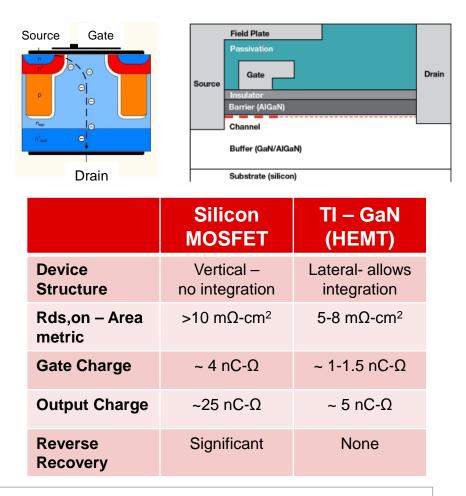

## Why GaN?

- Zero reverse-recovery enables efficient hard-switched CCM converters

- Low output capacitance reduces switch charging losses enabling faster switching speeds

- Low input capacitance reduces gate drive losses enabling higher switching frequency

- Higher switching speeds reduce transformers, inductors, and capacitors size

- Lateral structure enables integration

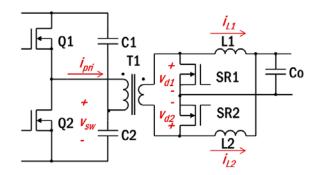

### Why GaN? - 48V to POL

- GaN enables single stage efficient hardswitched POL converter

- Single conversion

- reduces component count in half

- ~3x power density improvement

- Hard-switched topology improves transient response

**48V – 12V Bus Converter 12V** 92-97% Efficient

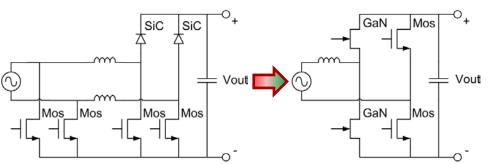

## Why GaN? – CCM Totem Pole PFC

- GaN enables CCM Totem Pole PFC

- No Qrr

- Low switching losses

- GaN enables higher switching frequency

- Reduces inductor size

- CCM Totem

- Lower components

- 30% higher power density

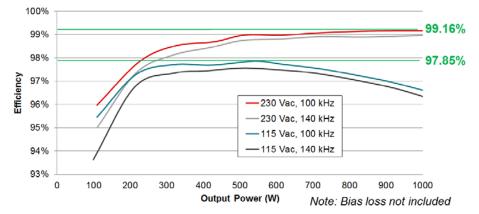

#### 1kW Totem Pole PFC

#### Outline

- Why GaN?

- Hard-Switching Losses

- Parasitic Inductance Effects on Switching

- Thermal Challenges of Surface Mount Packages

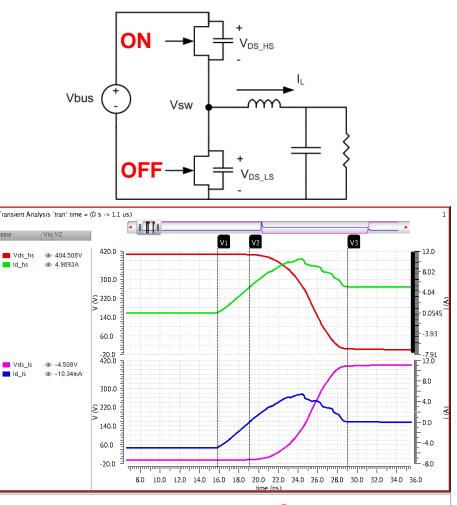

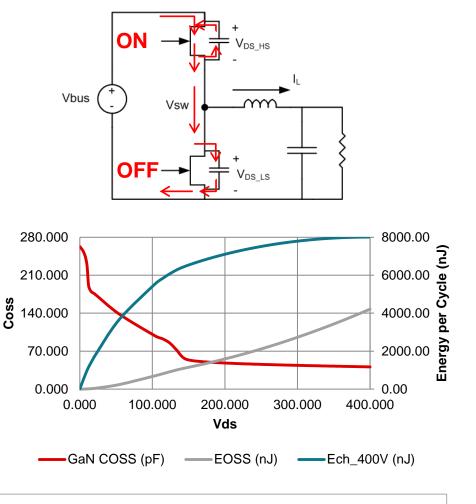

In CCM with positive inductor current, the high-side device dominates the switching losses. Turning on the high-side device faster will reduce the losses due to the inductor conducted through the high-side device during  $t_1 - t_2$  and  $t_2 - t_3$ . E<sub>oss</sub> and E<sub>ch</sub> are determined by C<sub>oss</sub> and Vbus.

**High Side Loss:**

$$P_{hs} = V_{bus} * \frac{I_{ind}}{2} * \frac{t_{1_{2}}}{\tau} + \frac{V_{bus}}{2} * I_{ind} * \frac{t_{2_{3}}}{\tau} + f_{sw} * (E_{oss} + E_{ch})$$

Low-Side Loss:

$$P_{ls} = V_{ds_3q} * \frac{I_{ind}}{2} * \frac{t_{1_2}}{\tau}$$

In CCM with positive inductor current, the high-side device dominates the switching losses. Turning on the high-side device faster will reduce the losses due to the inductor conducted through the high-side device during  $t_1 - t_2$  and  $t_2 - t_3$ . E<sub>oss</sub> and E<sub>ch</sub> are determined by C<sub>oss</sub> and Vbus.

**High Side Loss:**

$$P_{hs} = V_{bus} * \frac{I_{ind}}{2} * \frac{t_{1}}{\tau} + \frac{V_{bus}}{2} * I_{ind} * \frac{t_{2}}{\tau} + f_{sw} * (E_{oss} + E_{ch})$$

Low-Side Loss:

$$P_{ls} = V_{ds_3q} * \frac{I_{ind}}{2} * \frac{t_{1_2}}{\tau}$$

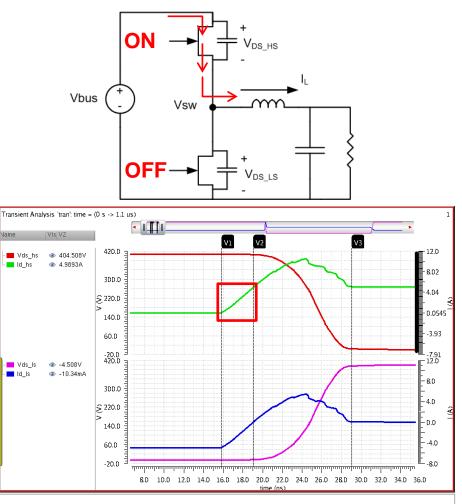

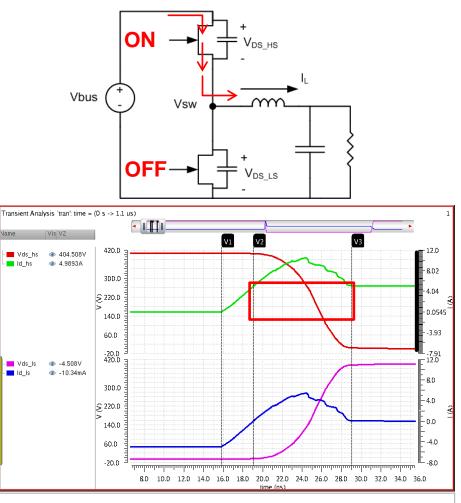

In CCM with positive inductor current, the high-side device dominates the switching losses. Turning on the high-side device faster will reduce the losses due to the inductor conducted through the high-side device during  $t_1 - t_2$  and  $t_2 - t_3$ . E<sub>oss</sub> and E<sub>ch</sub> are determined by C<sub>oss</sub> and Vbus.

High Side Loss:

$$P_{hs} = V_{bus} * \frac{I_{ind}}{2} * \frac{t_{1_{2}}}{\tau} + \frac{V_{bus}}{2} * I_{ind} * \frac{t_{2_{3}}}{\tau} + f_{sw} * (E_{oss} + E_{ch})$$

Low-Side Loss:

$$P_{ls} = V_{ds_3q} * \frac{I_{ind}}{2} * \frac{t_{1_2}}{\tau}$$

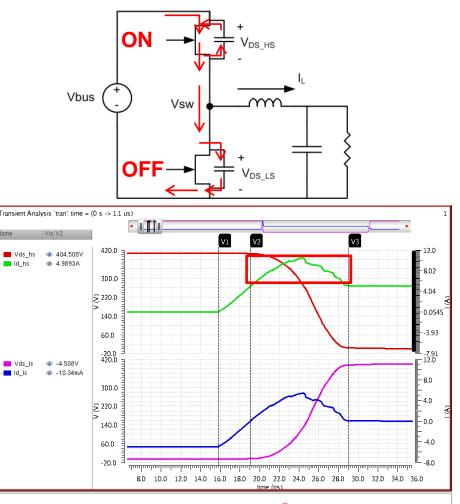

In CCM with positive inductor current, the high-side device dominates the switching losses. Turning on the high-side device faster will reduce the losses due to the inductor conducted through the high-side device during  $t_1 - t_2$  and  $t_2 - t_3$ . E<sub>oss</sub> and E<sub>ch</sub> are determined by C<sub>oss</sub> and Vbus.

High Side Loss:

$$P_{hs} = V_{bus} * \frac{I_{ind}}{2} * \frac{t_{1}}{\tau} + \frac{V_{bus}}{2} * I_{ind} * \frac{t_{2}}{\tau} + f_{sw} * (E_{oss} + E_{ch})$$

**Low-Side Loss:**

$$P_{ls} = V_{ds_3q} * \frac{I_{ind}}{2} * \frac{t_{1}}{\tau}$$

#### **Eoss vs Ech**

- C<sub>oss</sub> is very non-linear for GaN and most high voltage power devices

- $E_{\rm oss}$  is the energy stored in the  $C_{\rm oss}$  at a defined  $V_{\rm ds}$

$E_{oss} = \int_0^{V_{bus}} C_{oss}(V_{ds}) * V_{ds} \, dV$

- $E_{ch}$  is the energy dissipated in the highside when charging the low-side  $C_{oss}$  $E_{ch} = \int_{0}^{V_{bus}} C_{oss}(V_{ds\_ls}) * (V_{bus} - V_{ds\_ls}) dV$

- $E_{ch} > E_{oss}$  when  $C_{oss}$  is larger at low  $V_{ds}$

- Any parasitic SW node capacitance will sum with C<sub>oss</sub> of the low-side fet

- No snubbers

#### Outline

- Why GaN?

- Hard-Switching Losses

- Parasitic Inductance Effects on Switching

- Thermal Challenges of Surface Mount Packages

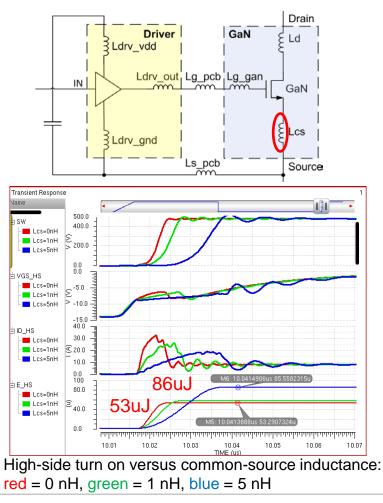

#### **Common Source Inductance**

- Common Source inductance reduces the di/dt during turn-on and turn-off.

- Increases power dissipated during the di/dt ramp

- 5nH common source inductance increases turn-on loss by 60%

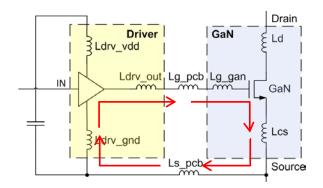

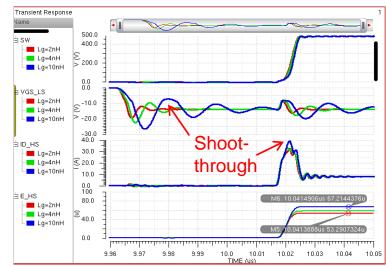

#### **Gate Loop Inductance**

- Gate loop inductance increases the impedance between the gate and the driver.

- Limits the ability to hold off the GaN device during the Vds ramp

- Shoot through increases the power dissipated in the high-side device and can cause it to fail due to SOA.

- Gate loop inductance increases ringing

- Higher stress on gate

- Ringing can cause the device to turn-on/off

- Loop resistance is required to dampen ringing

Low-side hold-off versus gate-loop inductance red = 2 nH, green = 4 nH, blue = 10 nH

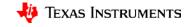

#### **Reduction of Common Source & Gate Loop Inductance**

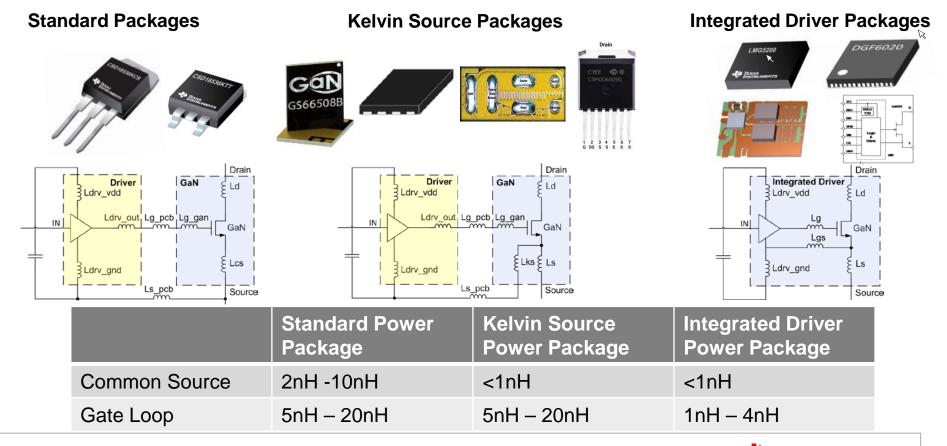

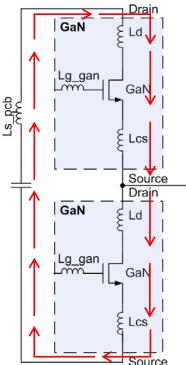

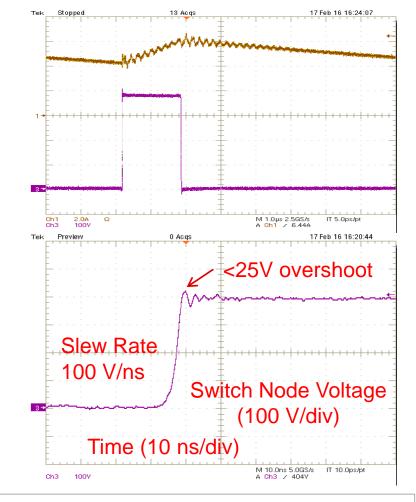

#### **Power Loop Inductance**

- Power loop inductance

- Increases Ringing and EMI

- Increases V<sub>ds</sub> voltage stress

- Increase switching losses

- Package must be designed to enables low power loop inductance PCB layout

- GaN must be switched without snubber to have high efficiency

#### **CCM Switching Waveforms**

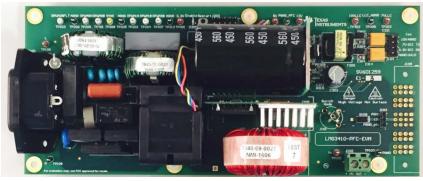

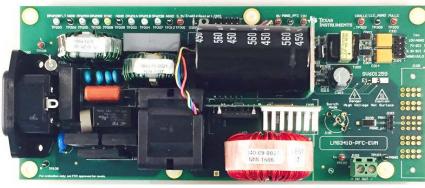

#### LMG3410 HB EVM

1kW Totem Pole PFC

#### **Outline**

- Why GaN?

- Hard-Switching Losses

- Parasitic Inductance Effects on Switching

- Thermal Challenges of Surface Mount Packages

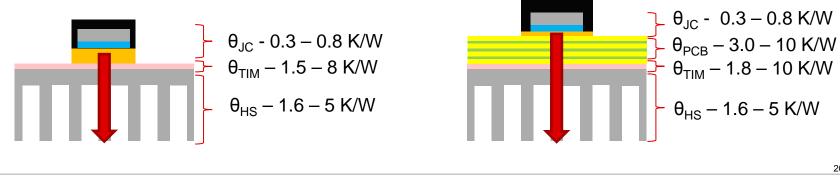

#### **Thermal**

- Power packages need to have good thermal dissipation capability

- GaN has high R<sub>ds\_on</sub> temperature coefficient.

- Lower junction temperature reduces conduction loss

- Surface mount packages do not dissipate power as well as traditional leaded packages

- Heat dissipates through PCB

- Typically have smaller heat spreaders

#### **Thermal Dissipation**

Power dissipation: ~12 W (50C ambient and 110C max junction temperature)

**Power dissipation:** ~7 W (50C ambient and 110C max junction temperature)

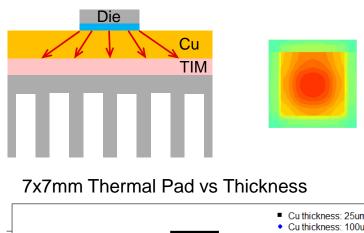

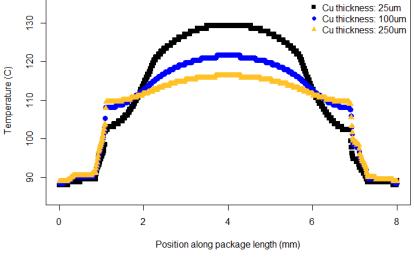

#### **Package Thermal Pad**

- Area of thermal pad must large enough to reduce thermal resistance of TIM

- Thermal pad must have sufficient thickness to spread heat over TIM

$$\Delta T_{TIM} = \frac{P_{diss} \times A_{TIM}}{d_{TIM} \times \lambda_{TIM}}$$

#### **Package Comparison**

| ompai |     |       | V |        |

|-------|-----|-------|---|--------|

|       | GSG | 5516T |   | Source |

|       |     |       |   | Gale   |

| Package              | TO220 | QFN | Bumped<br>Die | Embedded | TOLL | Sintered<br>Dual Cool |

|----------------------|-------|-----|---------------|----------|------|-----------------------|

| Common Source<br>Ind | *     | ++  | ++            | ++       | ++   | ++                    |

| Gate Loop Ind        |       | ++  | ++            | ++       | ++   | +                     |

| Power Loop Ind       |       | ++  | ++            | ++       | ++   | +                     |

| Thermal              | ++    | +   | -             | +        | +    | ++**                  |

| Cost                 | ++    | ++  | ++            | -        | +    |                       |

\* Additional kelvin source pin eliminates common source inductance

\*\* Includes isolation

Drain

#### **Conclusions**

- GaN's lower switching losses enables high efficiency and high density designs

- No reverse recovery

- Low Qoss and Qiss

- Low inductance package is required to realize GaN switching performance

- Low common source inductance to reduce losses during di/dt phases

- Low gate loop inductance to hold device off and reduce gate ringing

- Integrating the driver in the package will minimize gate loop and common source inductance

- Package must enable low power loop inductance PCB layout

- Power loop must be designed without snubbers

- GaN package must have good thermal performance

- Large thick power pad to spread heat and lower TIM drop

- Direct thermal connection to heat sink eliminates PCB thermal resistance

# **Thank You**