# V<sup>1</sup> Control for fast transient response in Power Converters on Chip

Pedro Alou, Jesús A. Oliver and José A. Cobos

Universidad Politécnica de Madrid

CAMPUS DE EXCELENCIA INTERNACIONAL

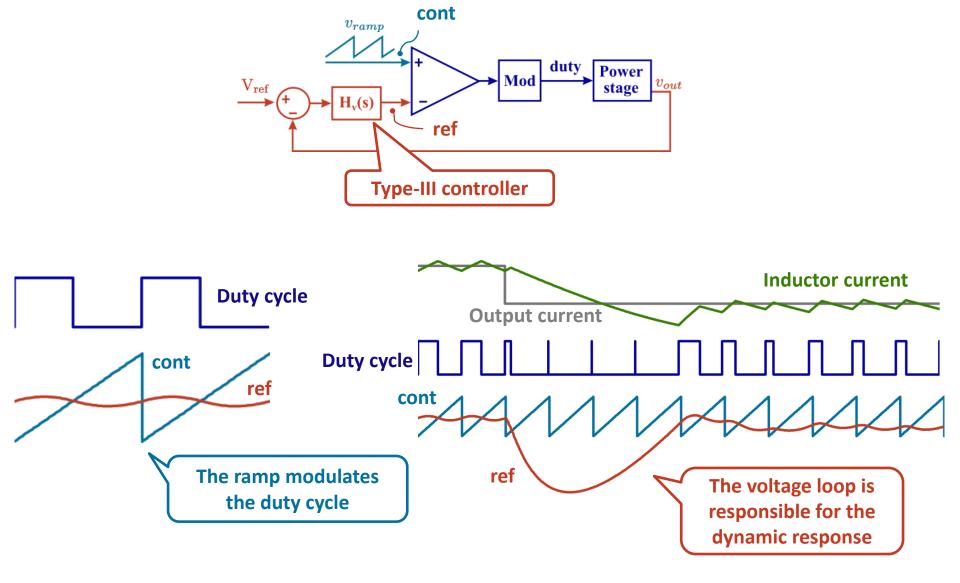

### Introduction: Voltage mode control

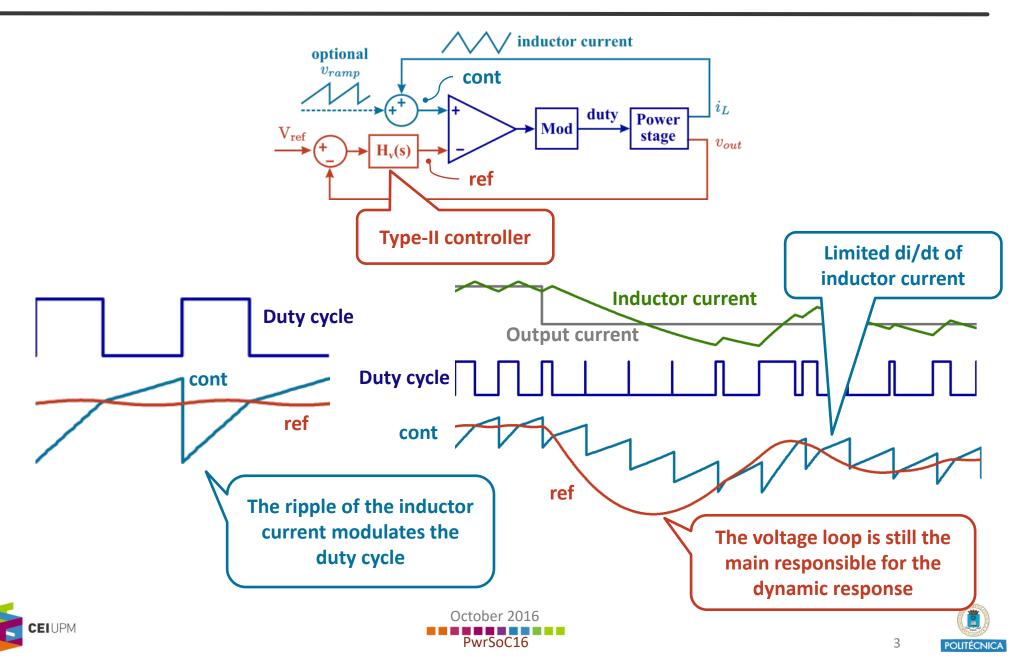

### **Introduction: Current mode control**

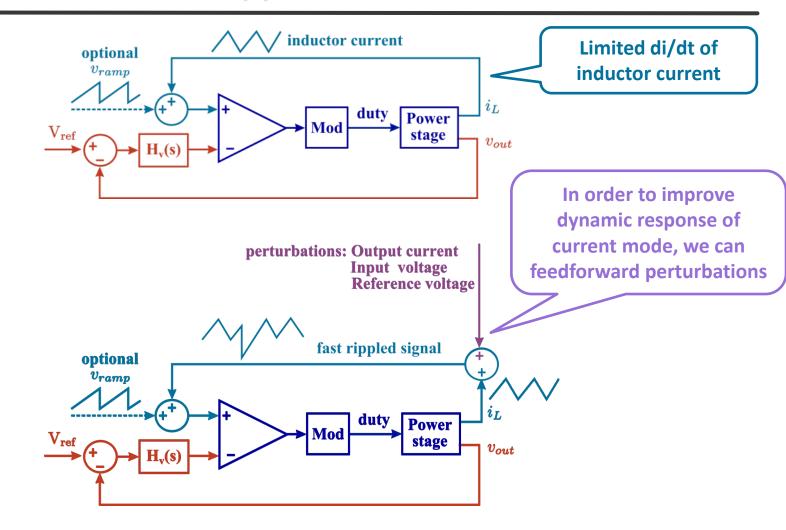

### **Introduction: Ripple-based control**

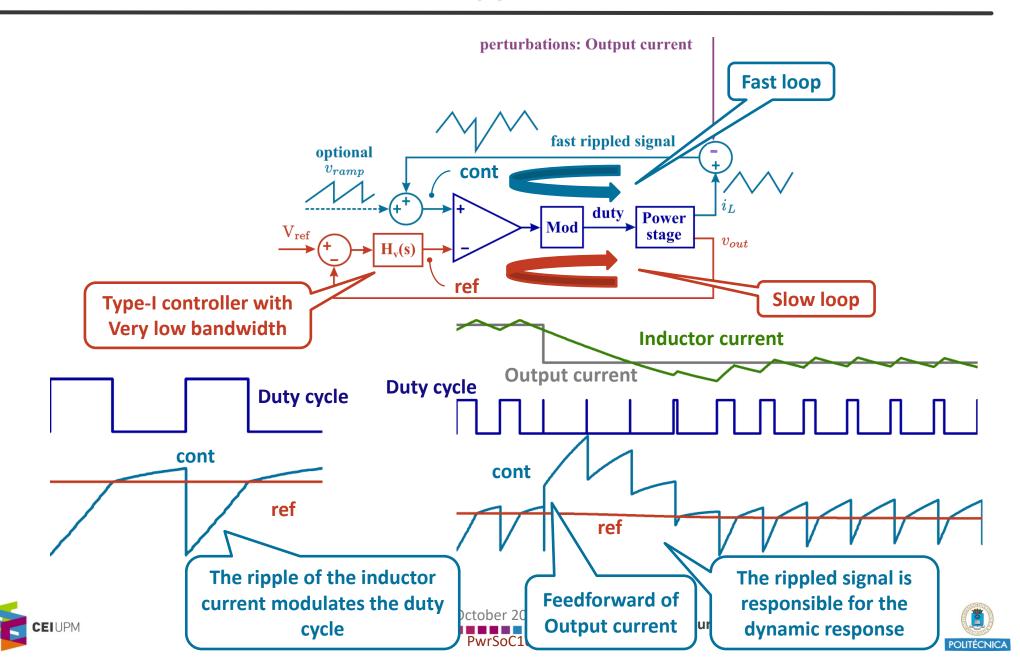

### **Introduction: Ripple-based control**

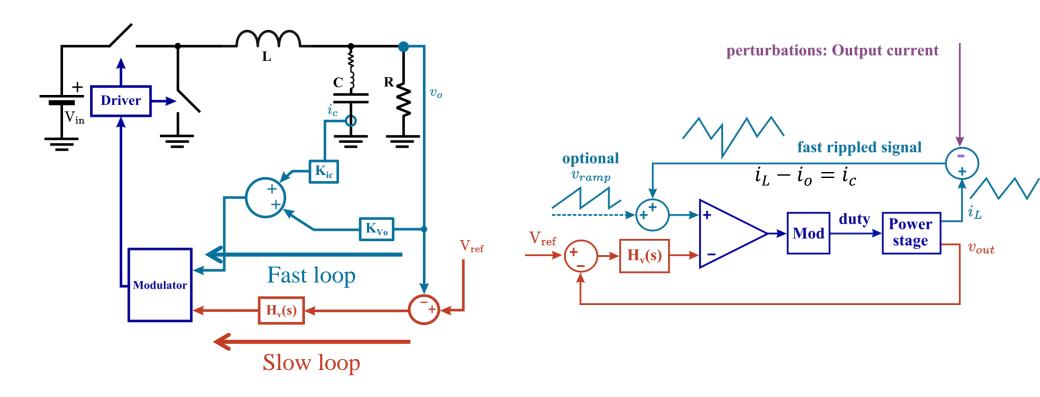

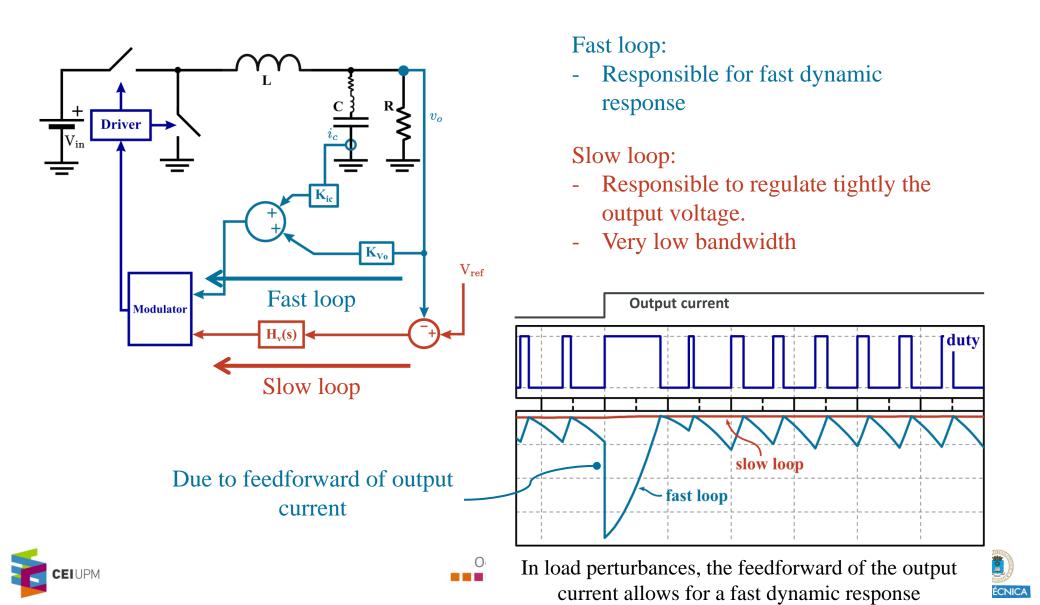

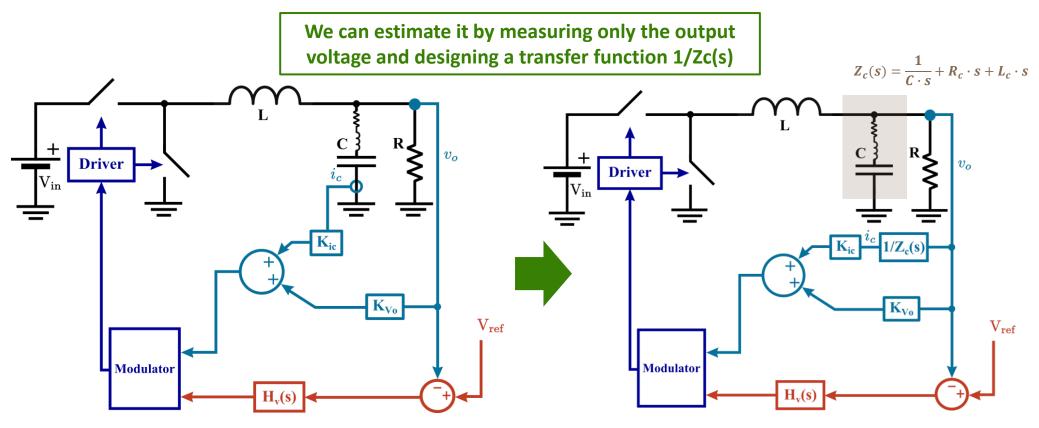

How can we measure the capacitor current?

] M. Del Viejo, P. Alou, J. A. Oliver, O. Garcia, and J. A. Cobos, "V2IC control: A novel control technique with very fast response under load and voltage steps," in 2011 Twenty-Sixth Annual IEEE Applied Power Electronics Conference and *Exposition (APEC)*, 2011, pp. 231–237.

] Y. Yan, P.-H. Liu, F. Lee, Q. Li, and S. Tian, "V2 control with capacitor current ramp compensation using lossless capacitor current sensing," in 2013 IEEE Energy Conversion Congress and Exposition (ECCE), 2013, pp. 117–124.

POLITÉCNICA

Is it possible to replicate  $V^2I_c$  in voltage mode?

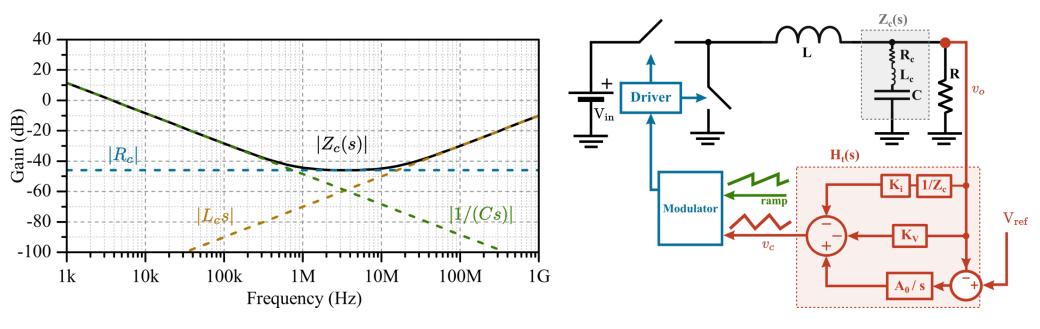

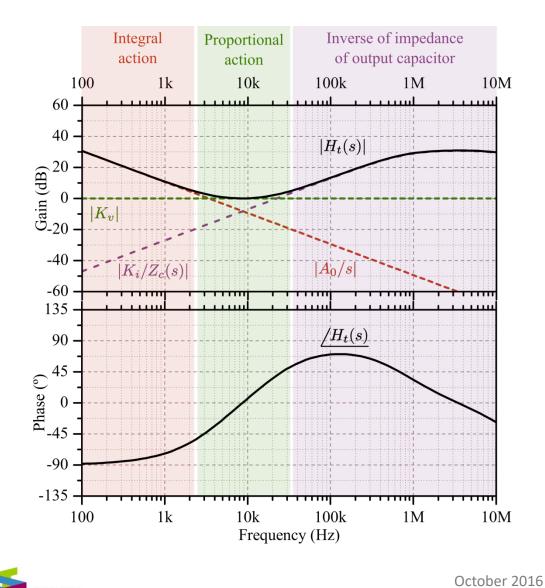

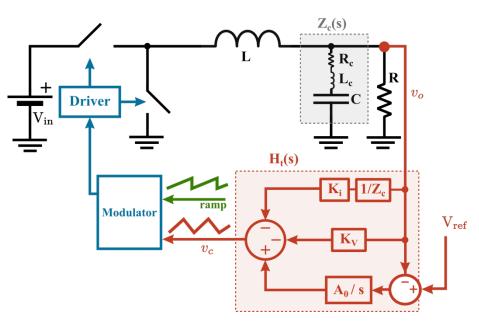

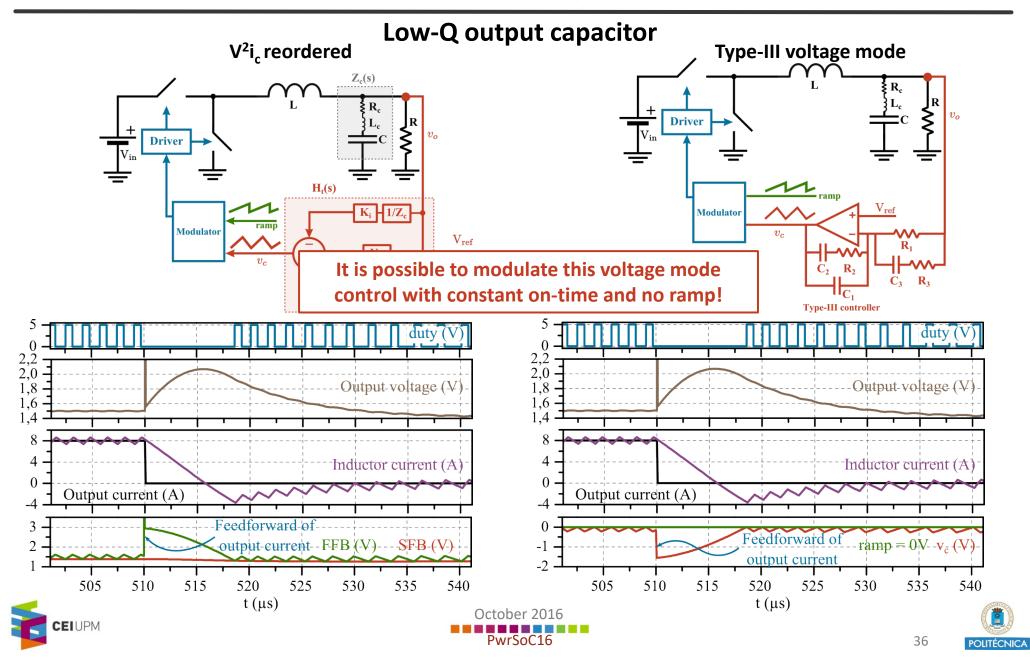

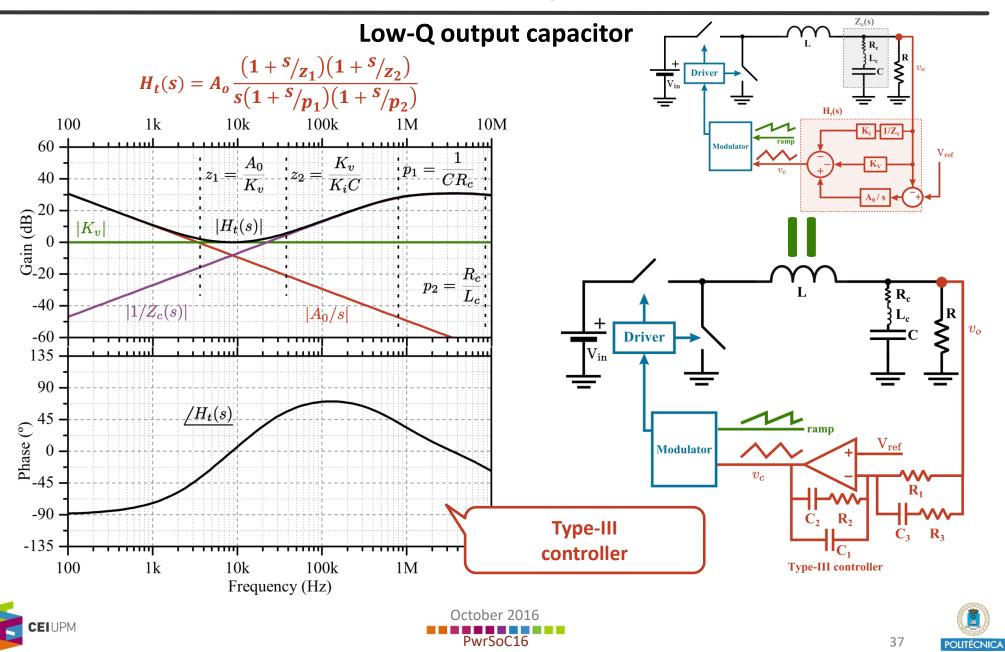

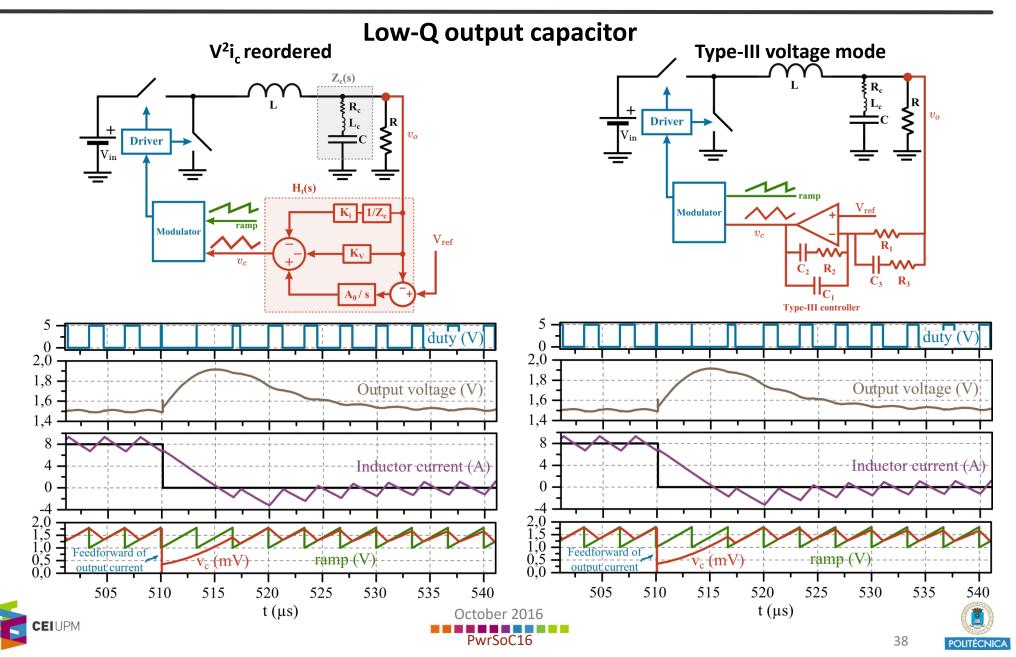

#### Low-Q output capacitor

$$Z_c(s) = \frac{(1 + sCR_c)\left(1 + \frac{sL_c}{R_c}\right)}{Cs}$$

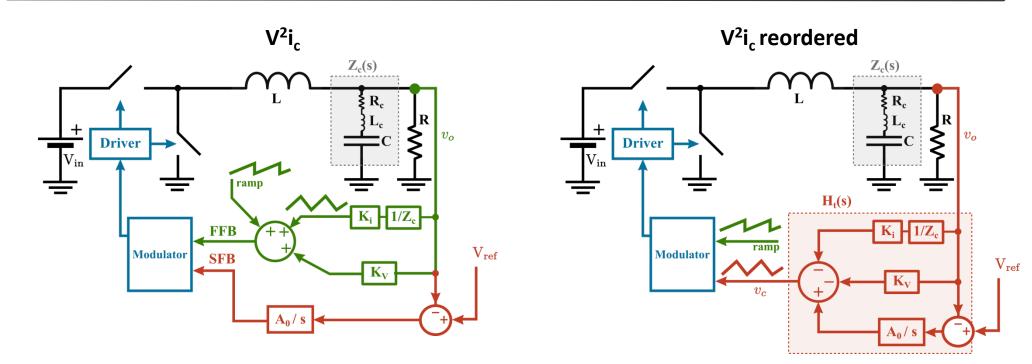

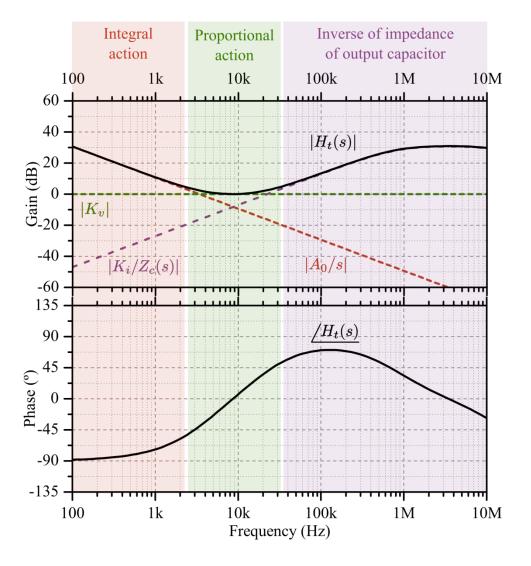

$$H_t(s) = \frac{A_o}{s} + K_v + K_i \frac{1}{Z_c(s)}$$

PwrSoC16

CEIUPM

$$H_t(s) = \frac{A_o}{s} + K_v + K_i \frac{1}{Z_c(s)}$$

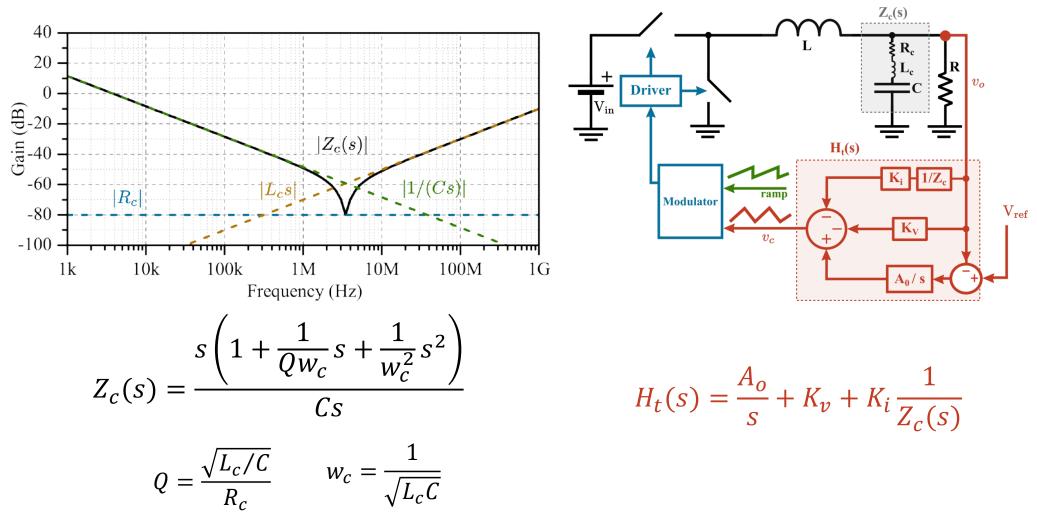

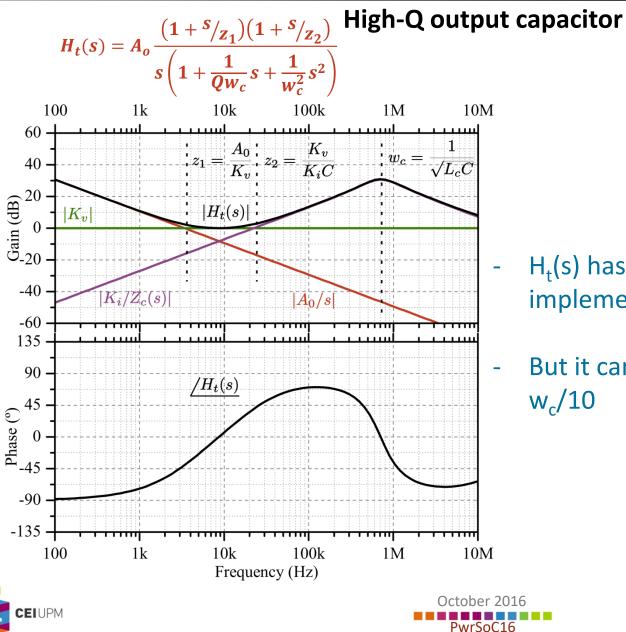

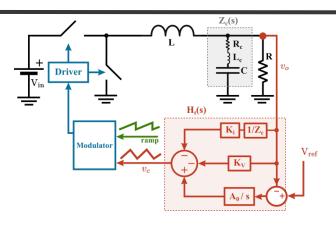

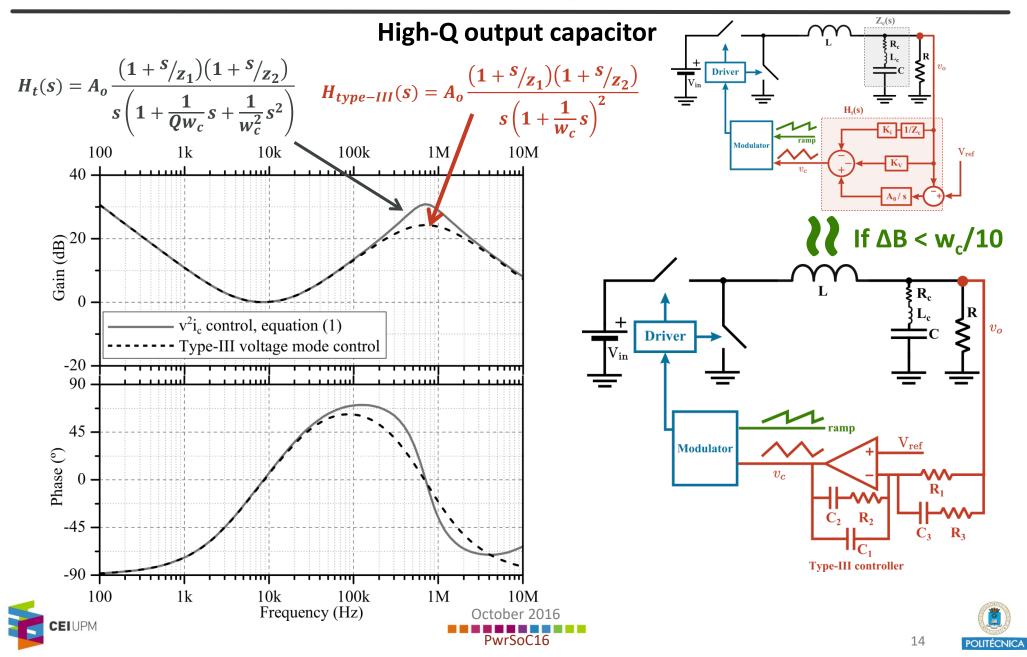

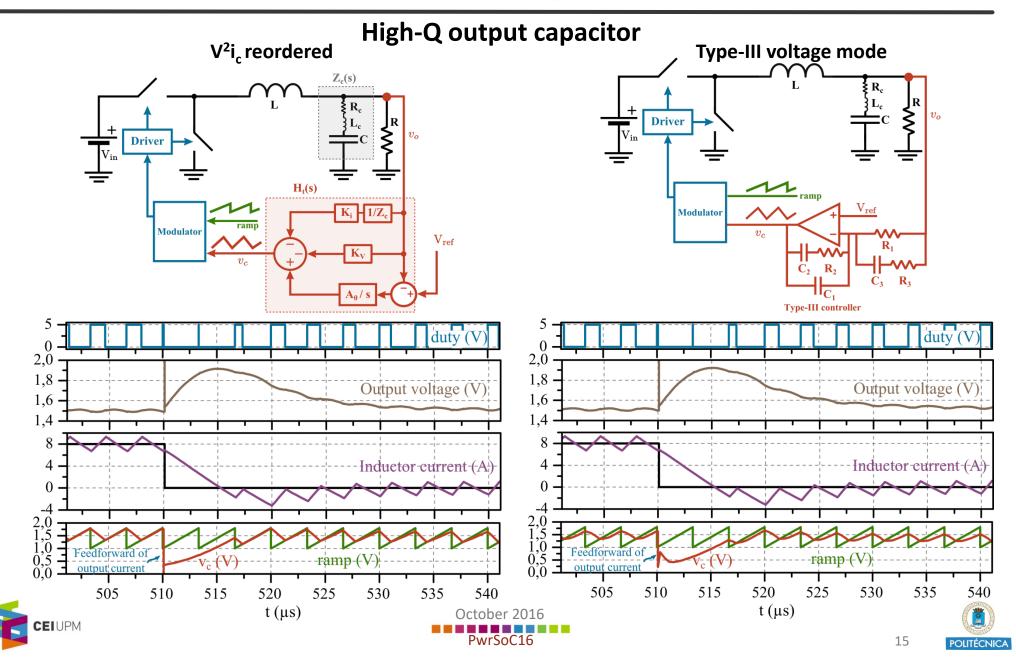

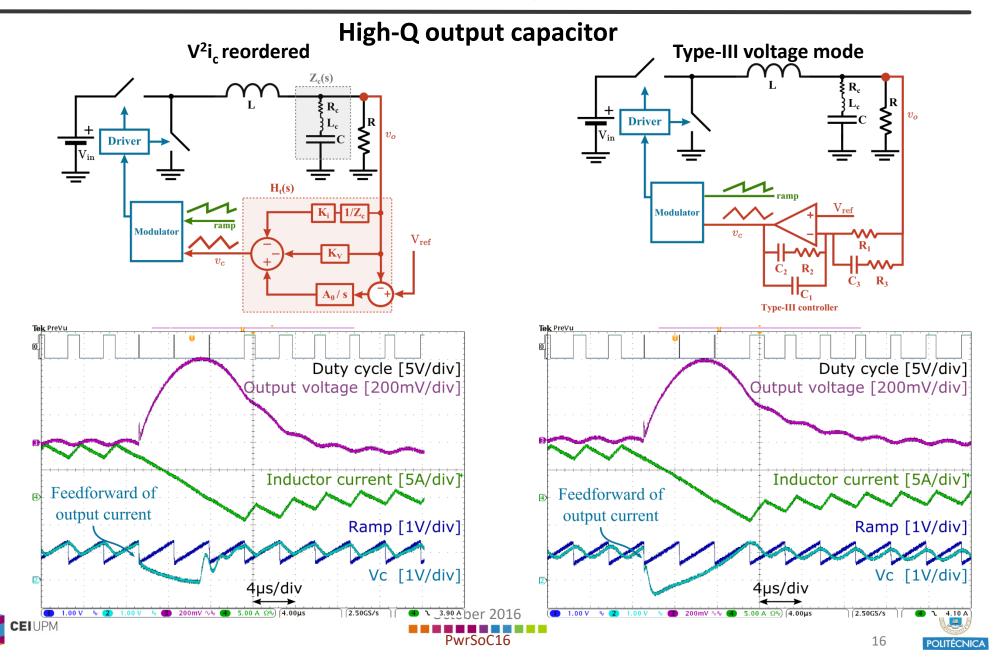

#### **High-Q output capacitor**

POLITÉCNICA

H<sub>t</sub>(s) has complex poles. It cannot be implemented as a type-III controller!

But it can be approximated if  $\Delta B < w_c/10$

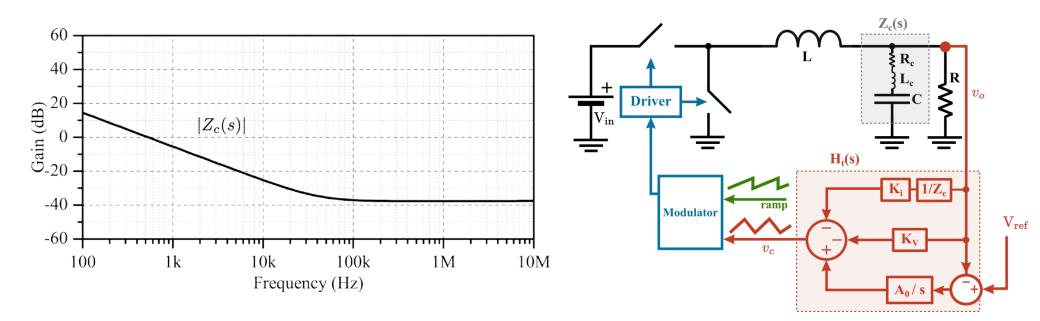

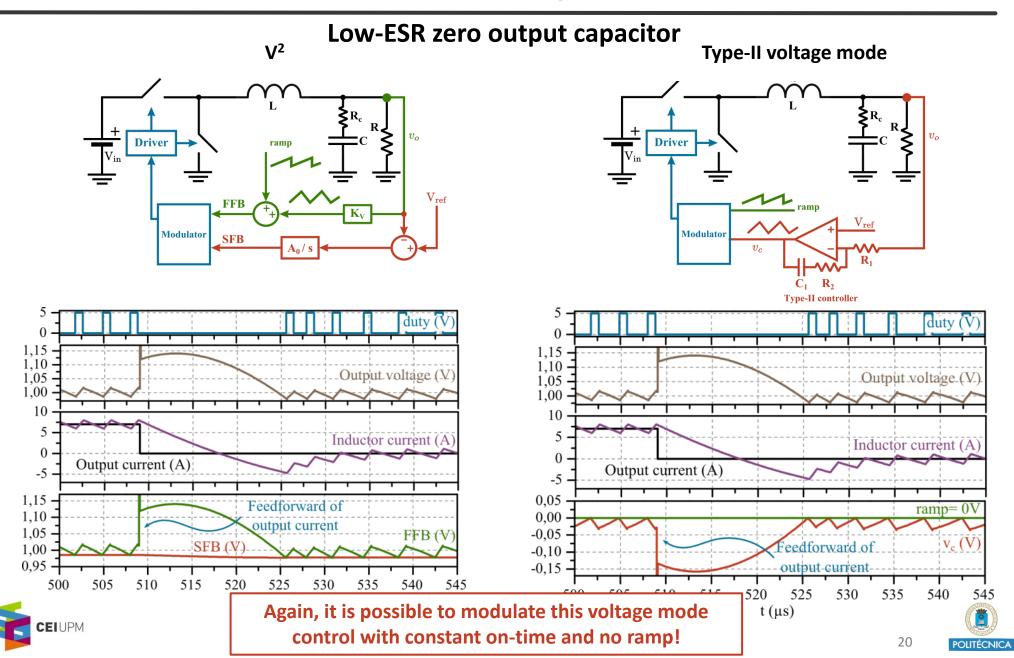

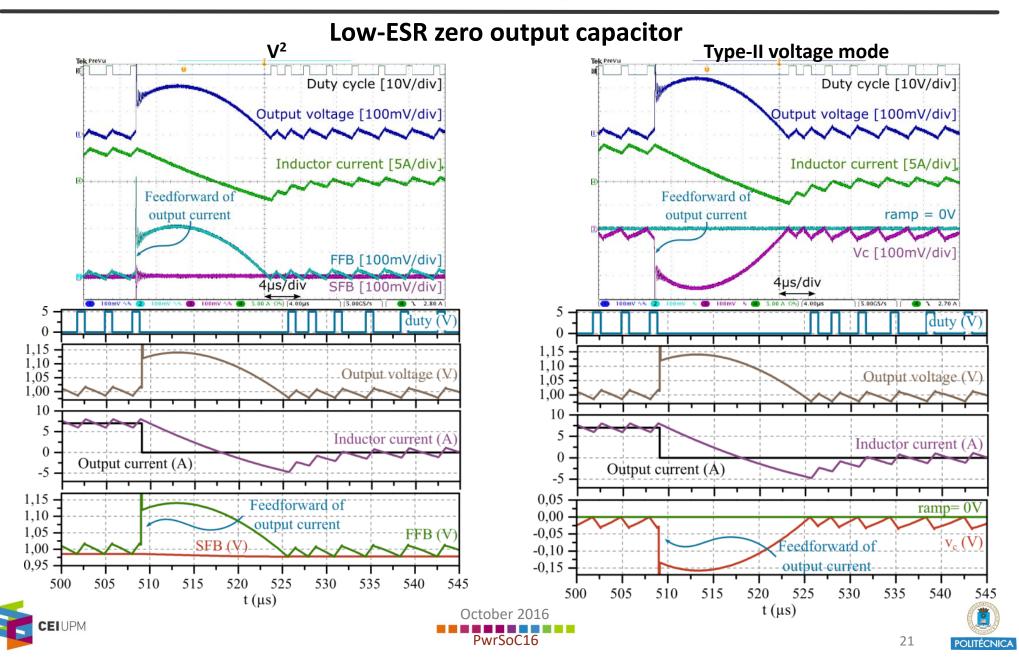

#### Low-ESR zero output capacitor

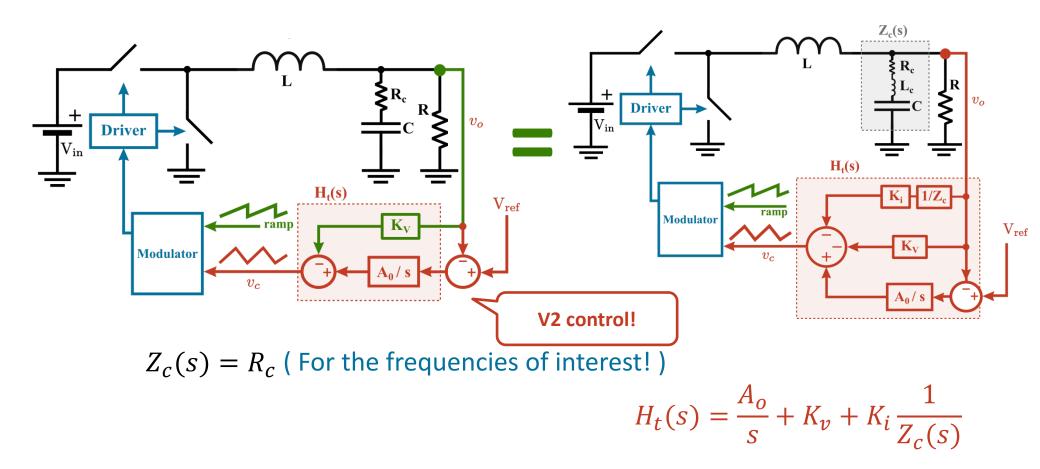

$Z_c(s) = R_c$  (For the frequencies of interest!)

$$H_t(s) = \frac{A_o}{s} + K_v + K_i \frac{1}{Z_c(s)}$$

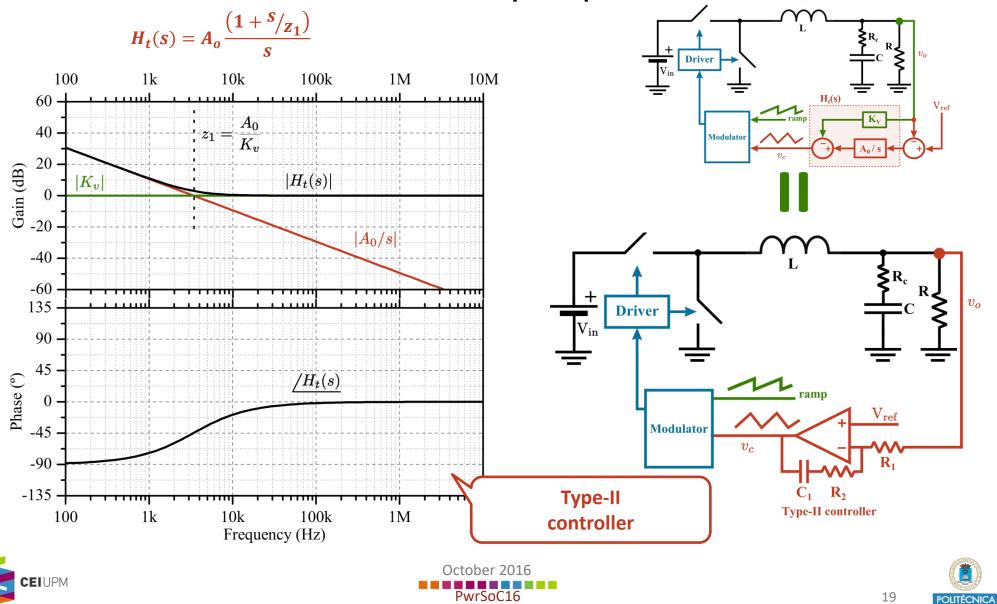

#### Low-ESR zero output capacitor

Low-ESR zero output capacitor

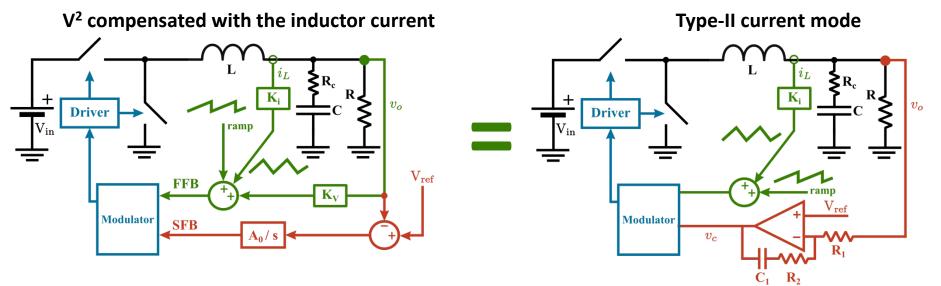

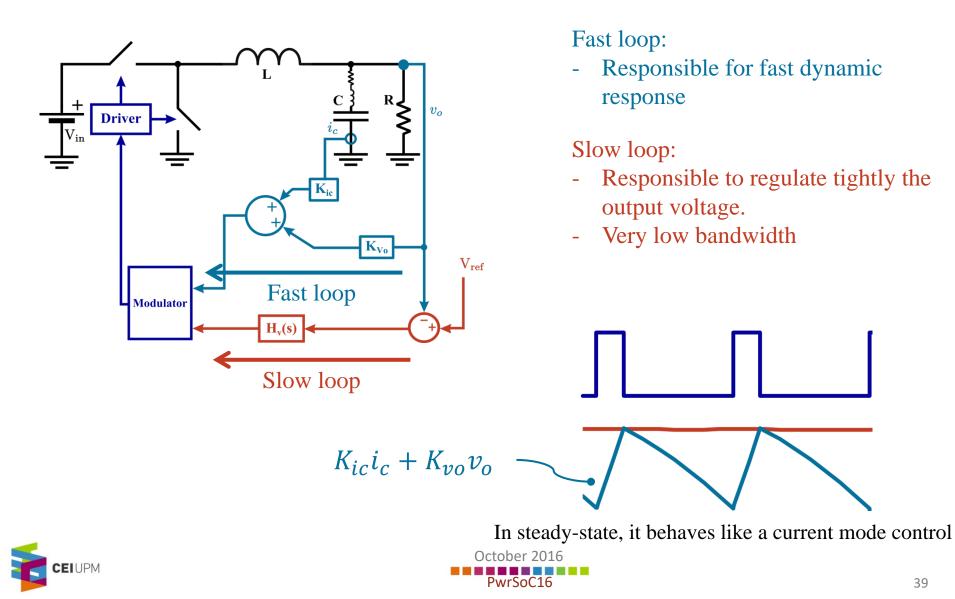

V<sup>2</sup> control compensated with the inductor current

$$H_t(s) = \frac{A_o}{s} + K_v + K_i \frac{1}{Z_c(s)}$$

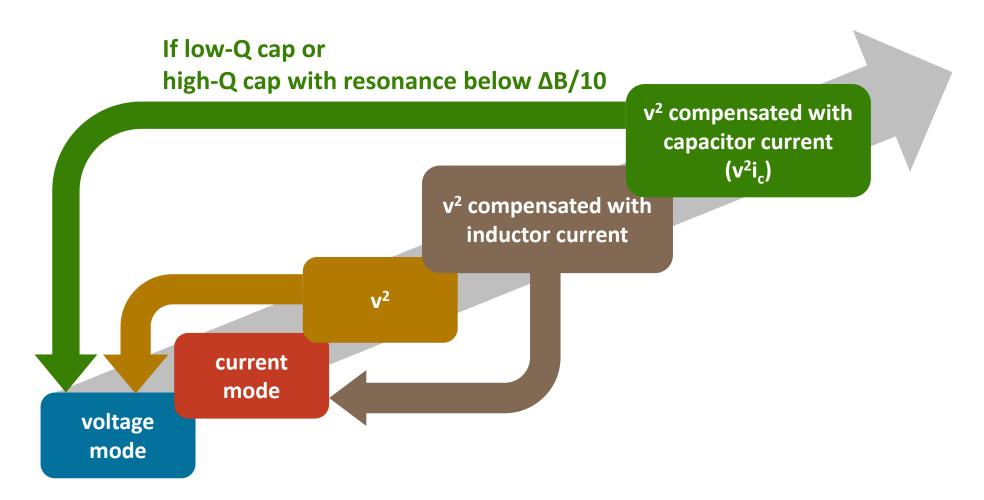

#### POSSIBLE IMPLEMENTATIONS OF H<sub>t</sub> ACCORDING TO OUTPUT CAP

#### Low-Q cap (Q<0.5)

v<sup>2</sup>i<sub>c</sub> type-III voltage mode

#### High-Q cap (Q>0.5)

$\frac{If \Delta B < w_c/10}{v^2 i_c}$ type-III voltage mode (approx)

$\frac{\text{If }\Delta B > w_{c}/10}{v^{2}i_{c}}$

#### Low-ESR zero cap

V<sup>2</sup>, V<sup>2</sup>i<sub>c</sub> , V<sup>2</sup>i<sub>L</sub> and V<sup>1</sup> are just different implementations of H<sub>t</sub>(s).

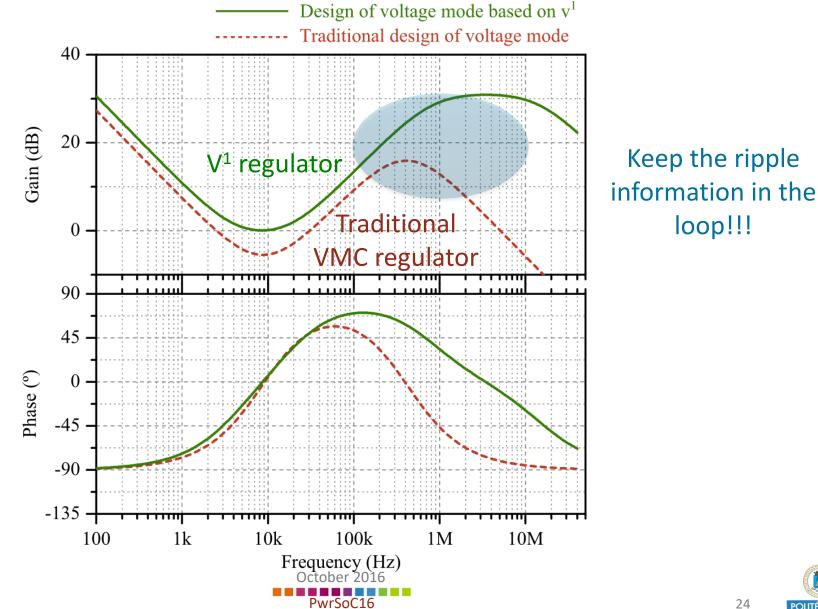

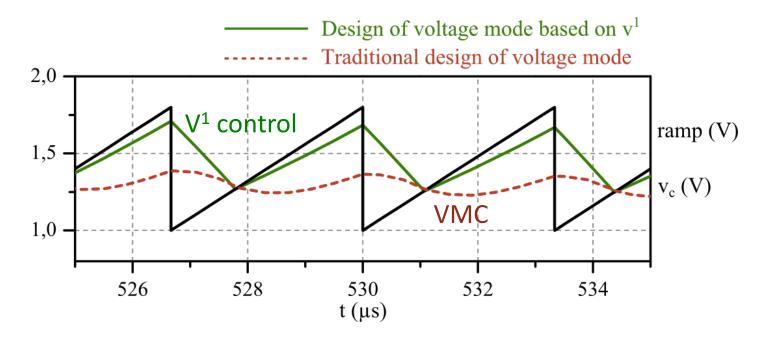

- By using only the output voltage, it is possible to emulate a current mode control with feedforward of output current → V<sup>1</sup> concept

- Keep the ripple information in the loop!!!

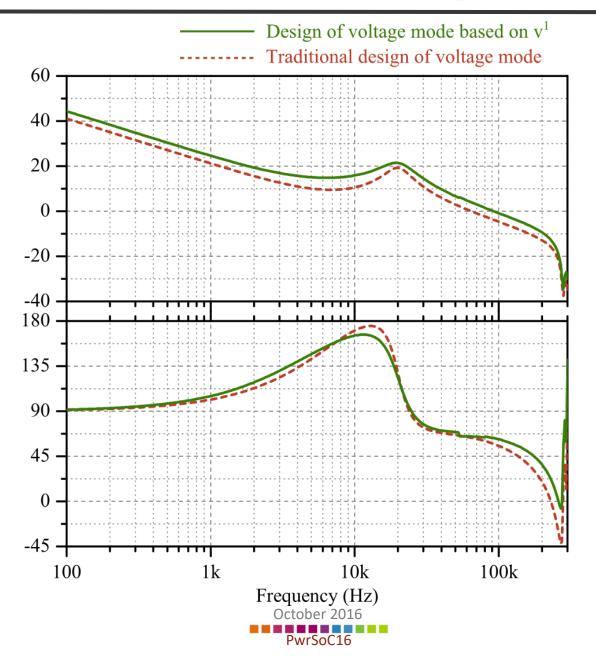

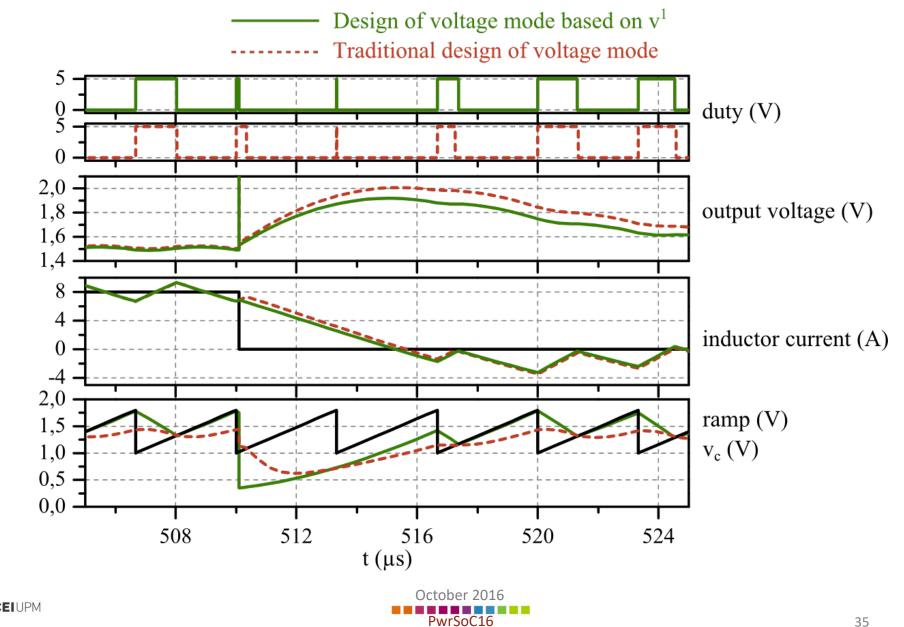

### **Comparison of traditional VMC design and V1 concept**

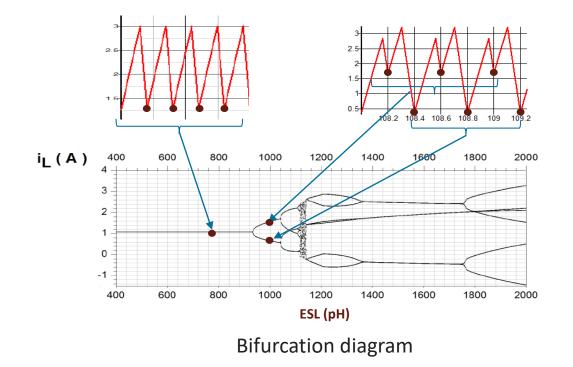

### V1 concept is a ripple based control: subharmonic oscillations!!

... BUT accurate models are needed to design with robustness....

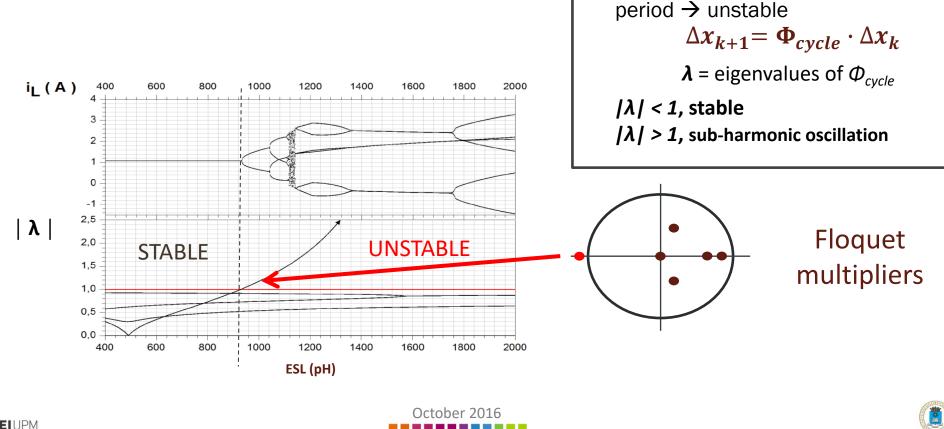

Discrete modelling and Floquet theory

- Robustness analysis and optimization

- High accuracy

Cortes, J.; Svikovic, V.; Alou, P.; Oliver, J.; Cobos, J.; Wisniewski, R., "Accurate analysis of sub-harmonic oscillations of V2 and V2Ic controls applied to Buck converter," Power Electronics, IEEE Transactions on, early access

POLITÉCNICA

# **Floquet theory**

#### **Bifurcation phenomena**

• Sub-harmonic oscillations can be seen as a bifurcation where the system is unable to maintain a T-periodic solution

#### **Equivalences between controls**

# **Floquet theory**

#### **Bifurcation phenomena**

Sub-harmonic oscillations can be seen as a bifurcation where the system is unable to 0 maintain a T-periodic solution

Stability

theory.

0

is analyzed

If a perturbation grows over a

PwrSoC16

POLITÉCNICA

Floquet

by

### Floquet Theory: robust design regarding all the tolerances

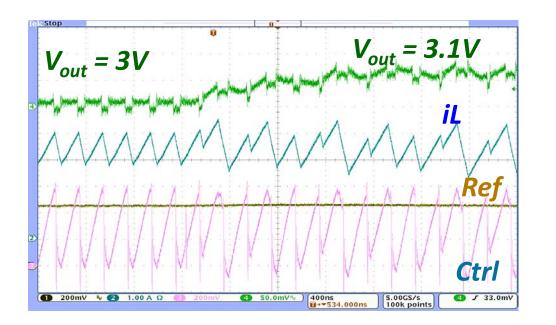

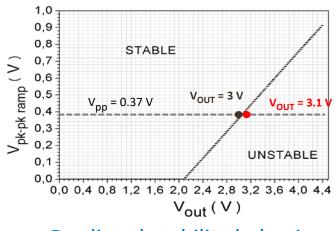

Predicted stability behavior

The Floquet theory predicts accurately the oscillation!

$V_{out} = 3V \rightarrow \lambda = -0.966$

$V_{out} = 3.1V \rightarrow \lambda = -1.06$

**Out of unit circle!**

October 2016

PwrSoC16

$$H_t(s) = \frac{A_o}{s} + K_v + K_i \frac{1}{Z_c(s)}$$

#### POSSIBLE IMPLEMENTATIONS OF H<sub>t</sub> ACCORDING TO OUTPUT CAP

#### Low-Q cap (Q<0.5)

v<sup>2</sup>i<sub>c</sub> type-III voltage mode

#### High-Q cap (Q>0.5)

$\frac{If \Delta B < w_c/10}{v^2 i_c}$ type-III voltage mode (approx)

$\frac{\text{If }\Delta B > w_c/10}{v^2 i_c}$

#### Low-ESR zero cap

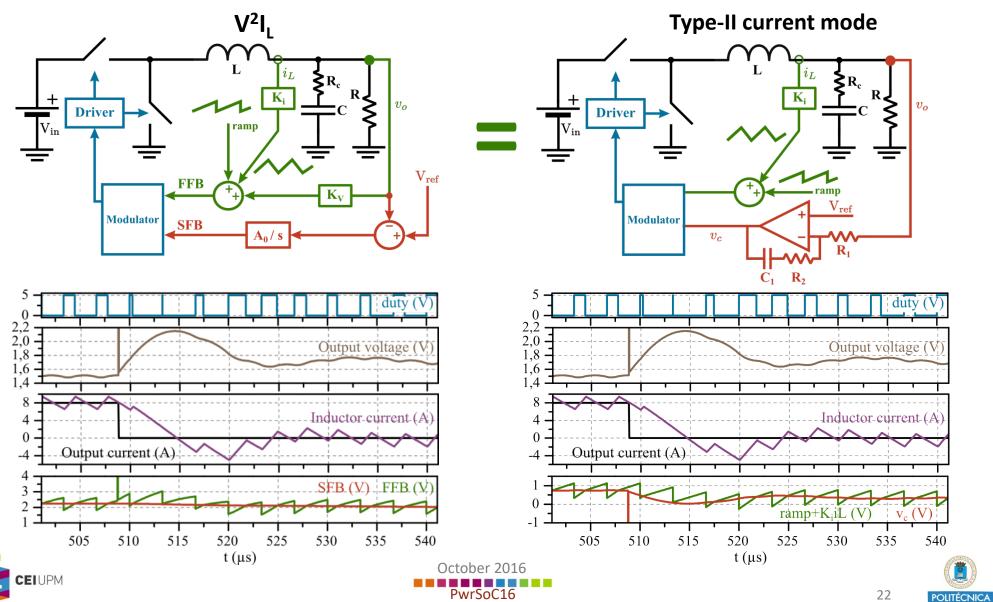

And what happens to the v<sup>2</sup> control compensated with the inductor current?

- As seen, the v<sup>2</sup> control is equivalent to a type-II control. In a Buck converter, the control relies on the ESR of the output capacitor to boost the phase of the loop gain.

- If the ESR is not dominant in the output voltage ripple, the phase margin is poor because the type-II controller cannot add any phase and the response is oscillatory or unstable.

- The v<sup>2</sup> control is commonly compensated with the inductor current for improved response for nondominant ESR capacitors. What we are essentially doing is turning the v<sup>2</sup> control into a conventional current mode control that can now be regulated with a type-II controller.

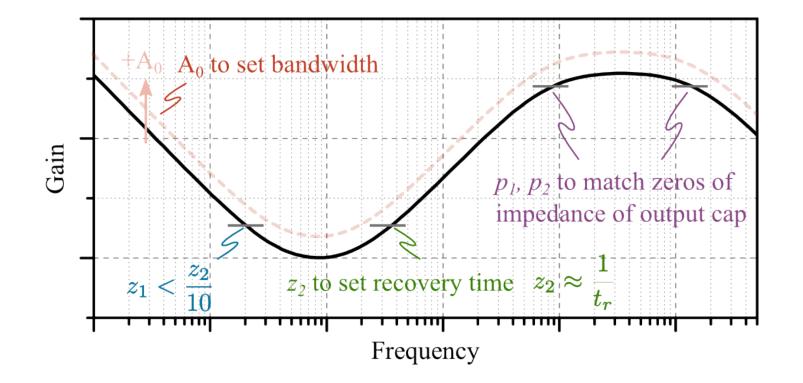

### v<sup>1</sup> concept: design guidelines

Proposed design of a type-III voltage mode control based on the v<sup>1</sup> concept

### **Comparison of traditional VMC design and V1 concept**

### **Comparison of traditional VMC design and V1 concept**

POLITÉCNICA