### 2016 International Workshop on Power Supply On Chip (PwrSoC 2016)

# A Novel Silicon-Embedded Transformer for System-in-Package Power Isolation\*

#### Rongxiang Wu<sup>1</sup>, Niteng Liao<sup>1</sup>, Xiangming Fang<sup>2</sup>, Johnny K.O. Sin<sup>3</sup>

<sup>1</sup>University of Electronic Science and Technology of China <sup>2</sup>Shenzhen CoilEasy Technologies, Co. Ltd. <sup>3</sup>Hong Kong University of Science and Technology

\* This work was supported by the National Natural Science Foundation of China under grant 61306101

Madrid, October 2016

## Signal & Small Power Isolation Applications

Industrial: Sensor Data Bus Motor Drive

Automobile: Motor Drive Battery Manage

Power Generation:

PV Inverter Wind Turbine

**Telecom:** Data Bus PoE

Medical: Patient Monitor Sensor Probe

Others:

Instrumentation

Consumer

Aerospace

#### R. Wu

## Small Power Isolation (<2W)</p>

## >Allow Simple Power Supply for Signal Isolation Channels

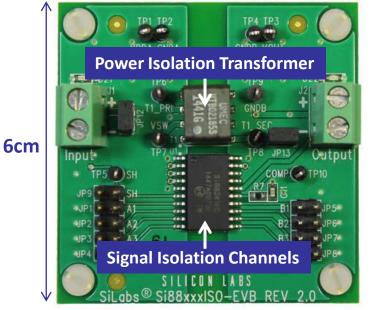

## **Discrete Transformer Solution**

- 2μH/0.05Ω

- ✓ 200 kHz to 800 kHz

- ✓ Up to 78% dc-dc efficiency

- Low integration level

- Large solution size

- 🛚 High system cost

Ref: Silicon Labs, Si88xxxISO-EVB **R. Wu**PwrSoC'16

## Small Power Isolation (<2W)</p>

>Allow Simple Power Supply for Signal Isolation Channels

Ref: Analog Devices, B. Chen, PwrSoC, 2008 R. Wu PwrSoC'16

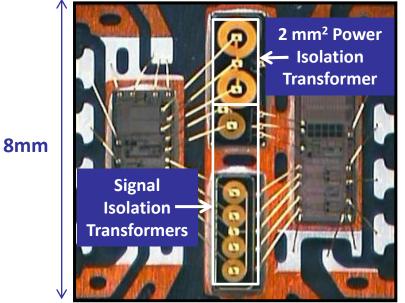

## **On-Chip Transformer Solution**

- ✓ System-in-package integration

- ✓ Small solution size

- Low system cost

- × 16nH/1.6Ω

- 🞽 170 MHz

- Up to 34% dc-dc efficiency

■ Needed: High Performance On-Chip Transformers

> High Efficiency @ Low Frequency → Large L/R

Ref: Tyndall, N. Wang et al., IEEE TPEL, 2015

### **DLM Microtransformer**

- 4.5  $\mu$ m core & 15  $\mu$ m metal

- 270 nH/1.22 Ω

- ✓ 78% efficiency @ 20 MHz

- ✓ 6kV Isolation

- core related issues

- × 7 masks

- × 3 mm<sup>2</sup>

PwrSoC'16

## R. Wu

Needed: High Performance On-Chip Transformers

> High Efficiency @ Low Frequency  $\rightarrow$  Large L/R

Ref: Our Work, R. Wu et al., IEEE TED, 2015

## Interleaved Embedded Transformer

- $\checkmark$  100  $\mu$ m metal

- ✓ 88 nH/0.45 Ω

- ✓ 80% efficiency @ 20 MHz

- ✓ 3 masks

- ✓ 2 mm<sup>2</sup>

PwrSoC'16

× 380 V isolation

breakdown path C at chip surface

6

## R. Wu

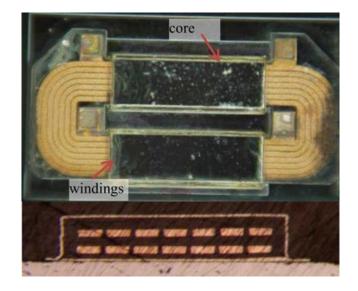

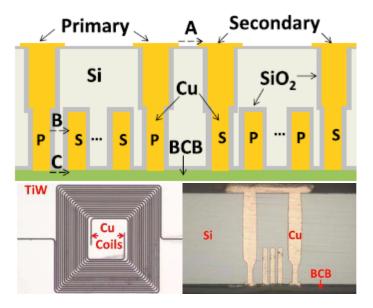

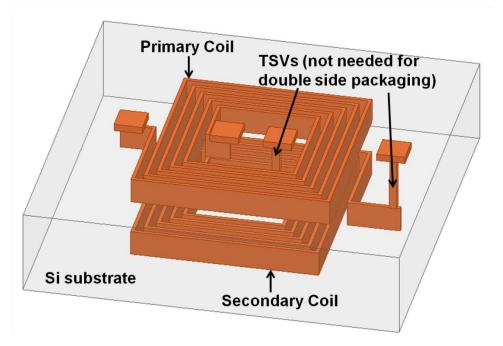

# **Double-Side Embedded Transformer**

## Device Structure

large thicknesses for both coils

- whole area usage for both coils

- breakdown through substrate:

Cu-oxide-Si-oxide-Cu for isolation

- balanced stresses at two sides

- 🗙 weaker coupling

Ref: R. Wu et al., IEEE TED, in press

### R. Wu

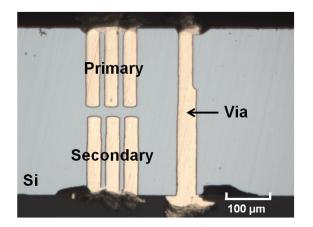

## **Double-Side Embedded Transformer**

## Transformer Design & Fabrication

| Coil     | Si        | Cu        | Track | Track   | Number | Oxide     |

|----------|-----------|-----------|-------|---------|--------|-----------|

| Diameter | Thickness | Thickness | Width | Spacing | of     | Thickness |

| (µm)     | (µm)      | (µm)      | (µm)  | (µm)    | Turns  | (µm)      |

| 1400     | 350       | 150       | 22    | 15      | 9      | 2         |

Ref: R. Wu et al., IEEE TED, in press

#### R. Wu

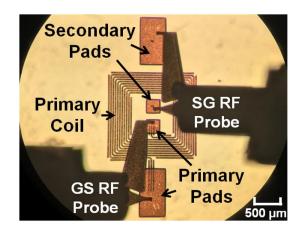

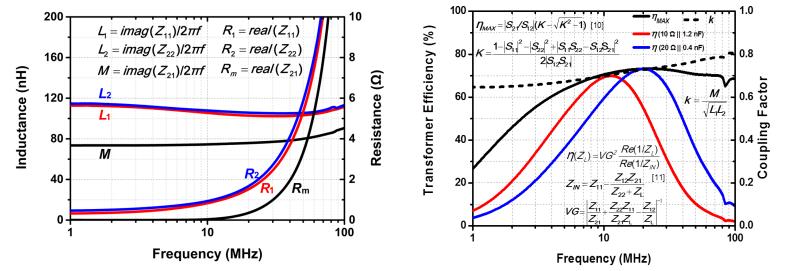

# **Double-Side Embedded Transformer**

## Measurement Results

>1050 V isolation for 2 $\times$ 2  $\mu$ m thermal oxide isolation

insulating substrate for further improving isolation capability

Ref: R. Wu et al., IEEE TED, in press

PwrSoC'16

#### R. Wu

9

# **Performance Comparison**

|                 | Coilcraft | CityU | ADI  | Tyndall | Our Work | This Work |

|-----------------|-----------|-------|------|---------|----------|-----------|

|                 | [1]       | [2]   | [3]  | [4]     | [5]      | [6]       |

| Technology      | discrete  | PCB   | Si   | Si      | Si       | Si        |

| Magnetic Core   | Yes       | No    | No   | Yes     | No       | No        |

| No. of Masks    | N/A       | N/A   | 5    | 7       | 3        | 4         |

| Area (mm²)      | 23        | 21    | 2    | 3       | 2        | 2         |

| Inductance (nH) | 4700      | 242   | 16   | 270     | 88       | 113       |

| Resistance (Ω)  | 0.32      | 0.66  | 1.6  | 1.22    | 0.45     | 0.31      |

| L/R (μΗ/Ω)      | 14.7      | 0.37  | 0.01 | 0.22    | 0.20     | 0.36      |

| Coupling        | 0.97      | 0.58  | N/A  | 0.9     | 0.98     | 0.65      |

| Efficiency      | N/A       | 76%   | 70%  | 78%     | 80%      | 70%       |

| Frequency (MHz) | 1         | 8     | 170  | 20      | 20       | 10        |

| Isolation (kV)  | 1.5       | 15    | 7    | 6       | 0.38     | 1.05      |

[1] Coilcraft: "Miniature transformers LPD5030V," Revised 2015.

[2] CityU: S.C. Tang et al., IEEE Transactions on Power Electronics, pp. 311-315, 2001.

[3] ADI: B. Chen, PwrSoC, 2008; ADuM6000 Datasheet ,Revised 2013.

[4] Tyndall: N. Wang et al., IEEE Transactions on Power Electronics, pp. 5746-5754, 2015.

[5] Our Work: R. Wu et al., IEEE Transactions on Electron Devices, pp. 220-223, 2015.

[6] This Work: R. Wu et al., "A Novel Double-Side Silicon-Embedded Transformer for 10-MHz, 1-kV-Isolation, Compact

Power Transfer Applications," IEEE Transactions on Electron Devices, in press

## R. Wu

## Conclusions

- On-chip transformers with high efficiencies at low frequency are needed for compact, low cost, system-in-package isolated power supply (<2W).</p>

- The double-side embedded transformer features large thicknesses and whole area utilization for both coils. It achieved a best reported L/R of 0.36 μH/Ω with an area of 2 mm<sup>2</sup>. Consequently it can work at a low frequency of 10 MHz with a reasonable efficiency of 70%.

- The only breakdown path is through the substrate. An isolation capability of 1050 V was achieved with two 2-µm-thick thermal oxide isolation layers, and can be further improved by using an insulating substrate.

#### R. Wu