### Mixed-Signal IC Controllers and Low-Volume SMPS Topologies

Prof. Aleksandar Prodić

prodic@ele.utoronto.ca

Laboratory for Power Management and Integrated SMPS

University of Toronto, E. Rogers ECE Department

### A Low Power (Portable) Application – Rogers Portable Radio

- Allowed a large number of households to have daily access to information

- Reduced power consumption by using more efficient electronic tubes

Main motivation: to reduce the volume and weight of the power supply, by far the largest part of previous radios

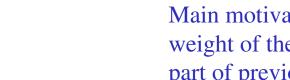

### Low Power SMPS in Portable/Consumer Electronics

http://www.ifixit.com/Teardown/iPad-FCC-Teardown/2197/1

- Dc-dc SMPS occupy between 20% and 80% of the total volume in modern electronics devices, communication equipment, computers...

- Most of the volume occupied by passives and heat sinks

EVO

ARBOR

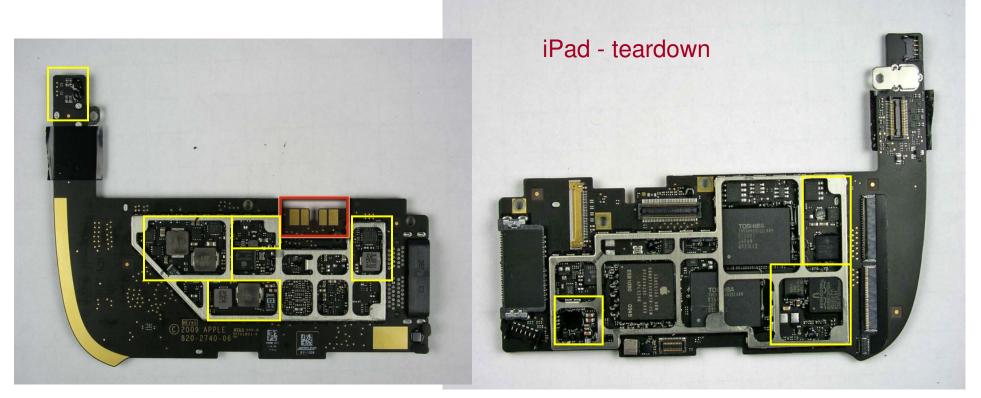

### **Outline: Two Parts of Presentation**

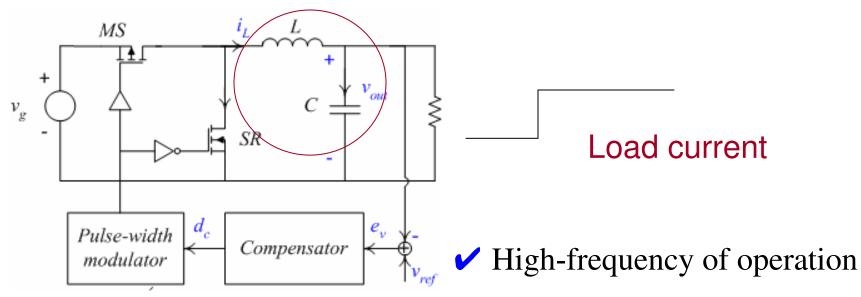

### **Conventional Methods for Volume Minimization**

- Operation at high switching frequencies

- Efficiency optimization = flat and high efficiency curve

- Fast dynamic response of the controller + plug and play operation

All three of these goals can be acomplished

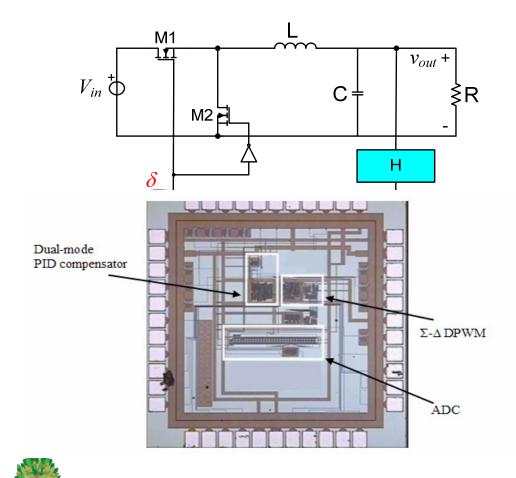

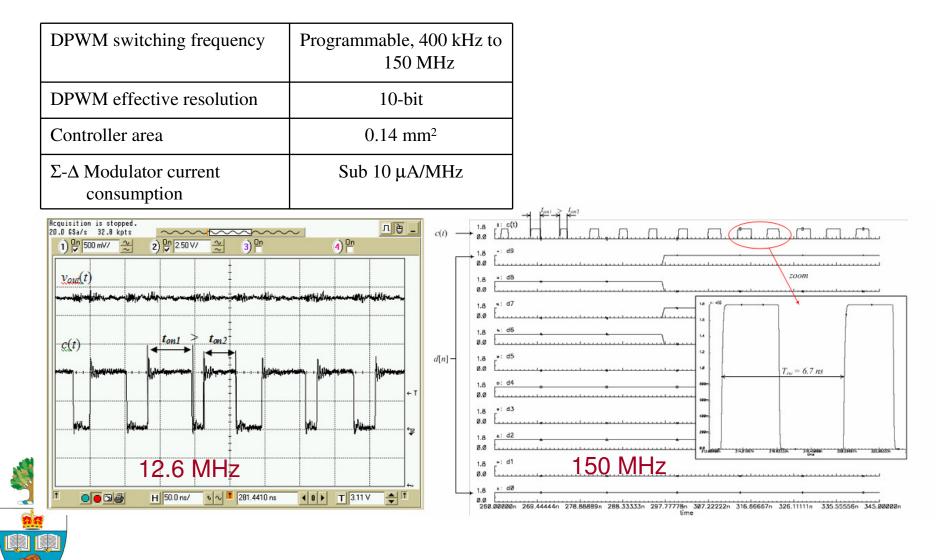

### **Ultra High-Frequency High-Resolution Digital Controller IC**

• The duty ratio of a core resolution (high-frequency) DPWM is varied over several switching cycles to achieve high effective resolution.

- The averaging is performed by the switching converter itself (LC filter)

- The output measured with a moving windowed ADC producing just few error signals

- Processing unit reduced since it also operates over a small error

#### range

[1] Z. Lukic, N. Rahman, A. Prodić, "Multibit  $\Sigma - \Delta$  PWM Digital Controller IC for DC–DC Converters Operating at Switching Frequencies Beyond 10 MHz," IEEEE Transactions on Power Electronics, Vol.22, Issue.5, October 2007, Pg. 1693-1707 (.pdf).

ARBOR

### **Ultra High-Frequency Digital Controller IC Results**

University of Toronto, Rogers ECE Department

EVO

ARBOR

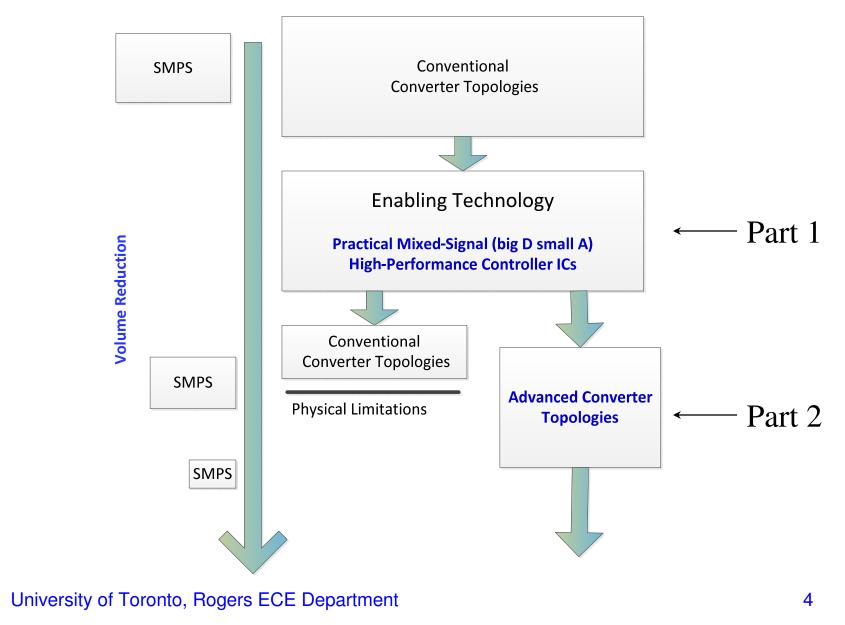

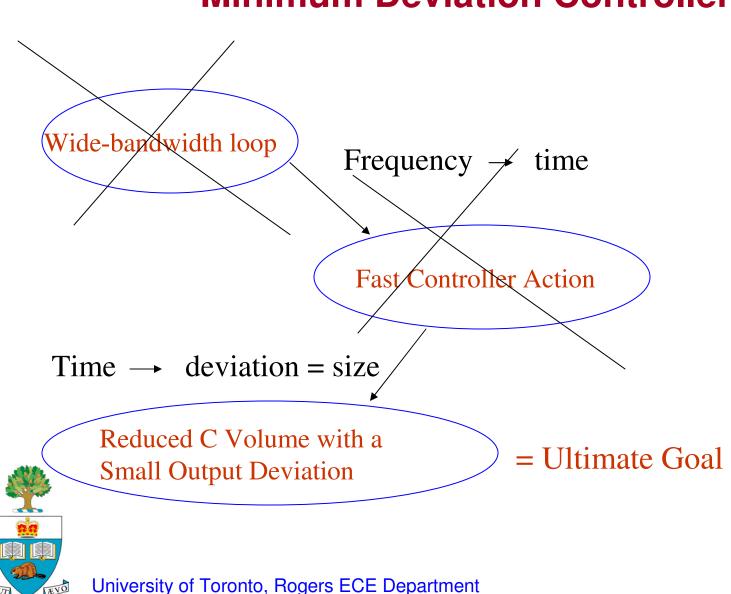

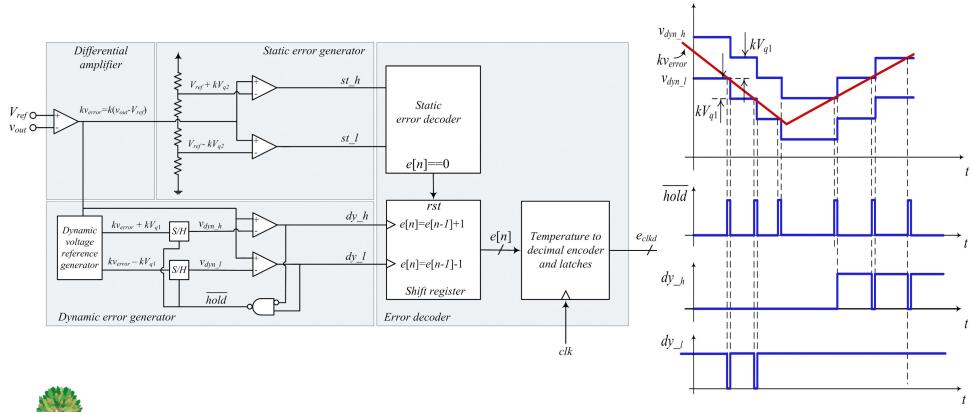

### **Minimum Deviation Controller IC**<sup>[2]</sup>

[2] A. Radic, Z. Lukic. A. Prodic, and R. de Nie, "Minimum Deviation Digital Controller IC for DC-DC Switch-ModePower Supplies," IEEEE Transactions on Power Electronics, Vol.28, Issue.2, February 2013.

University of Toronto, Rogers ECE Department

VEUT

ARBOR

EVO

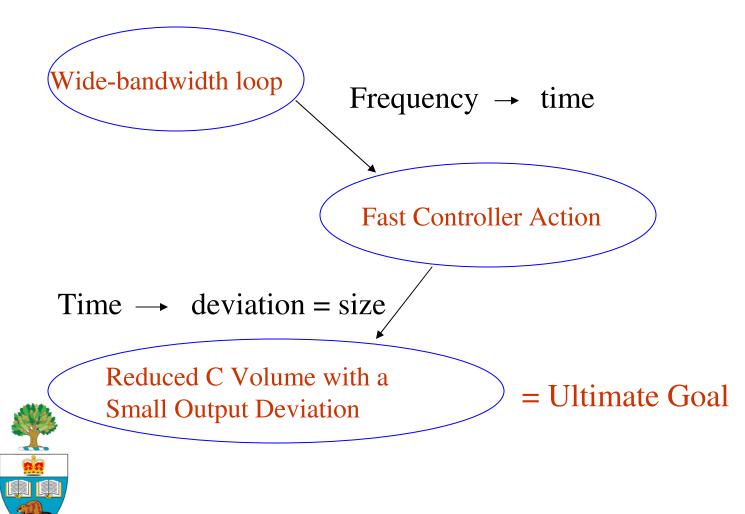

### **Conventional Controller Design**

University of Toronto, Rogers ECE Department

EVO

ARBOR

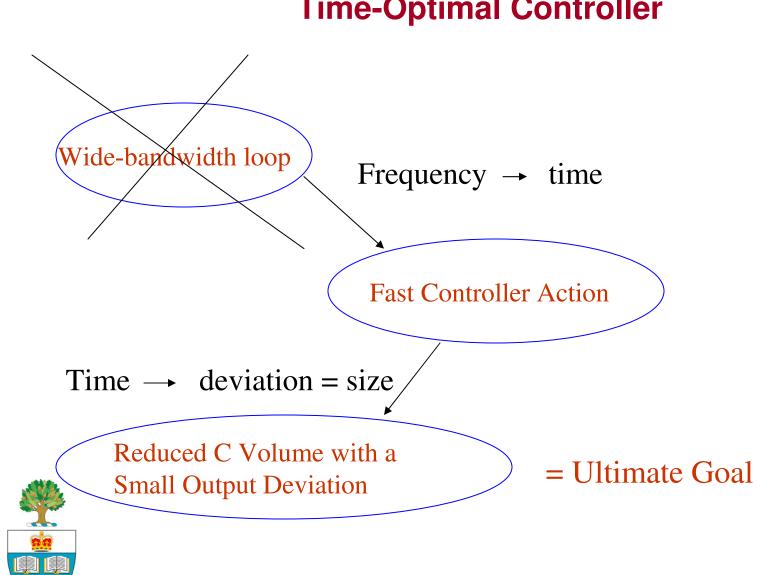

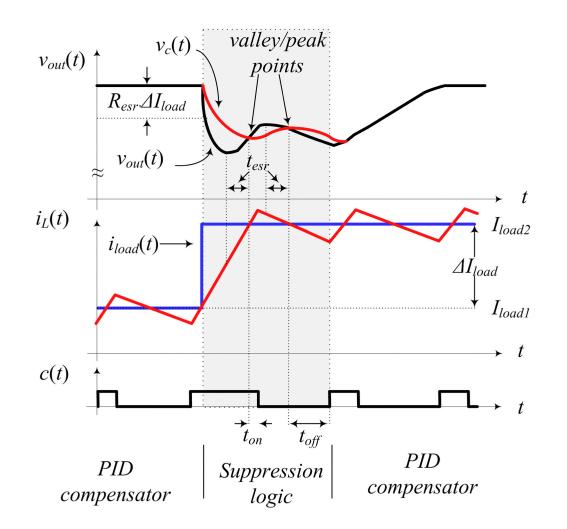

#### **Time-Optimal Controller**

EVO

ARBOR

### **Time-Optimal Control**

Overly large peak inductor current, i.e. inductor might need to be overdesigned

- □ Fairly complex calculations

- Need to know LC values

- Very sensitive to time delays

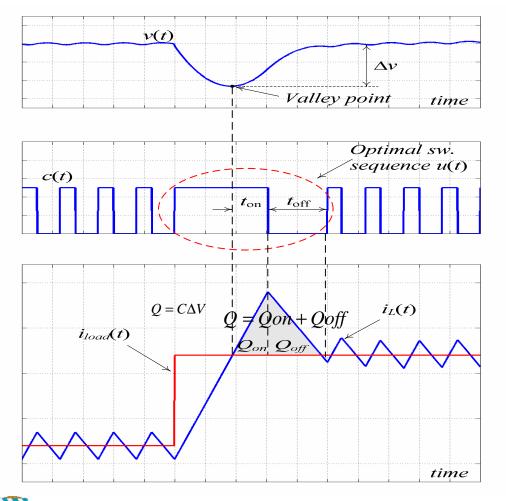

### **Minimum Deviation Controller**

ARBOR

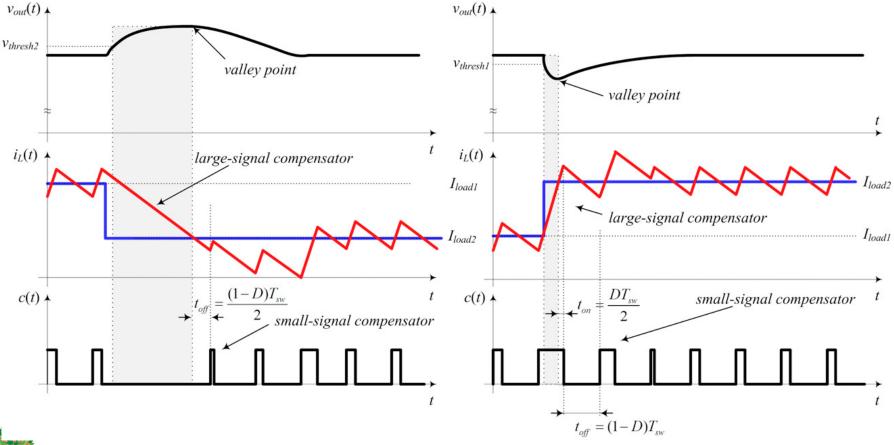

### **Minimum (Optimum) Deviation Controller**

•No current overshoot, no need to know converter parameters, simple calculations

#### **Minimum (Optimum) Deviation Controller**

#### Only needs to remember *D* before transient

### Self-Calibrating SAR Track & Hold ADC

### **Dual Sampling Mechanism**

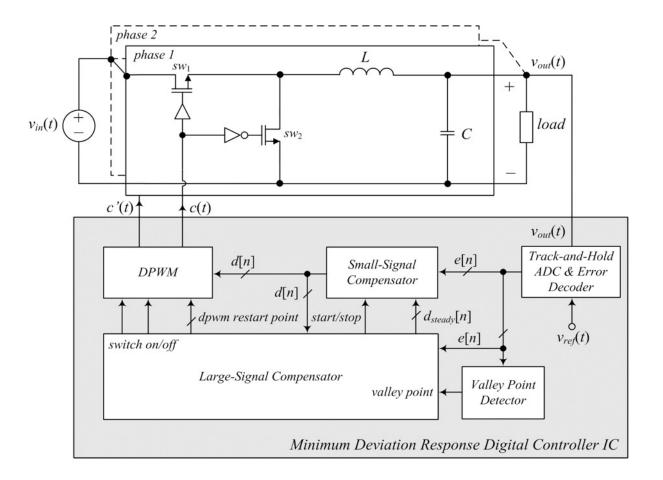

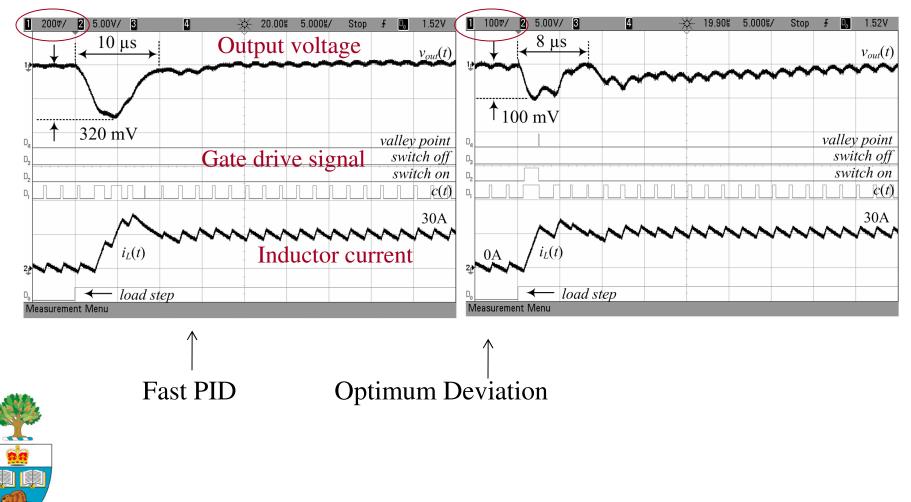

### **Practical Implementation (500 kHz VRM)**

University of Toronto, Rogers ECE Department

EVO

ARBOR

VEUT

ARBOR

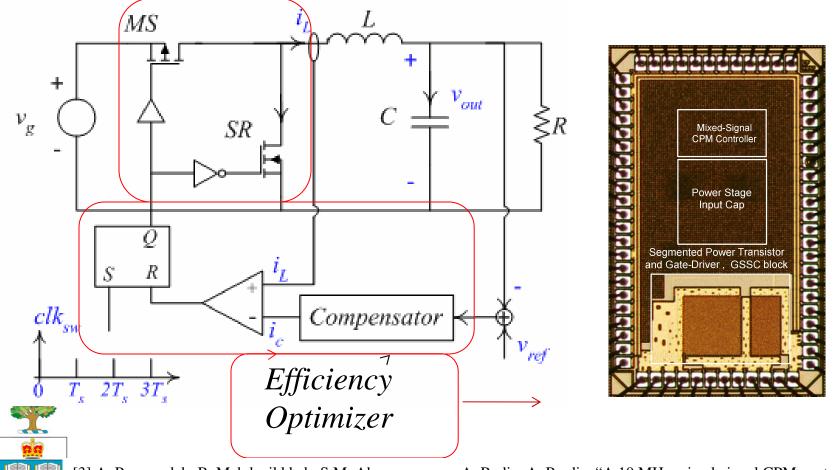

### 10 MHz Mixed Signal CPM Power Module with Instantaneous Efficiency Optimization <sup>[3]</sup>

[3] A. Parayandeh, B. Mahdavikkhah, S.M. Ahsanuzzaman, A. Radic, A. Prodic, "A 10 MHz mixed-signal CPM controlled DC-DC converter IC with novel gate swing circuit and instantaneous efficiency optimization," in Proc. IEEE ECCE, 2011, Pg. 1229-1235

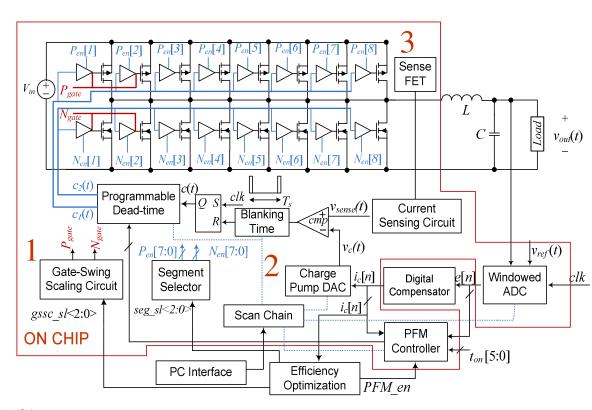

### **IC Block Diagram**

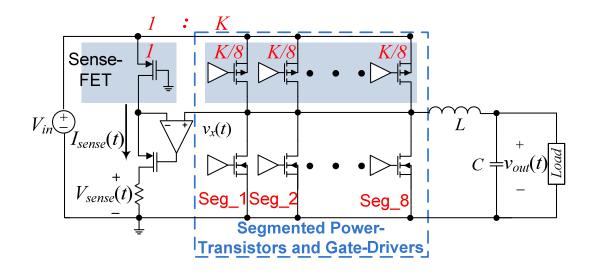

Incorporates:

- *1. Novel gate swing circuit*

- 2. Modified highresolution charge-pump based DAC

- 3. Optimized design of current sensing circuit (senseFET)

### Low-Power High-Frequency SensFET

*GBW reduced since the amplitude is always relatively large (but not the losses)*

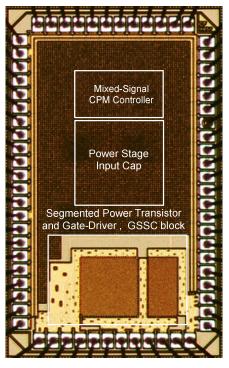

### **IC-Implementation**

| Specifications         | Value        | Units |

|------------------------|--------------|-------|

| CMOS Process           | 0.13         | μm    |

| Area                   | 2.5          | mm2   |

| Input Voltage          | 2.5          | v     |

| Output Voltage         | 0.8-1.3      | v     |

| Rated Load             | 500          | mA    |

| Filter L,C             | 400, 0.9     | nH,µF |

| Switching Frequency ,  | 10           | MHz   |

| Ron Pmos , Nmos        | 0.26 , 0.234 | Ω     |

| Supply Analog, Digital | 1.2, 2.5     | V     |

| Peak Efficiency        | 83           | %     |

| CPM Controller Current | 500          | μΑ    |

| PFM Controller Current | 10           | μΑ    |

| Digital Core           | 200          | μΑ    |

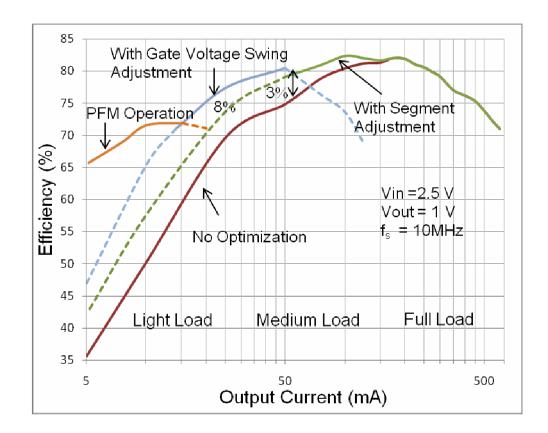

### **Experimental Results**

## Reaching the Physical Limitations Through Hardware-Efficient Mixed-Signal ICs

✓ Optimal response with plug and play operation

Relatively flat efficiency curve even during load changes

Laboratory for Power Management and Integrated SMPS

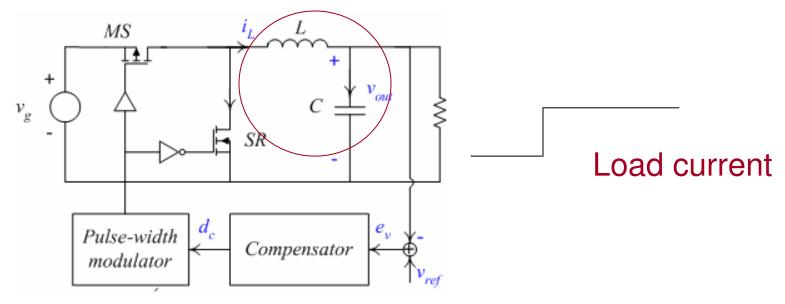

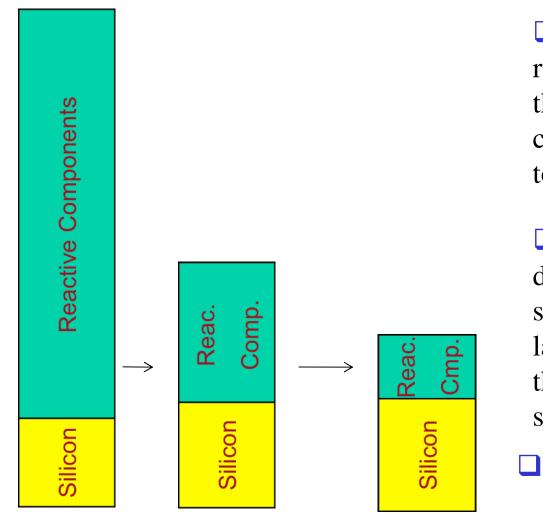

### Moving Forward Advanced Low-Volume SMPS Topologies

#### **Moving Forward**

Reduce volume of reactive components through advanced converter and control topologies

Allow weight (cost)

distribution where the

silicon are will be

larger than today but

the overall volume

smaller

□ No penalty in efficiency

Overall volume (weight) contribution

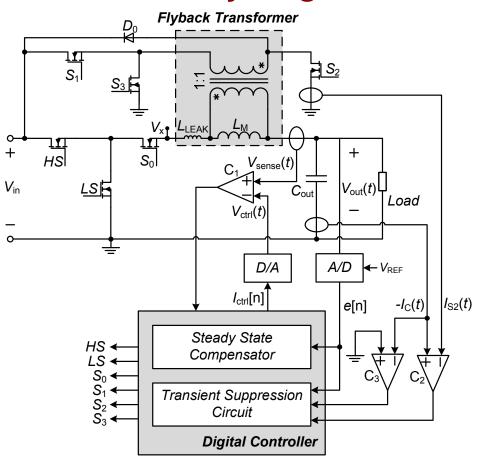

# Flyback Transformer Based Buck (FTBB) with Transient Energy Recycling<sup>[4]</sup>

[4] Jing Wang; Prodić, A.; Wai Tung Ng, "Mixed-Signal-Controlled Flyback-Transformer-Based Buck Converter With Improved Dynamic Performance and Transient Energy Recycling," IEEE Transactions on Power Electronics, Vol. 28, Issue. 3, February 2013.

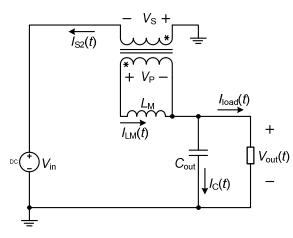

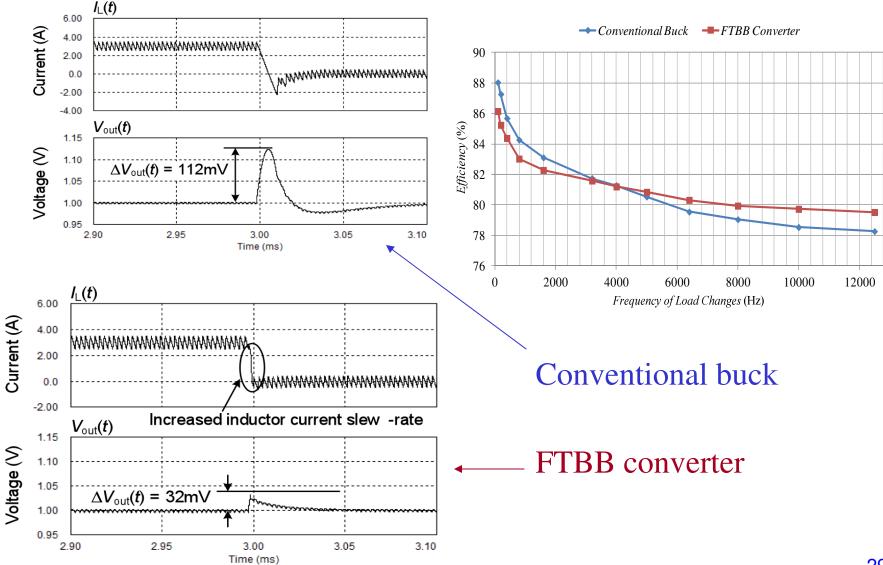

### Flyback Transformer Based Buck with Transient Energy Recycling

The buck inductor is replaced with a flyback transformer, and a single extra switch inside the conduction path

### **FTBB** – **Principle of Operation**

ARBOR

$L_{LEAK}$   $I_{load}(t)$  +  $V_{in}$   $V_{in}$   $V_{irtual short}$   $I_{load}(t)$  +  $V_{out}(t)$  - Light-to-heavy

The inductance is reduced to its leakage value

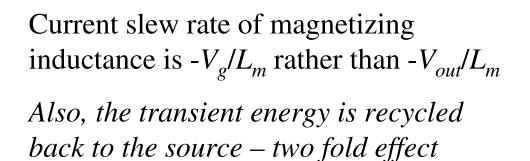

#### **Conventional Minimum-Deviation vs. FTBB**

### Load-Interactive Steered-Inductor DC-DC Converter with Transient Energy Recycling <sup>[5]</sup>

[5] S.M. Ahsanuzzaman, A. Parayandeh, A. Prodic, D. Maksimovic, "Load-interactive steered-inductor dc-dc converter with minimized output filter capacitance," in Proc. IEEE Applied Power Electronics Conference (APEC '10), 2010, Pg. 980-985.

### Load Interactive SMPS with Current Steering

Relies on improved interaction with the digital load

• Theoretically, allows selection of the output capacitor based on the output ripple criteria only.

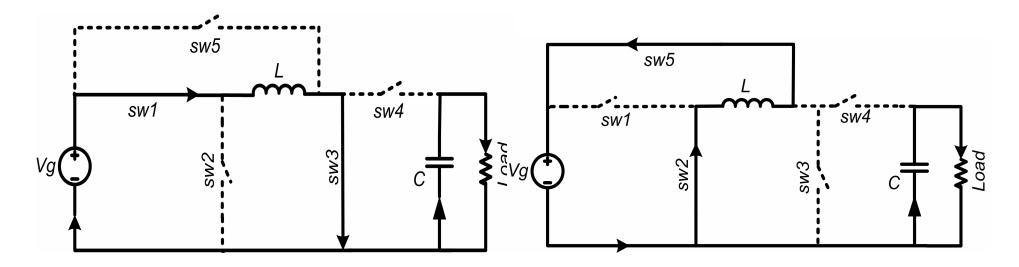

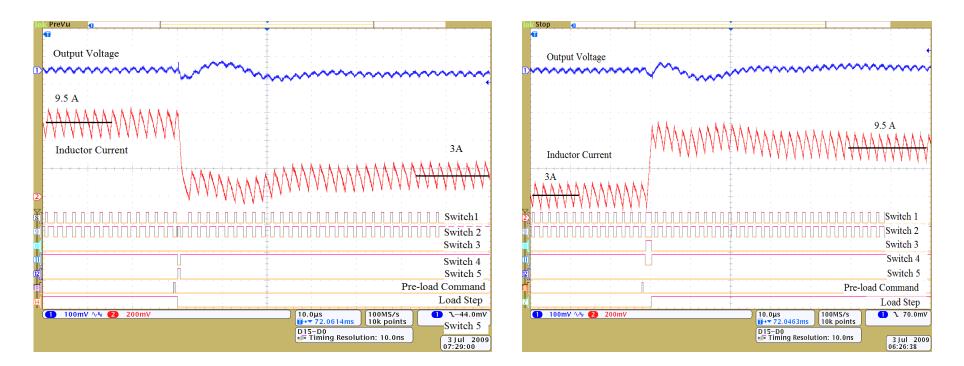

### **Steered Inductor Buck-Boost Converter**

Light-to heavy pre-transient condition current "pump-up"

Slew rate is Vg/L vs (Vg-Vout)/L

•Heavy-to-light transient ,the current is steered away from the capacitor to the source)

- •The current slew-rate is –Vg/L (was -Vout/L in buck mode)

- Energy recycled in this cycle

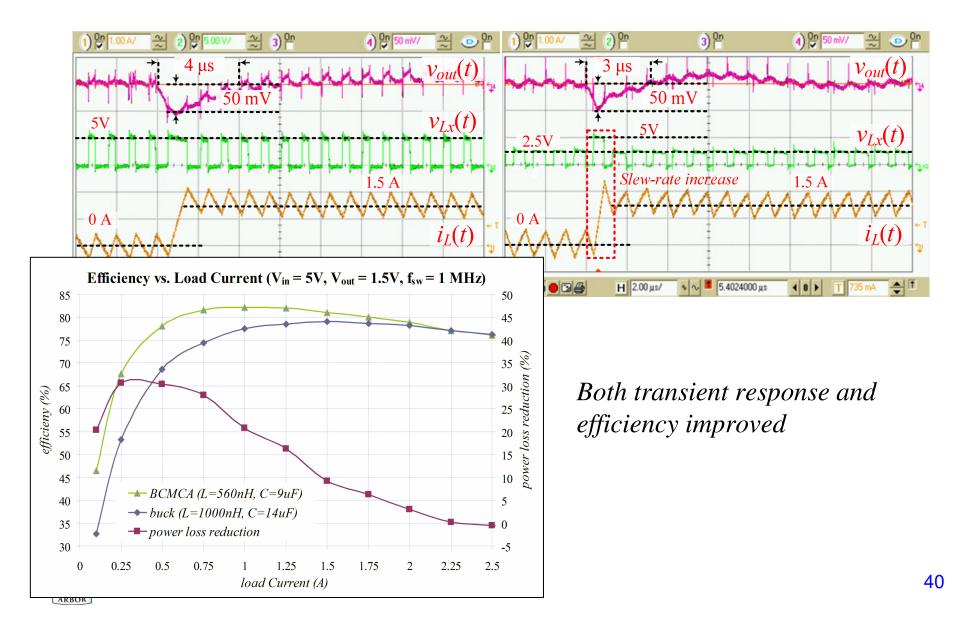

#### **Load Transient Performance**

Theoretically, allows reduction of the output capacitor to ripplelimited value

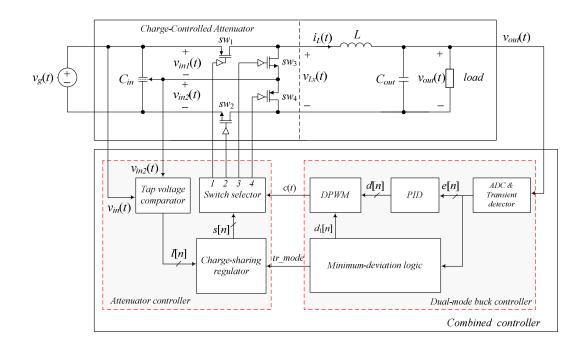

### **Buck Converter with Merged Capacitive Attenuator**<sup>[6]</sup>

[6] A. Radic, A. Prodic, "Buck Converter With Merged Active Charge-Controlled Capacitive Attenuation," IEEE Transactions on Power Electronics, Vol. 27, Issue. 3, March 2012.

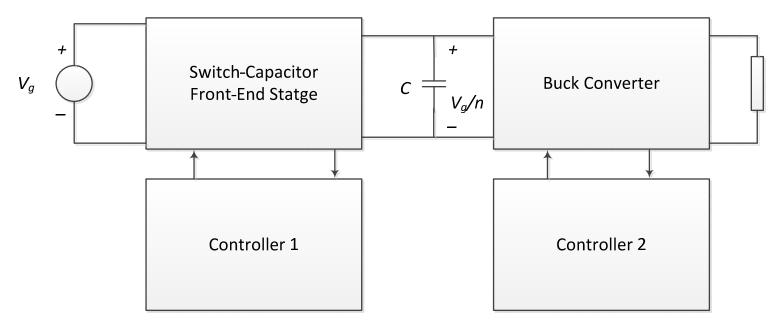

### Common Approach: Serial Connection of a Switch Cap Converter And a Converter with Inductor

1. Reduced output filter volume

1. Bulky intermediate balancing cap

2. Extra switches in conduction path (at least 4) and at least 6 switches total

3. Requires two control loops

#### **Buck Converter with Merged Capacitive Attenuator**

-All switches rated at  $\frac{1}{2} V_{max}$ of the conventional buck (no extra conduction losses)

-Switches are shared between the cap stage and buck

-Lower switching losses than of the conventional buck

-Centre tap voltage maintained constant with the help of buck inductor

- Better transient response than the time-optimal buck

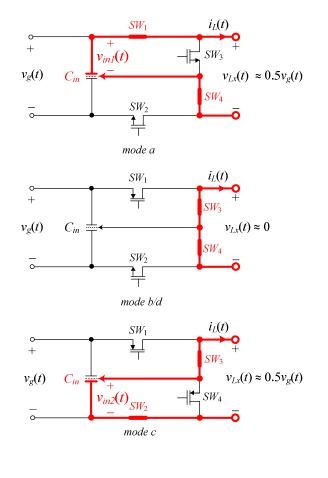

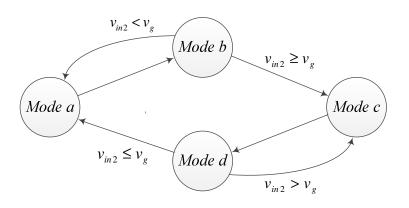

#### Modes of Operation, Ideal and Practical System

Centre-tap voltage controller operation. Skips regular sequence and takes the charge from the cap with larger voltage until balance is achieved.

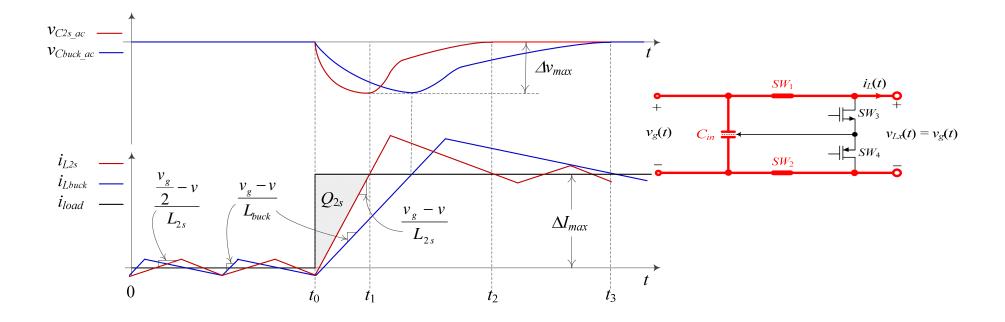

### **Transient Mode**

Comparison with a conventional buck

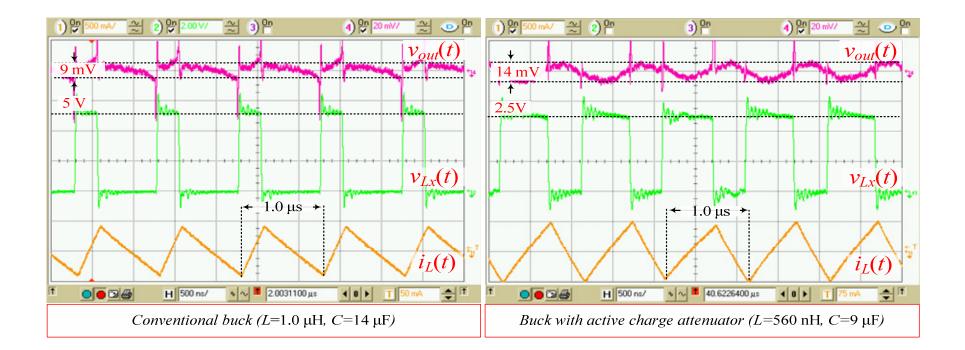

### **Experimental Results: Comparison with Conv. Buck**

For a 5V to 1 V buck 44% smaller inductor and 35% smaller output capacitor

#### **Experimental Results: Comparison with Con. Buck**

#### Extension to 2-Phase<sup>[7]</sup> *2-phase interleaved buck* Input filter converter Active capacitive divider $L_{f}$ $L_p$ $v_{xl}(t)$ $Cr_{-}$ L1G1+ Cin1 $Q_5$ $V_{in1}$ Ē $v_{out}(t)$ G8G9Cout $V_{batt}$ $\mathbb{P}_{\mathbb{P}}Q_3$ *06* ™ $\leq R$ $v_{x2}(t)$ L2+ Cin2 $V_{in2}$ G2G3 G5 G7G4*G6* ADC & Switching control $\leftarrow DPWM \leftarrow d[n]$ e[n]PID . Transient logic detector $d_I[n$ Minimum Deviation. logic Digital controller

$L_1$  takes the charge from the top inductor and  $L_2$  from the bottom

[7] B. Mahdavikhah, P. Jain, A. Prodic, "Digitally controlled multi-phase buck-converter with merged capacitive attenuator," Applied Power Electronics Conference and Exposition (APEC), 2012 Twenty-Seventh Annual IEEE, vol., no., pp.1083-1087, 5-9 Feb. 2012

Laboratory for Power Management and Integrated SMPS

November 17th, 2012

### Many other examples .....

### Conclusion

Digital control allows us to use advanced converter topologies and drastically reduce the volume of SMPS while improving efficiency at the same time.

Laboratory for Power Management and Integrated SMPS

November 17th, 2012

### Thank you