2<sup>nd</sup> International Workshop on Power Supply On Chip

www.powersoc.org

October 13-15, 2010

**Tyndall National Institute**

Cork, Ireland

# 2<sup>nd</sup> International Workshop on Power Supply On Chip

Following the overwhelming positive feedback from PwrSOC`08, the second International Workshop on Power Supply on Chip will once again bring together the key players from both the industry and academic communities active in the emerging area of system-in-package (SiP) and system-on-chip (SoC) solutions for power supply miniaturisation.

A major challenge to the further miniaturisation of DC-DC converters is the inability to integrate passive components on silicon due to their relatively large size at today's operating frequencies of 0.5 to 5 MHz. Increasing the switching frequencies into the 10 to 100 MHz region offers the potential for the reduction of passive component values to the point where, with the right technology, their size becomes compatible with silicon device dimensions.

Currently, significant R&D and product development activity is evident in advances in semiconductor, magnetic, capacitor and packaging material technologies that will deliver products operating at multi-MHz frequencies. The ultimate target is to develop new miniaturised product formats that can be referred to as power supply-in-package (PSiP) and power supply-on-chip (PwrSoC). This space has been under increasing focus from semiconductor companies due to their ability to deliver advanced silicon processing technologies and functional integration with increased reliability. This proliferation of functionally-integrated hardware solutions can be seen as an inflection point in the power supply industry which is seeing a dramatic move away from traditional power supply manufacturing (with a focus on the assembly of power supply modules or bricks from discrete components) to an increasing emphasis on power supply products derived from semiconductor and microelectronics platforms and technologies.

At Powersoc '08, the speakers and conference organizers agreed that the interdisciplinary approach of the workshop was essential to the successful development of power supply-on-chip technology. Application needs, technologies, manufacturability and packaging have all converged to the point that a power SoC solution is not only possible but quite likely required in certain applications. Semiconductor manufacturers, materials researchers, system makers and power supply designers all need to come together to address the problems of functional and packaging integration. The 2008 PwrSOC workshop was thus a significant step in that direction and Powersoc '10 is positioned to result in further significant progress in this field.

It is now clear that the concept of integrated power solutions presents a significant disruptive opportunity in power management solutions and warrants an international forum for its discussion and for the elucidation of the key challenges and innovations that lie ahead in the commercialisation of this space.

Tyndall is supported in the organisation of the workshop with technical co-sponsorship by the IEEE Power Electronics Society (PELS) (<u>http://www.ieee-pels.org</u>), the Power Sources Manufacturers Association (PSMA) (<u>http://www.psma.com</u>), and the European Centre for Power Electronics (ECPE) (<u>http://www.ecpe.org</u>).

The workshop is also supported by Enterprise Ireland, Investment Development Agency, Science Foundation Ireland, MIDAS Ireland, IMAPS Europe, National Microelectronics Institute, UK and United Technologies Research Centre.

Dr. Cian Ó Mathúna General Chair

# 2<sup>nd</sup> International Workshop on Power Supply On Chip

# www.powersoc.org

# October 13-15, 2010

# **Tyndall National Institute**

# Cork, Ireland

General Chair: Cian Ó Mathúna, Tyndall National Institute

#### **Programme Chairs:**

Yan-Fei Liu, Queens University, Francesco Carobolante, Qualcomm, Arnold Alderman, Anagenesis, Saibal Roy, Tyndall National Institute

#### **Technical Committee:**

Eduard Alarcon, Universitat Politècnica de Catalunya Bruno Allard, INSA Magali Brunet, LAAS CNRS Baoxing Chen, Analog Devices José Cobos, UPM Maeve Duffy, NUI Galway Ray Foley, UTRC Florian Herrault, Georgia Tech Brice Jamieson, Tyndall National Institute Seth Sanders, UC Berkeley John Shen, University of Central Florida Ed Stanford, Intel Charles Sullivan, Dartmouth College Matthew Wilkowski, Enpirion Shuming Xu, Texas Instruments Masahiro Yamaguchi, Tokyo University

#### **Tyndall Organising Committee:**

Cian Ó Mathúna Brice Jamieson Catherine Walsh Katherine Barry Saibal Roy Jeffrey Godsell Santosh Kulkarni Shunpu Li Ningning Wang

# Workshop Schedule

# Tuesday 12<sup>th</sup> October

| 17:30 – 19:00 | Registration |  |

|---------------|--------------|--|

# Wendesday 13<sup>th</sup> October

| 08:00 - 09:00 | Registration             |                              |

|---------------|--------------------------|------------------------------|

| 09:00 - 09:30 | Welcome/Workshop Opening |                              |

| 09:30 – 10:15 | Ted DiBene               | Plenary Talk                 |

|               | INTEL                    | Power on Silicon with on-die |

|               | USA                      | magnetics: The start of a    |

|               |                          | revolution in power delivery |

|               |                          | and power management for     |

|               |                          | SoC's and high performance   |

|               |                          | applications                 |

# Session 1: System Architectures compatible with PwrSoc

Session Co-Chairs: Francesco Carobolante, Ed Standford, Bruno Allard, José Cobos

| 10.15 10.40   | Alakaandar Dradia       | Lligh Dorformonoo Miyod Cignol  |

|---------------|-------------------------|---------------------------------|

| 10:15 – 10:40 | Aleksandar Prodic       | High-Performance Mixed-Signal   |

|               | UNIVERSITY OF TORONTO   | Controllers for On-Chip         |

|               | Canada                  | Integrated SMPS                 |

| 10:40 - 11:05 | Alex Vainberg           | Adaptive Voltage Scaling (AVS)  |

|               | NATIONAL SEMICONDUCTOR  | Technology                      |

|               | USA                     |                                 |

| 11:05 - 11:35 | River Le                | ee Hotel                        |

|               | Breako                  | ит Room                         |

|               | Coffee/T                | Fea Break                       |

| 11:35 - 12:00 | Dominik Schmidt         | Challenges and Solutions:       |

|               | INTEL                   | Power Delivery and Regulation   |

|               | USA                     | in NanoCMOS SoCs                |

| 12:00 - 12:25 | Hans Meyvaert           | The importance of fully-        |

|               | ESAT MICAS K.U. LEUVEN  | integrated CMOS: Cost Effective |

|               | Belgium                 | Integrated DC-DC Converters     |

| 12:25 - 12:50 | William O. Keese        | Power Management Design         |

|               | NATIONAL SEMICONDUCTOR, | Challenges and Techniques for   |

|               | USA                     | Power Amplifiers in 2G/3G/4G    |

|               |                         | Multimode Handsets              |

| 12:50 - 14:00 | River Le                | ee Hotel                        |

|               | Lu                      | nch                             |

# Session 2: Technologies and Devices to Enable PwrSoC

Session Co-Chairs: Yan-Fei Liu, John Shen, Shuming Xu

| 14:00 - 14:25 | Anco Heringa<br>NXP,<br>Netherlands                      | High Voltage transistors for<br>SoCs in baseline CMOS                                    |

|---------------|----------------------------------------------------------|------------------------------------------------------------------------------------------|

| 14:25 - 14:50 | Shuming Xu<br>Texas Instruments,<br>USA                  | NexFET Technology: New<br>Technology Enables High Power<br>Density                       |

| 14:50 - 15:15 | Paul Chow<br>Rensselaer Polytechnic<br>Institute,<br>USA | GaAs p-HEMT-based Power ICs<br>for High Frequency Switching<br>Converter Applications    |

| 15:15 - 15:45 | Вгеако                                                   | ee Hotel<br>ит Rooм<br>Геа Break                                                         |

| 15:45 - 16:05 | Sameer Pendharkar<br>Texas Instruments,<br>USA           | Mixed signal technologies<br>enabling PwrSoC and PwrSiP                                  |

| 16:05 - 16:30 | Sami Ajram<br>SL3J Systems<br>France                     | Power train scaling, high<br>frequency cross talk and its<br>impact on controller design |

# **Session 3: Poster Session**

Session Co-Chairs: Brice Jamieson, Ray Foley, Florian Herrault, Magali Brunet, Maeve Duffy, Yan-Fei Liu, José Cobos

| 19:00 – 20:30 | River Lee Hotel<br>Breakout Room                 | Poster Session and Welcome<br>Reception |

|---------------|--------------------------------------------------|-----------------------------------------|

| 20:30 – 22:30 | River Lee Hotel<br>The Weir Restaurant<br>Dinner |                                         |

# Thursday 14<sup>th</sup> October

# Session 4a: Integrated Passives: Magnetics

Session Co-Chairs: Charles R. Sullivan, Maeve Duffy, Matthew Wilkowski, Florian Herrault, Saibal Roy

| 08:30 - 08:55 | Saibal Roy                          | Challenges in magnetics for     |

|---------------|-------------------------------------|---------------------------------|

|               | Tyndall National Institute,         | PwrSoC - Development in high-   |

|               | IRELAND                             | frequency magnetics, materials, |

|               |                                     | and integration                 |

| 08:55 - 09:20 | Donald .S. Gardner                  | Integrated On-Chip Inductors    |

|               | INTEL,                              | Using Magnetic Material         |

|               | USA                                 |                                 |

| 09:20 - 09:45 | Sarah Bedair                        | Thin Film Piezotransformers for |

|               | US ARMY RESEARCH LABS,              | High Frequency Switched Mode    |

|               | USA                                 | Power Supplies                  |

| 09:45 - 10:10 | Florian Herrault                    | Lamination-Based Technology     |

|               | Georgia Tech,                       | for High Performance Metallic   |

|               | USA                                 | Magnetic Cores                  |

| 10:10 - 10:40 | River L                             | ee Hotel                        |

|               | Breako                              | ит Room                         |

|               | Poster Session and Coffee/Tea Break |                                 |

| 10:40 - 11:05 | Nian Sun                            | Low-Temperature Deposited       |

|               | NORTHEASTERN UNIVERSITY,            | Metallic Magnetic Films and     |

|               | USA                                 | Ferrite Films and Their         |

|               |                                     | Applications in Integrated RF   |

|               |                                     | Magnetic Devices                |

| 11:05 – 11:30 | Matthew Wilkowski                   | Magnetics on Wafer:             |

|               | ENPIRION,                           | Transitioning From Prototype    |

|               | USA                                 | to Manufacturing                |

|               |                                     |                                 |

| 11:30 – 12:30 | Open Forum Discussion               | "PwrSoC or Not"                 |

|               |                                     |                                 |

| 12:30 - 13:30 | River Lee Hotel                     |                                 |

|               | Lu Lu                               | nch                             |

# Session 4b: Integrated Passives: Capacitators

# Session Co-Chairs: Seth Sanders, Magali Brunet

| 13:30 - 13:55 | Catherine Bunel           | 3D capacitors: Manufacturing  |

|---------------|---------------------------|-------------------------------|

|               | IPDIA                     | and applications              |

|               | CAEN, FRANCE              |                               |

| 13:55 - 14:20 | Magali Brunet             | Ultra-high power carbon-based |

|               | LAAS CNRS,                | microsupercapacitors          |

|               | Toulouse, France          |                               |

| 14:20 - 14:45 | Mihaela Popovici          | ALD Strontium Titanates and   |

|               | IMEC,                     | their characterization        |

|               | Belgium                   |                               |

| 14:45 - 15:10 | Stephen O'Brien           | Printed components and large- |

|               | CITY COLLEGE OF NEW YORK, | area capacitators             |

|               | USA                       |                               |

| 15:10 - 15:40 | River Le                  | ee Hotel                      |

|               | Breakou                   | JT ROOM                       |

|               | Poster Session and        | d Coffee/Tea Break            |

# Session 5: Converter Topologies and Control Systems for PwrSoC

| 15:40 – 16:05 | Rais Miftakhutdinov<br>Texas Instruments,<br>USA      | PSiP and PwrSoC Based<br>Opportunities and Solutions for<br>High Power Systems                          |

|---------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| 16:05 - 16:30 | Eby Friedman<br>UNIVERSITY OF ROCHESTER,<br>USA       | Small Area Power Converter for<br>Application to Distributed On-<br>Chip Power Delivery                 |

| 16:30 - 16:55 | Olivier Trescases<br>University of Toronto,<br>Canada | Gate-Charge Recovery for Light-<br>Load Efficiency Improvement in<br>High-Frequency DC-DC<br>Converters |

| 18:30 - 23:00 | Trident Hotel, Kinsale<br>Workshop Banquet            |                                                                                                         |

# Friday 15<sup>th</sup> October

# Session 5: Converter Topologies and Control Systems for PwrSoC

# Session Co-Chairs: Ray Foley, Yan-Fei Liu, Eduard Alarcon

| 08:30 - 08:55 | David Anderson          | Compact, Cost-effective,      |

|---------------|-------------------------|-------------------------------|

|               | NATIONAL SEMICONDUCTOR, | Efficient Power: Is there a   |

|               | USA                     | sweet-spot for integration?   |

| 08:55 - 09:20 | Seth Sanders            | Integrated Power Conversion - |

|               | UC BERKELEY,            | The Switched Capacitor        |

|               | USA                     | Approach                      |

| 09:20 - 09:45 | Gabriel A. Rincón-Mora  | Energy-Harvesting Switching   |

|               | Georgia Tech,           | Converter ICs                 |

|               | USA                     |                               |

# Session 6: Monolithic Integration vs System in Package

Session Co-Chairs: Arnold Alderman, Baoxing Chen, Cian Ó Mathúna

| 09:45 - 10:10 | Arnold Alderman                 | Overview of product            |

|---------------|---------------------------------|--------------------------------|

|               | ANAGENESIS,                     | integration                    |

|               | USA                             |                                |

| 10:10 - 10:35 | Bill Liu                        | Advanced Power Management      |

|               | ANALOG DEVICES,                 | Techniques for Portable        |

|               | USA                             | Applications                   |

| 10:35 - 11:05 |                                 | e Hotel                        |

|               | Breakou                         | JT ROOM                        |

|               | Coffee/T                        | ea Break                       |

| 11:05 - 11:40 | Dion Manessis                   | Embedded Power Dies for        |

|               | FRAUNHOFER INSTITUTE,           | System in Package              |

|               | GERMANY                         | 5                              |

|               |                                 |                                |

| 11:40 - 12:05 | Brian Molloy                    | Power SoC Vs SiP – Competitive |

|               | INFINEON TECHNOLOGIES,          | Challenges in High-Volume      |

|               | USA                             | Applications                   |

| 12:05 - 12:30 | Ashraf Lofti                    | PowerSoC Commercialisation –   |

|               | ENPIRION,                       | Market Drivers and Key         |

|               | USA                             | Technology Enablers            |

| 12:30 - 12:55 | Satoshi Matsumoto               | Future Power Electronics for   |

|               | KYUSHU INSTITUTE OF TECHNOLOGY, | Realizing Sustaining Society   |

|               | Japan                           |                                |

| 12:55 - 13:10 | Close of Workshop               |                                |

| 13:10 - 14:15 | River Le                        | ee Hotel                       |

|               | Lunch                           |                                |

# **Poster Session**

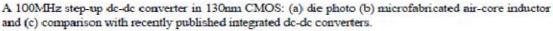

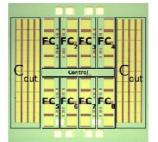

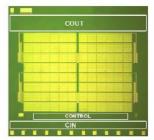

#### A 100MHz 8x step-up dc-dc converter in 130nm 1.2V CMOS process with micro-fabricated air-core inductor

Lin Xue, Christopher Meyer, Christopher Dougherty, \*Sarah Bedair,\*Brian Morgan, David P. Arnold and Rizwan Bashirullah

Department of Electrical and Computer Eng., University of Florida, Gainesville, FL 32611

\*U.S. Army Research Laboratory, 2800 Powder Mill Road, Adelphi, MD 20783.

# Fully Integrated Switched-Capacitor DC-DC Converters in Standard CMOS: The Key- Enabler for on-chip Power Management

Tom Van Breussegem, Hans Meyvaert and Michiel Steyaert ESAT – MICAS K.U. Leuven – Kasteelpark Arenberg 10 Belgium

#### Multilayer Micromachined Air-Core Power Inductors and Transformers

Christopher D. Meyer<sup>1</sup>, Sarah S. Bedair<sup>2</sup>, Brian C. Morgan<sup>2</sup>, and David P. Arnold<sup>1</sup> <sup>1</sup>Department of Electrical and Computer Engineering, University of Florida, Gainesville, FL 32611 <sup>2</sup>U.S. Army Research Laboratory, Adelphi, MD 20783

#### Performance and Fabrication of On-Chip Power Inductors Using Multi-Layer Co-Zr-O Films

Di Yao, Jizheng Qiu, and Charles R. Sullivan Thayer School of Engineering at Dartmouth, Hanover, NH, USA

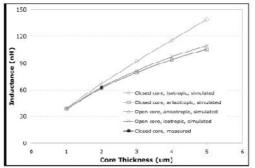

#### Effect of anisotropic permeability on a closed-core inductor

Joyce Mullenix<sup>1</sup> and Shan X. Wang<sup>1, 2</sup>

<sup>1.</sup> Dept. of Electrical Engineering, Stanford University, Stanford, CA 94305, USA

<sup>2</sup> Dept. of Materials Science and Engineering, Stanford University, Stanford, CA 94305, USA

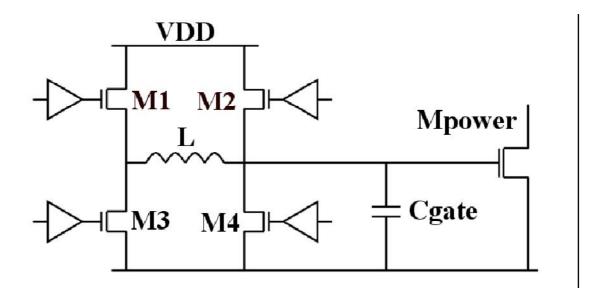

#### Improvement of the efficiency of HF DC/DC converters by resonant gate drivers

Malal Bathily, Frederic Hasbani and Bruno Allard STMicroelectronics (Crolles) 850 rue Jean Monnet 38926 Crolles, France

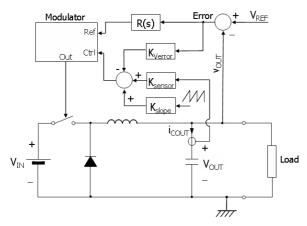

# Output cap reduction thanks to a fast and novel control technique: V<sup>2</sup>I<sub>c</sub> control

M. del Viejo; P. Alou; J. A. Oliver; O. García; J. A. Cobos. Centro de Electrónica Industrial. Universidad Politécnica de Madrid, Madrid, Spain

#### Potential for improved efficiency of PwrSoC with parallel micro-inductors

M. Duffy<sup>1</sup>, N. Wang<sup>2</sup> <sup>1</sup> Power Electronics Research Centre, NUI Galway, Ireland <sup>2</sup> Tyndall National Institute, Cork, Ireland

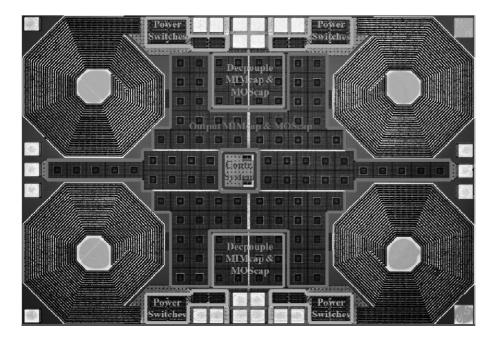

#### Fully-Integrated Inductive DC-DC converters in Standard CMOS

Mike Wens, Hans Meyvaert and Michiel Steyaert ESAT-MICAS K.U.Leuven – Kasteelpark Arenberg 10 Belgium

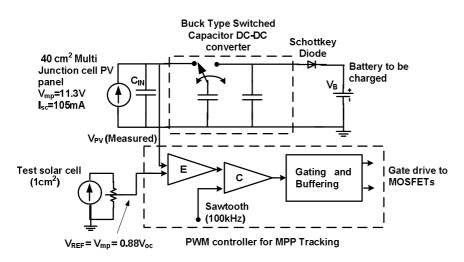

#### Portable PV Fed Maximum Power Point Tracking Switched Capacitor Battery Charger

Pradeep K. Peter, Indian Space Research Organization, India Vivek Agarwal, Indian Institute of Technology Bombay, India

# A novel simple-inductance, double-output Step-down converter for embedded audio applications

Xavier Branca, ST ERICSSON, Grenoble, France

#### Integrated LC filter on silicon for DC-DC converter applications

Magali Brunet, Philippe Artillan, David Bourrier, Jean-Pierre Laur, Nicolas Mauran, Laurent Bary, Monique Dilhan, Bruno Estibals, Corinne Alonso and Jean-Louis Sanchez

Laboratoire d'Analyse et d'Architecture des Systèmes (LAAS-CNRS), 7 avenue du Colonel Roche, 31077 Toulouse cedex 4, France

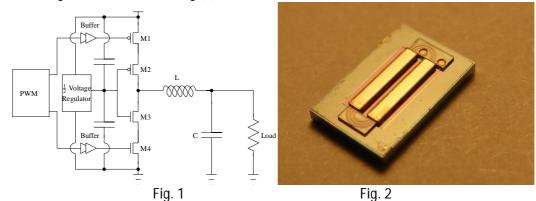

#### Design of a DC-DC Converter with Co-Packaged Inductor

Jason Hannon, Santosh Kulkarni, Ray Foley, Ningning Wang, Saibal Roy, Cian O'Mathuna and Kevin McCarthy, Tyndall National Institute, Cork, Ireland

#### A 150V Power SOI LDMOS Transistor for MHz Frequency Switching Applications

Patrick Shea University of Central Florida, USA

#### GaN Schottky diodes for high operating temperature electronics Donagh O'Mahony<sup>(1)</sup>, Pleun Maaskant<sup>(1)</sup>, Peter J. Parbrook<sup>(1,2)</sup> and Brian Corbett<sup>(1)</sup>

<sup>(1)</sup>Tyndall National Institute University College Cork, Lee Maltings, Cork, Ireland. <sup>(2)</sup>Department of Electrical and Electronic Engineering, University College Cork, Western Road, Cork, Ireland.

#### Digital Control of Multi-Rail DC-DC Converter Systems with Non-Integer Switching Frequency Ratios

James Mooney University of Limerick, Ireland

# HIGH-FREQUENCY COMPLEX PERMEABILITY ANALYSIS OF CONIFE FERROMAGNETIC THIN FILMS FOR INTEGRATED PASSIVES.

Jeffrey F. Godsell, Santosh Kulkarni and Saibal Roy Tyndall National Institute, Cork, Ireland.

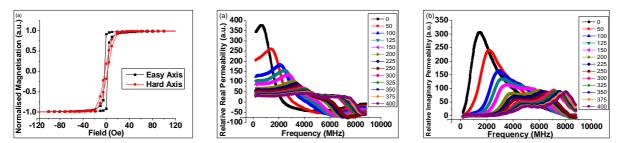

#### Engineered Anisotropy in Modulated Magnetic Films for Miniaturized Devices

Shunpu Li, Jeffrey Godsell, Saibal Roy Tyndall National Institute, Cork, Ireland

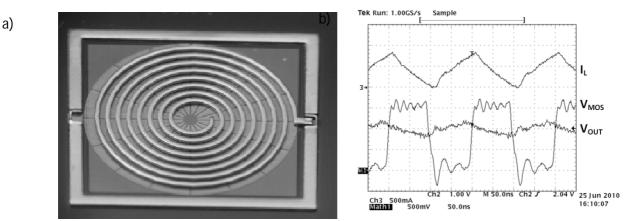

#### 20MHz DC-DC Converter with Integrated Inductor on Si

Ningning Wang<sup>1</sup>, Jason Hannon<sup>2</sup>, Ray Foley<sup>2</sup>, Kevin McCarthy<sup>2</sup>, Kenneth Rodgers<sup>1</sup>, Finbarr Waldron<sup>1</sup>, Santosh Kulkarni<sup>1</sup>, Saibal Roy<sup>1</sup>, Cian Ó Mathúna<sup>1</sup>

<sup>1</sup>Tyndall National Institute, University College Cork, Ireland, <sup>2</sup> Dept. of Electrical Engineering, University College Cork, Ireland, <sup>3</sup> Enterprise Ireland, Industry House, Rossa Avenue, Bishopstown, Cork, Ireland

#### AN IMPROVED CALCULATION METHOD FOR AC COPPER LOSSES IN POWER INDUCTORS INTEGRATED ON SILICON

Ningning Wang, Sean Cian Ó'Mathúna

Tyndall National Institute, University College Cork, Ireland,

# Structural and Electrical Analysis of Interface Control Layers of MgO or Al2O3 Deposited by Atomic Layer Deposition, at the high- κ/III-V Interface

A. O'Mahonya, S. Monaghana, R. Chiodoa, b, I. M. Poveya, A. Blakea, K. Cherkaouia, R. E. Naglea, É. O'Connora, R. D. Longa, V. Djaraa, D. O'Connella, F. Crupib, P. K. Hurleya and M. E. Pemblea

<sup>a</sup> Tyndall National Institute, University College Cork, Lee Maltings, Prospect Row, Cork, Ireland.

<sup>b</sup> Università della Calabria, Via P. Bucci, 41C I-87036 Arcavacata di Rende (CS), Italy.

# **KEYNOTE SPEECH**

# Power on Silicon with on-die Magnetics: The Start of a Revolution in Power Delivery and Power Management for SoC's and High Performance Applications

Ted DiBene

Intel

USA

# Abstract:

"Power delivery for advanced platforms, from consumer electronics to large servers is becoming very challenging. Sophisticated power management on these platforms, particularly in the high power devices, has been ongoing for some time but much, much more is needed. Until very recently, the problems with on-die power delivery have resulted in low current and low efficiency indicating that it might be a while before this technology was mature enough to be introduced into products. However, this has now changed. This presentation will illustrate some of the platform level challenges and will then discuss in detail a technology that has broken the mold in on-die power delivery with magnetics and will show a device that has the capability of powering an entire server platform with a device the size of a fingernail."

#### Bio:

J. Ted DiBene II is currently a lead silicon power architect at Intel advancing both silicon and system power management. His recent focus has been in power management for microprocessors and other silicon devices including SoC's. Prior to that, Dr. DiBene was the lead architect and senior technologist for a highly advanced integrated silicon power chip inside of Intel. Along with his background in power he has spent a large portion of this time on system architecture. Prior to working at Intel, Dr. DiBene was the chief technology officer at INCEP Technologies, a startup in San Diego. He has been involved in advanced signal integrity, power system management, and platform research and development since the late 80's and has brought many products thru the development process over his career. Dr. DiBene holds a BSEE from UC Santa Barbara as well as an MSEE and PhD in Applied Physics and Electrical Engineering from UC San Diego. He holds 26 patents and has authored over 50 papers in the area of power, signal integrity, and thermal. He is an affiliate professor at the University of Washington and spends his spare time volunteering his time to education of bio-diesel and other energy conservation efforts at high schools.

# Session 1: System Architectures compatible with PwrSoC

Session Co-Chairs: Francesco Carobolante, Ed Stanford, Bruno Allard, José Cobos

Potential application areas for on-chip or highly integrated power supplies include mobile/battery powered devices, microprocessor power supplies, power management for RF transmitters, energy harvesting, etc. This session addresses the key system-level issues brought out by power supply on chip and other power integration techniques. The session will also discuss the requirements, constraints and trade-offs (i.e. performance, cost, complexity) in such systems with a view to defining the potential benefits of power supply integration. Other issues to be discussed will include: suitable input voltages, single or 2-stage conversion, point of load, integration with load.

| 10:15 – 10:40 | Aleksandar Prodic<br>UNIVERSITY OF TORONTO<br>Canada | High-Performance Mixed-Signal<br>Controllers for On-Chip<br>Integrated SMPS                                    |

|---------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 10:40 - 11:05 | Alex Vainberg<br>National Semiconductor<br>USA       | Adaptive Voltage Scaling (AVS)<br>Technology                                                                   |

| 11:05 - 11:35 | Breakou                                              | ee Hotel<br>JT Rooм<br>ea Break                                                                                |

| 11:35 - 12:00 | Dominik Schmidt<br>Intel<br>USA                      | Challenges and Solutions:<br>Power Delivery and Regulation<br>in NanoCMOS SoCs                                 |

| 12:00 - 12:25 | Hans Meyvaert<br>ESAT MICAS K.U. LEUVEN<br>Belgium   | The importance of fully-<br>integrated CMOS: Cost Effective<br>Integrated DC-DC Converters                     |

| 12:25 - 12:50 | William O. Keese<br>National Semiconductor, USA      | Power Management Design<br>Challenges and Techniques for<br>Power Amplifiers in 2G/3G/4G<br>Multimode Handsets |

| 12:50 - 14:00 |                                                      | ee Hotel<br>nch                                                                                                |

# High Performance Mixed Signal Controllers for On-Chip Integrated SMPS Aleksandar Prodic

University of Toronto, Canada

### Abstract:

This paper gives a review of emerging digital and mixed-signal control methods and architectures for on-chip integrated dc-dc switch-mode power supplies (SMPS). The paper is divided into three main parts.

First, it discusses practical implementation problems of digital controllers and shows architectures enabling operation of at ultra high switching frequencies (beyond 100 MHz) allowing significant minimization of the power stage components.

The second part addresses dynamic response of controllers and associated problems of the output filter overdesign creating challenges in on-chip integration of the filtering components. In this part mixed-signal control solutions for obtaining minimum output filter size, defined by the physical limitations of a given power stage, is shown. The presented mixed-signal controller does not require any prior knowledge about the components values and, as such, eliminates the need for custom design.

In the final part, load-interactive controllers and advanced SMPS topologies further minimizing the size of the reactive components and improving power processing efficiency are shown. Theoretically, the presented load-interactive solutions allow drastic reduction of the filtering components, such that their size is limited by the output ripple value only.

# Bio:

Aleksandar Prodic is an associate professor at the ECE department of the University of Toronto, where, in 2004, he formed Laboratory for Power Management and Integrated SMPS. He received his Ph.D. and M.Sc. degrees from the University of Colorado in Boulder, and Dipl. Ing. degree from the University of Novi Sad in Serbia.

His research interests include digital and mixed-signal control of low to medium power high-frequency SMPS, mixed-signal IC design for power electronics, and converter topologies.

In this area he has more than 70 journal and conference publications.

Prof Prodic a recipient of IEEE Power Electronics Transactions Paper Award, and multiple IEEE conference paper prizes. He is especially proud of two Excellence in Teaching Awards, elected and given by the University of Toronto undergraduate students.

# Adaptive Voltage Scaling (AVS) Technology

# Alex Vainberg

National Semiconductor, USA

# Abstract:

With the emphasis on lowering power consumption a concern for system designers, National Semiconductor has pioneered a technology for reducing the energy consumed by large-scale CMOS ASICs and other digital systems on a chip (SoCs).

This technology is called Adaptive Voltage Scaling (AVS) which can reduce the overall energy consumption by 40% or more. AVS is a closed-loop control system that not only handles process variation between devices, but it also handles shifts in temperature, digital load, and process aging.

# Bio:

B.Sc. of Engineering from Technology Institute in Haifa, Israel

M.Sc. Electrical Engineering from Tel-Aviv University, Israel

Worked on different engineering and management positions at Tower, Jazz Semiconductor, Novelics and National Semiconductor.

Has an expertise in intellectual property development, foundry and mixed-signal design

# Challenges and Solutions: Power Delivery and Regulation in NanoCMOS SoCs

Dominik Schmidt

Intel, USA

#### Abstract:

As geometries scale to 32nm and below, the voltage-handling capability of CMOS systems is coming under increasing strain. The core transistors and SRAM cells are constrained to mV levels, and even the periphery devices no longer offer a dependable interface to system voltages. At the same time, voltage regulation and conversion systems can inject unacceptable noise into the substrate, with ever more complex power routing schemes and ground-plane management. As with other aspects of CMOS scaling, these problems come with opportunities, such as potentially lower power conversion losses due to improved switching, SoC-level quasiadiabatic power management techniques and increasing integration of regulation sub-systems on the nanoCMOS die. To balance these tradeoffs requires a careful re-assessment of the overall SoC design process, including new EDA tools and circuit techniques.

#### Bio:

Dominik Schmidt, M.S.M., Ph.D., PE has been working in the semiconductor industry for 20 years. He earned his EE doctorate from Stanford in 2003. He was at Altera working in reconfigurable logic and has worked with Sharp, TI, Cypress and TSMC. He co-founded Pixel Devices International (PDI) in 1997, one of the first companies to offer CMOS imaging chips. After PDI was acquired by Aglient he founed Airify Communications, specializing in multi-protocol wireless chip design. Following the acquisition of Airify, Dr. Schmidt is now Director of Engineering at Intel Corporation, where he is leading the introduction of next generation mixed-signal processes. He has also worked for the Stanford Linear Accelerator and Lawrence Berkeley National Laboratory on several advanced projects, and consulted for several large companies and startups in the mixed-signal and RF design areas. He has taught at UC Extension since 2000 and also taught at Tsinghua University in Beijing and the Swedish Royal Institute. He is wiring a graduate textbook on RF Design for Elsevier Press. He is also a Lieutenant with the US Coast Guard.

# The Importance of Fully-Integrated CMOS: Cost Effective Integrated DC-DC Converters

Hans Meyvaert

ESAT MICAS K.U. Leuven, Belgium

### Abstract:

Scaling of CMOS is enabling ever more complex systems to be fully-integrated on a single die, this results in various System on Chip (SoC) designs with advanced functionality available at ever lower processing cost. Transistor supply voltages are low in these advanced CMOS technologies in order to reduce power consumption. At the same time battery supply voltages remain constant or even increase to enable a higher energy density. This creates a gap that cannot be solved by the well known linear regulator technology due to their poor associated efficiency.

Integrated switched-mode DC-DC converters are a much better choice to close this gap in terms of conversion efficiency. As a result, switching converters are able to increase the autonomy in mobile devices, thereby reducing battery constraints. Moreover, they are also crucial in high-end designs such as CPU' s and SoC' s by avoiding excess power losses and alleviating thermal issues.

Research at the MICAS (K.U.Leuven) laboratory has explored the field of both fully-integrated inductive and fully-integrated capacitive converters. Since 2006 this has resulted in more than 13 prototypes of fully-integrated DC-DC converters in standard CMOS.

In these prototypes various specifications important for DC-DC conversion are targeted. These include high efficiency (up to 88%), low ripple (down to 0.5%), reconfigurability, high power density (213mW/mm2), large conversion ratio (10X) and tight control (PID, hysteretic,...).

This presentation will give an overview of the results produced by the research conducted at MICAS. It will go deeper into the fundamental restrictions of fully-integrated DC-DC converters in standard CMOS. But also the opportunities of on die power management.

#### Bio:

Hans Meyvaert was born in Sint-Truiden, Belgium, in 1985. He received the M.Sc. degree in electrical engineering from the Katholieke Universiteit Leuven (K.U.Leuven), Belgium, in 2009.

Currently he is a research assistant at the ESAT-MICAS Laboratory of the same university where he is working towards the Ph.D. degree. His research interest includes on die power management in general and currently capacitive DC-DC converters in specific.

# Power Management Design Challenges and Techniques for Power Amplifiers in 2G/3G/4G Multimode Handsets

William O. Keese

National Semiconductor, USA

#### Abstract:

The linearity requirements and complexity of the handset RF Front End to support multimode multi-band architectures place a premium on power amplifier performance. With the explosion of high-speed data services on the radio channel and resultant increase in average output power, the importance of the transmitter efficiency is emphasized even more. A variable PA power supply offers superior and unique performance benefits for improving talk time of mobile phones by maximizing utilization of battery power consumed.

This presentation reviews the technical advantages of implementing DCDC converters in mobile transmitters and discusses the relative efficiency and current consumption improvements. Recent advancements in power management design technology and system techniques to address the specific challenges in meeting multimode performance requirements will be discussed.

#### Bio:

Senior member of Technical Staff at National Semiconductor, leads the system definition and architecture of RF power supplies for handset power amplifiers. Previously he has been in the forefront of innovation and development of Frequency Synthesizer, Femtocell, and RFIC wireless communications devices and architecture.

# Session 2: Technologies and Devices to Enable PwrSoC

Session Co-Chairs: Yan-Fei Liu, John Shen, Shuming Xu

This session discusses active switching power devices suitable to facilitate various PwrSoC concepts, ranging from traditional BCDMOS to vertical/lateral hybrid devices and SOI RESURF devices. The focus will be on switching frequency from multi-MHz up to radio frequency (RF), process compatibility, and special power electronics requirements such as SOA and energy capability of different CMOS-based device technologies.

| 14:00 - 14:25 | Anco Heringa<br>NXP,<br>NETHERLANDS                      | High Voltage transistors for<br>SoCs in baseline CMOS                                    |

|---------------|----------------------------------------------------------|------------------------------------------------------------------------------------------|

| 14:25 - 14:50 | Shuming Xu<br>Texas Instruments,<br>USA                  | NexFET Technology: New<br>Technology Enables High Power<br>Density                       |

| 14:50 - 15:15 | Paul Chow<br>Rensselaer Polytechnic<br>Institute,<br>USA | GaAs p-HEMT-based Power ICs<br>for High Frequency Switching<br>Converter Applications    |

| 15:15 - 15:45 | River Lee Hotel<br>Breakout Room<br>Coffee/Tea Break     |                                                                                          |

| 15:45 - 16:05 | Sameer Pendharkar<br>Texas Instruments,<br>USA           | Mixed signal technologies<br>enabling PwrSoC and PwrSiP                                  |

| 16:05 - 16:30 | Sami Ajram<br>SL3J Systems<br>France                     | Power train scaling, high<br>frequency cross talk and its<br>impact on controller design |

DC-DC convertors on silicon next generation technology for emerging business opportunities

# High Voltage Transistors for SoCs in Baseline CMOS

Anco Heringa

NXP, Netherlands

# Abstract:

In many modern IC applications the supply voltage has to be converted to the lower voltage as needed by advanced CMOS technology. Preferably the power management enabled by HV-transistors, should be integrated with the advanced CMOS circuits in baseline CMOS technology offering a one-chip solution which guarantees cost competiveness and short time to market.

Both advanced CMOS at one hand and the high voltage transistors as needed in SoCs on the other hand have their own figures of merit with feature size and clock speed for CMOS and breakdown voltage, power handling, on-resistance and high frequency as key features for HV-transistors. We will show that the extreme feature size and process control from advanced CMOS can be exploited for the implementation of HV-transistors. By smart-layout of shallow trench, implants and poly/field plates HV-transistors can be realized in a base line state of the art sub-100 nm bulk foundry CMOS or PD-SOI CMOS process with figures of merit on par with transistors in special purpose HV-processes. Also the Hot-Carrier/reliability characteristics of these transistors, often being a major limiting factor, meet the requirements for a 10 year operational life time.

# **Biographies**

# Anco Heringa

Anco Heringa graduated in technical physics at the University of Groningen in 1977. From 1977-1987 he did research on medical physics and cardiophysics at the Catholic University Nijmegen. From 1987-2002 he was consultant in process, device and interconnect modelling in Philips Research and Philips Semiconductors. Since 2002 he is with Philips Research, now NXP Semiconductors, Leuven, Belgium, working on advanced CMOS and on integrated high voltage devices.

# Jan Šonský

Jan Šonský has received MSc. in solid state physics at Czech Technical University in Prague, Czech Republic, in 1997 and his PhD degree at Delft University of Technology, The Netherlands, in 2002 on ultra-low noise silicon X-ray detectors. He joined Philips Research, now NXP Semiconductors, Leuven, Belgium, in 2002, where he has been working on integrated power management, RF power and SOI processes, and power conversion discrete technologies, including GaN. He serves on technical committees of ISPSD and IEDM, holds over 25 patents/patent applications in semiconductors and published on radiation detectors and high voltage and smart power technologies.

# NexFET Technology: New Technology Enables High Power Density

Shuming Xu

Texas Instruments, USA

# Abstract:

In this presentation, a new device technology NexFET will be discussed. It improved the Figure of Merit (FOM) drastically, allowing high frequency operation, reducing the filter size. Scaling down to low voltage, NexFET shows great reduction of cost and better performance, promising two stage operation for MHz operation. The second generation NexFET is configured as source on the bottom of the substrate, allowing stacking the high side switch device on the low side synchronies device directly: this reduces the footprint by 50%, eliminates three parasitic inductors out of four. Furthermore, it removed the PCB parasitic resistance between the two devices in the traditional way. With the stack die power block, high frequency and small active block can be achieved simultaneously.

# Bio:

Shuming Xu, graduated from Jiaotong University, Xian China in 1982. Received his Master's degree from Shaanixi Microelectronics Institute in 1987 and got the Ph. D from University of Bremen, Germany in 1997. Shuming worked in Daimler-Benz AG in Germany, IME in Singapore, Vishay Siliconix in CA, where he worked for power MOSFET development based on Trench technology; From 2001 to 2004, Shuming worked at Agere Systems and worked for RF LDMOS development. In the beginning of 2005, he co-founded a company called Ciclon Semiconductor and served as VP of technology. Where lead the development of NexFET. He is currently the Chief Technologist in Power Stage of Power Business Unit, Texas Instruments.

# GaAs p-HEMT-based Power ICs for High Frequency Switching Converter Applications

Paul Chow

Renesselaer Polytechnic Institute, USA

#### Abstract:

Switching regulators operating at 100s of Megahertz would enable high bandwidth power supplies capable of catering to the fast load transients especially in point of load converters in portable battery powered appliances. Such switching frequencies also allow for the use of air-core inductors, which can be integrated on chip or on package to minimize the form factor and achieve high power densities. However, the efficiency of hard-switched converters decreases drastically at these frequencies because of the gate driver and output switching loss in the power transistor, which are proportional to the gate charge of the FET used. Due to their improved material properties and device structure, GaAs pHEMTs, which are Schottky gate, field-effect transistors with a high mobility 2DEG channel, are shown to have a 2 to 4x advantage in figure of merit over silicon N-MOSFETs with the same voltage rating.

Enhancement mode low leakage pHEMTs are available through commercial foundries and are suitable for monolithic high frequency power supplies. We demonstrate a 4.5V input, 0.5-3.3V output, 1-2A multiphase buck converter in a 0.5um E/D pHEMT process with the power transistors, gate drivers and charge pumps integrated ON chip. A thick metal air-core coupled spiral inductor fabricated on a GaAs substrate is used in the output filter. The converter is capable of operating at a switching frequency of up to 200MHz and achieves a peak efficiency of 86%.

Bio:

#### Professor, RPI

#### Dept. of Electrical, Computer and Systems Engineering

**Education:** B.A., Mathematics and Physics, Augustana College (S. Dak.); M.S., Materials Science, Columbia University; Ph.D., Electrical Engineering, Rensselaer Polytechnic Institute (RPI).

**Experience:** Dr. Chow was a member of the technical staff at GE-CRD from 1977 to 1989. Since 1989, he has been with RPI, where he is now professor of the Electrical, Computer and Systems Engineering Department. He has been working in the power semiconductor device area since 1982. His present research activities include novel device concepts, processing and circuit models for high-voltage silicon, GaAs and wide bandgap (particularly SiC and GaN) semiconductor power devices. He has published over 100 papers in scientific journals, has contributed seven chapters in technical textbooks, and has filed over fifteen patents. He is a fellow of the IEEE and a member of the Electrochemical Society.

# Mixed Signal Technologies Enabling PwrSoC and PwrSiP

Sameer Pendharkar

Texas Instruments, USA

# Abstracts:

This presentation will focus on recent advances and innovations in mixed signal bicmos-dmos technologies that enable complex power SoCs as well as multi-chip power SiPs. Key performance metrics and robustness (short term and long term) criteria and characterization techniques will be presented. While the advances in lithography and processing help with SoC design, it also introduces challenges in monolithic integration of digital, analog, power and passives which drive new integration techniques and power device and esd design. The presentation will also touch on a few packaging techniques that enable SiP and help integrate disparate technologies to improve overall system performance.

#### Bio:

Sameer Pendharkar graduated in Electrical Engineering at the University of Wisconsin-Madison in 1996 Since 1996, he has been at Texas Instruments Inc., Dallas, USA where he is presently a TI-Fellow and manager of high voltage and power component development team. His group's main focus is defining integrated power roadmap and designing and developing high voltage and high power devices and ESD components for numerous BiCMOS and High Voltage CMOS technologies. He has published more than 50 papers and has more than 50 issued patents in the general area of semiconductor devices and processing.

# Power Train Scaling, High Frequency Cross Talk and its Impact On Controller Design

Sami Ajram

SL3J Systems

#### Abstract:

The emergence low cost Chip Scale and Flip Chip packaging techniques for standard power ICs enabled a significant push of the switching frequency of DCDC converters and allowed several suppliers to introduce 4, 6, and 9MHz DCDCs that fit in a 6 mm<sup>2</sup> PCB area. Designers start realizing that scaling the power switches becomes a complex equation that not only includes conduction and switching losses of the power switch but also wasted reactive power that stores in the extrinsic parasitics.

Complex PMICs based on 0.18um and 0.13um extended drain processes offer higher capabilities toward 50MHz to 200MHz switching frequency but the challenge is quite similar regarding the criteria for better scaling the power switches, reducing the die area, reducing the electrical overstress and managing the extrinsic power losses. The presentation provides simple rules and a simple theory that help the designer realize an optimum device scaling.

The most concerning challenge from design point of view comes from the controller that has to be radically changed because of the short on time duration and the difficulty on using blanking techniques due to the non-damped HF ringing after each power switching event. The presentation highlights the crosstalk mechanisms and suggests ideas and techniques for solving such issues.

#### Bio:

Dr. Sami Ajram has 16 years experience in Electronics industry. He received his Ph.D. in 1998 from the University of Sciences and Technologies of Lille and pursued his research activities at the IEMN (http://www.iemn.univ-lille1.fr) pioneering 100MHz DCDC converter design based on IIIV power switches and PCB printed power inductors. He joined the ASIC department at ATMEL Rousset in 2000 where he led the design activity of HF clock synthesizers and low power front end sensors. In 2006, he joined Fairchild Semiconductor as Marketing Manager in charge of the development of High Frequency DCDC converters dedicated Dynamic Voltage Biasing of GSM / WCDMA RFPAs. He recently started SL3J SYSTEMS, a small design center focusing on Power Management and electronic solutions for handheld devices. He has 5 granted patents, published several papers and he received a Best Paper award from the IEEE PEL society in 2001.

# **Session 4a: Integrated Passives: Magnetics**

# Charles R. Sullivan, Maeve Duffy, Matthew Wilkowski, Florian Herrault, Saibal Roy

Inductors are key elements for dc-to-dc converters. For power supply on chip, inductors require novel and improved materials and integration techniques. In particular, multi-MHz, soft magnetic materials, deposited in a CMOS-compatible technique, are needed. The issues to be addressed in this session include:

- Magnetic integration opportunities and challenges.

- Multi-MHz magnetics thin film magnetic materials and deposition techniques.

- Material compatibility issues for integration on top of active silicon.

- Achievable power density and efficiency.

| Saibal Roy                          | Challenges in magnetics for     |  |

|-------------------------------------|---------------------------------|--|

| 5                                   | PwrSoC - Development in high-   |  |

| IRELAND                             | frequency magnetics, materials, |  |

|                                     | and integration                 |  |

| Donald .S. Gardner                  | Integrated On-Chip Inductors    |  |

| INTEL,                              | Using Magnetic Material         |  |

| USA                                 |                                 |  |

| Sarah Bedair                        | Thin Film Piezotransformers for |  |

| US ARMY RESEARCH LABS,              | High Frequency Switched Mode    |  |

| USA                                 | Power Supplies                  |  |

|                                     | Lamination-Based Technology     |  |

|                                     | for High Performance Metallic   |  |

|                                     | Magnetic Cores                  |  |

| _                                   | ee Hotel                        |  |

| Breakout Room                       |                                 |  |

| Poster Session and Coffee/Tea Break |                                 |  |

|                                     | Low-Temperature Deposited       |  |

| -                                   | Metallic Magnetic Films and     |  |

| USA                                 | Ferrite Films and Their         |  |

|                                     | Applications in Integrated RF   |  |

|                                     | Magnetic Devices                |  |

| Matthew Wilkowski                   | Magnetics on Wafer:             |  |

|                                     | Transitioning From Prototype    |  |

|                                     | to Manufacturing                |  |

|                                     | "PwrSoC or Not"                 |  |

| River Lee Hotel<br>Lunch            |                                 |  |

|                                     |                                 |  |

# Challenges in magnetics for PwrSoC - Development in high-frequency magnetics, materials and integration

#### Saibal Roy

#### Tyndall National Institute, Ireland

#### Abstract:

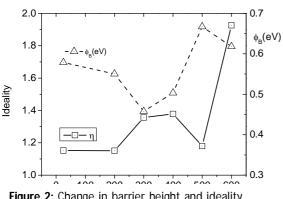

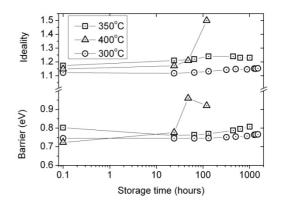

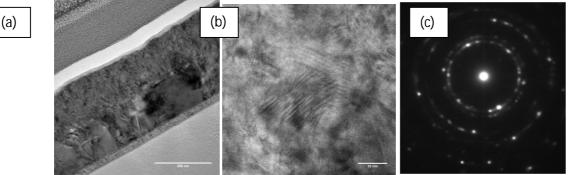

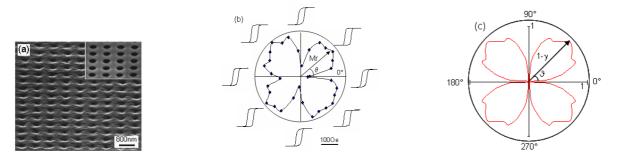

To enable the next-generation of highly-integratable, Power-RF magnetic components for on-chip converters, challenges must be overcome in various facets, such as device design, modelling, next generation magnetic materials and integration. Accurate modelling is the basis of any thorough understanding of the properties of a ferromagnetic thin-film, necessary to correctly predict the effects of thin-film deposition in a miniaturized device. Starting from characterisations of as-deposited materials, analytic models are applied to predict the effects of shape and thickness on the permeability of a structure. As well, the effects on inductance and loss at high-frequency of a conductive seed layer have been analytically modelled, which is of particular necessity for electrodeposited conformal thin-films.

To miniaturise the inductive components, magnetic materials are required which exhibit low loss at high frequencies. The features of these materials must include a high anisotropy field, low hysteresis, high saturation flux densities and low eddy current losses. To meet these requirements novel nanostructured magnetic materials are being synthesised. We have considered a number of different electroplated, high-frequency nanostructured magnetic materials such as NiFe, CoNiFe, and CoP. Electroplating is compatible with the deposition of conformal and relatively thick layers i.e. several Im to 10's of Im to achieve required power density. However eddy current losses due to the lower resistivity of the electroplated films mean that thick layers will have an inferior frequency response. Typically, films are developed with pulse reverse plating to generate Co rich and Co deficient 'multi-nano-layers' having improved saturation magnetisation and better frequency response. The plating parameters have been optimised in order to produce a material with low loss and a high permeability of around 700 retained up to 103 MHz for a sample with a thickness of 1.7 Im, Bs of 1.2T and a resistivity of 136IOhm cm. Some of the developed nano-materials have been integrated in the next generation of micro-inductors fabricated at Tyndall.

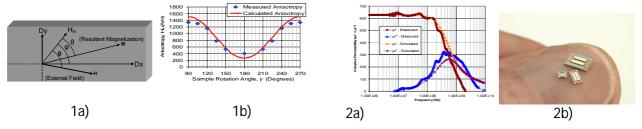

1a) Schematic representation of a magnetic thin-film core illustrating components of anisotropy

1b) Measured and simulated anisotropy of a thin-film CoP layer as a function of sample rotation

2a) Wide-band complex permeability of a 1.7  $\mu m$  thick layer of Co\_{91.5}P\_{8.5} Measured and simulated including Cu seed layer

2b) Image of fabricated micro-inductors at Tyndall National Institute

#### Bio:

**Dr. Saibal Roy** is working as *Senior Scientist* in the Microsystems Centre of Tyndall National Institute, Cork, Ireland. He is Science Foundation Ireland Principal Investigator (SFI PI) and R&D leader in the Micropower - Nanomagnetics research area. He did his M.Sc. in Physics from the Indian Institute of Technology and received his Ph.D. working on advanced nanostructured materials from IACS in 1994. Since receiving his Ph.D, his professional experiences include 13 years academic and 3 years industrial research experiences; particularly he has served both in academia and industry as a senior scientist while leading research groups. Dr Roy's present research interests at Tyndall include how engineered nanostructures could be employed for potential benefits for micron scale devices from beyond Moore (BM) to More than Moore (MtM) scenario. Since joining the Tyndall National Institute, Dr. Roy was able to bring substantial (€ 3.28 Million) government and corporate research funding. Recently Dr. Roy has been honoured by the president of University College Cork (UCC) for licensing the patented technology to INTEL. Some of his published work featured in BBC technology news; Daily Mail; Sunday Telegraph and in American radio. His recent microfabricated high frequency inductor work has been described as a global benchmark for integrated magnetics by NXP (PHILIPS). Dr. Roy has supervised several PhD and Post doctoral fellows at Microelectronics Dept., University College Cork, and at Tyndall National Institute. He has served as a member of several programme committees, chaired sessions and delivered invited talks in many International Conferences / Research Institutes. So far, he has filed 5 international patents, written 1 book chapter and published 90 papers with h index 14.

# Integrated On-Chip Inductors Using Magnetic Materials

Donald S. Gardner

Intel, USA

#### Abstract:

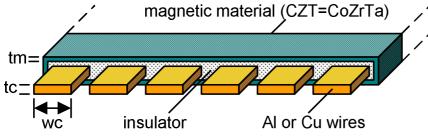

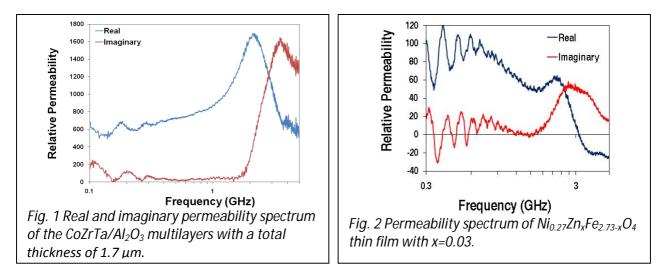

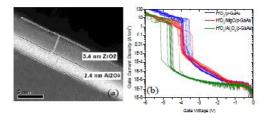

Rapidly increasing input current of microprocessors has resulted in rising costs and motherboard real estate occupied by the power delivery system. The current DC-DC converters on microprocessor motherboards are switching at or near KHz frequencies because of the strict efficiency requirements. Significantly higher frequency switching DC-DC converters in a CMOS process has been demonstrated for microprocessor power delivery [1-2]. The ultimate goal is to have a fully integrated converter with on-chip inductors to provide fine-grain power distribution and fast response time. On-chip inductors with magnetic material were integrated into both advanced 130 and 90 nm CMOS processes [3]. Increases in inductance of over 30 times corresponding to an inductance density of up to 1,700 nH/mm<sup>2</sup> were demonstrated [4], significantly greater than air-core and other on-chip inductors with magnetic material. With such improvements, the effects of eddy currents, skin effect, and proximity effect become clearly visible at higher frequencies. The CoZrTa was chosen for its good combination of high permeability, good high-temperature stability (>250 °C), high saturation magnetization, low magnetostriction, high resistivity, minimal hysteretic loss, and compatibility with silicon technology. The CoZrTa alloy can operate at frequencies up to 9.8 GHz, but trade-offs exist between frequency, inductance, and quality factor. Techniques are presented to extract a *sheet inductance* and examine the effects of magnetic vias (vias that allow complete closure in the magnetic flux) on the inductors. The DC resistance is also important for converters and was 0.04 ohms with quality factors of 8 when using thick copper metallization and thick CoZrTa (see Fig. 1).

Fig. 1. Inductor structure with magnetic material

- [1] G. Schrom, et al., "A 480-MHz, multi-phase interleaved buck DC-DC converter with hysteretic control," in *IEEE PESC*, 2004, pp. 4702-4707 Vol.6.

- [2] G. Schrom, et al., "A 100 MHz Eight-Phase Buck Converter Delivering 12A in 25mm2 Using Air-Core Inductors," in Appl. Power Electronics Conf., 2007, pp. 727-730.

- [3] D. S. Gardner, *et al.*, "Integrated on-chip inductors using magnetic material (invited)," *Journal of Applied Physics*, vol. 103, p. 07E927, Apr 2008.

- [4] D. S. Gardner, *et al.*, "Review of On-Chip Inductor Structures With Magnetic Films," *IEEE Transactions on Magnetics*, vol. 45, pp. 4760-4766, Oct 2009.

#### Bio:

**Donald Gardner** has been with Intel Corporation since 1991 and is currently a Principal Engineer in Intel Research. He received his PhD in Electrical Engineering from Stanford University and is currently a visiting scholar at Stanford. Donald is the inventor or co-inventor of 64 issued patents including for inductors using magnetic materials, reflowed copper for interconnections, layered aluminum interconnections, and embedded decoupling capacitors. He has received Intel's highest technical award "For Fundamentally Changing Platform Power Delivery with Integrated Voltage Regulators and Magnetic Inductors on CMOS". Donald has published over 135 electrical engineering, materials science and computer science papers in journals and conferences. He has received three Best Paper and Poster awards at international conferences and over 1,700 authors have cited his publications. Donald invented a copper technology and used it to fabricate the first working chip with copper-based interconnections at Intel, then published on copper size effects that has been referred to as the first study that showed surface scattering and grain size to be a potential interconnect scaling issue. He pioneered techniques for the study of metallic films using *in-situ* mechanical stress measurements that are widely cited in the literature. He also invented an Al alloy/Ti metallization for interconnections as part of his PhD thesis studies that was later widely used by industry in microchips. Donald has had appointments as a visiting research scientist at Hitachi Research Labs in Japan and also at Stanford University. He enjoys bringing new life to old technologies by blending them with new scientific technologies or integrating them with new materials. His current interests include future microprocessor technology, magnetic materials for inductors, silicon-based optoelectronic devices, new materials integration and nanostructure design and devices.

#### DC-DC convertors on silicon

next generation technology for emerging business opportunities

# Thin Film Piezotransformers for High Frequency Switched Mode Power Supplies

Sarah Bedair

US Army Research Labs, USA

#### Abstract:

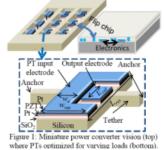

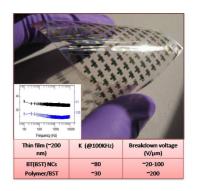

There is interest in power units with a single battery input and multiple output voltages for mobile micro-systems which are palm-sized and below [1]. Implementation of these units using larger COTS switched mode converters would cripple the entire system or limit functionality. Power converter size reduction motivates increasing the switching frequency (>20MHz), further reducing passive components' size. An array of thin film, high frequency piezoelectric resonant transformers (PTs), each of which is impedance matched

to various loads, is envisioned (Fig.1-top). The predicted performance (AC/AC, AC/DC) of PTs in a power converter is evaluated where electrodes may be lithographically defined for load impedance-matching. Although there are challenges with thin film PTs including depoling and power handling, they present a promising, alternate technology to thin film magnetic transformers where the magnetic material losses limit high frequency implementation.

A performance model of a 21.4MHz (190µm x 40µm x 11µm) length extensional thin film PT using lead-zirconium-titanate is presented [2]. The extracted series motional resistance, Rx, inductance,

Lr, and capacitance, Cr, (Q=2023) are  $50\Omega$ , 0.75mH and 74fF, respectively [3]. The input/output electrode coverage is used to tailor to various loads and specifications including efficiency and voltage boosts. The performance may be tailored through decreasing the output electrode area which is traded for input electrode coverage (Fig-1). Although this comes at a cost of reduced electromechanical coupling, the tradeoffs in efficiency and boosts over higher Rx are superior under higher resistive load, lower power regimes where voltage boosts are desired. Expected performances are shown for various output electrode coverage, 100%\*Lout/Lres. For example, if

50% efficiency can be tolerated, voltage boosts (normalized power delivered) of  $3.53(156\mu W/V2)$ , 3.47(750µW/V2) and 2.80(2.6mW/V2) may be achieved by designing the output electrode coverage at 100%\*Lout/Lres=1%, 5% and 20% for loads of 80, 16 and 3kΩ, respectively. Simulations of the PT in an AC/DC configuration (Table-1) at the optimal frequency show that boosts up to 8.2 at 29% efficiency and 0.4% ripple may be achieved.

[1] B. Morgan, S. S. Bedair, W. Nothwang, D. Arnold, C. Meyer, B. Bowers, A. Sopeju, C.

Dougherty, X. Lin, and R. Bashirulla, "Micro-power requirements & conversion for autonomous Microsystems" NATO Specialist Meeting on Energy Technologies and Energy Management for Portable Power Systems for Military Applications, Slovenia, May 2009.

[2] S. S. Bedair, J. S. Pulskamp, B. Morgan, and R. G. Polcawich, "Performance model of electrode tailored thin film piezoelectric transformers for high frequency switched mode power supplies", PowerMEMS 2009, p. 435, Dec. 2009. [3] H. Chandrahalim, S. A. Bhave, R. Polcawich, J. Pulskamp, D. Judy, R. Kaul, and M. Dubey, "Performance comparison of Pb(Zr0.52Ti0.48O3-only and Pb(Zr0.52Ti0.48O3-on-silicon resonators", Applied Physics Letters, 93, p. 233504-1 (2008).

#### Bio:

Sarah S. Bedair is an Electronics Engineer at the US Army Research Laboratory (ARL) in Adelphi, Maryland. Prior to joining ARL as an employee, she was an Oak Ridge Associated Universities (ORAU) Postdoctoral Fellow. She received her B.S. (2002) degree in Applied Sciences from the University of North Carolina at Chapel Hill. She also received her M.S. (2004) and Ph.D. (2008) degrees from Carnegie Mellon University from the Electrical and Computer Engineering Department where she conducted research on CMOS-MEMS gas chemical sensors and MEMS resonator / oscillators. During her studies she was awarded the UNC-Chapel Hill James D. Crawford Award (2002) and the Phillip and Marsha Dowd-ICES Fellowship (2005) and was a member of the Phi Beta Kappa and Eta Kappa Nu honor societies. She also received the 2010 Excellence in Federal Career - Rookie of the Year Award (Technical & Scientific) in addition to the 2009 Army Research Laboratory Research and Development Award. Her research interests include high frequency switched mode power supplies, high frequency piezoelectric resonators / transformers and the fabrication of integrated MEMS passives.

> DC-DC convertors on silicon next generation technology for emerging business opportunities

# Lamination-Based Technology for High Performance Metallic Magnetic Cores

Florian Herrault

Georgia Tech, USA

#### Abstract:

Traditional passive elements in power conversion technologies, inductors and capacitors, are comprised of combinations of electrical conductors and materials of high magnetic permeability or high electric permittivity. Microelectromechanical (MEMS) researchers have been working on integrating these structures with integrated circuitry for many years. More recently, MEMS technology is being utilized to improve the performance of the materials themselves. This presentation will give an example of the use of MEMS to improve the properties of passive elements. Specifically, we have developed highly-laminated metallic magnetic alloys with suppressed eddy current losses for high-frequency power converters.

Iron alloys are used as magnetic core materials for inductors at low frequency, due in part to their extremely high value of saturation flux density. However, at higher frequencies (such as the continually increasing frequencies of switching converters), induced eddy current losses make the use of iron alloys challenging. Ferrites are therefore used due to their high electrical resistivity, even though they have low saturation flux density, resulting in relatively bulky inductor cores. Although laminations can be used to suppress eddy currents in iron cores (and are, at power delivery frequencies such as 60 Hz), the thickness of laminations necessary to suppress these currents at switcher frequencies extends into the submicron range. Using MEMS technology, we have developed approaches to realize iron alloy cores with macroscopic total thickness built from many submicron laminations. These cores allow the use of high saturation flux density iron materials in switching converters, potentially greatly shrinking the size of converter modules.

#### Bio:

Florian Herrault received the B.S. and M.S. degrees in physics and materials science and the Ph.D. degree in electrical and electronics engineering from the National Institute of Applied Sciences (INSA), Toulouse, France, in 2003, 2005, and 2009, respectively. However, his Ph.D. research was performed at Georgia Institute of Technology (Georgia Tech), Atlanta. He is currently a Research Engineer with the MicroSensors and MicroActuators Group, Georgia Tech. His current research interests include piezoelectric and electromagnetic actuators, small-scale power generation systems, high-performance magnetics for on-chip power converters, 3-D microelectromechanical systems (MEMS) fabrication, and MEMS-enabled thermal management devices.

# Coupled Analysis of Magnetic Hysteresis and Electromagnetic Filed to Design On-Chip Planar Power Inductor

#### Masahiro Yamaguchi

#### Tohoku University, Japan

#### Abstract:

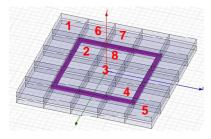

It is important for a planar power inductor for one-chip DC-DC converter to keep required AC inductance under superimposed DC field defined by DC output current. This paper proposes a new design methodology to endure coupled analysis of magnetic hysteresis model and numerical electromagnetic (EM) field simulation to realize more smaller inductor [1]. The Jiles-Atherton static hysteresis model [2] is employed.

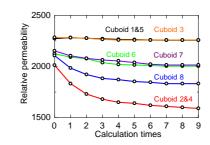

A 5.0 x 5.0 x 0.5 mm<sup>3</sup> size planar rectangular spiral inductor is modeled in a commercial EM simulator (Maxwell 3D, Ansoft Co.), where 2-turn coil is sandwiched by 0.2mm thick MnZn ferrite layers, as shown in Fig. 1. The extracted J-A parameters are; Ms=1.46x10^-6, a=88, c=0.35, k=72 and alpha=0.00017. The conductor carries DC 1.1A and AC ripple 0.1Ap-p. Initially, permeability is assumed as non-linear and non-hysteretic with magnetic field intensity but uniform within the core space. After the first turn of the EM simulation, the permeability is replaced by position-dependent constants based on the J-A model depending on the simulated local flux density. This process was repeated for 9 times to be converged, as shown in Fig. 2. Flux density B on the coil (Cuboids 2 & 4) is B=0.43T and closely to saturation with relatively low permeability of ur=1600 whereas B=0.10T with ur=2300 at the edge of the inductor (Cuboids 1 & 5). Smaller inductor with improved DC-superimposed performance can be developed based on this method.

Fig. 1 Simulation model References

Fig. 2 Local permeability extraction as a result of the proposed coupled analysis

[1] M. Yamaguchi, T. Inagaki, M. Furuta, Y. Lu and S. Muroga, Joint European Magnetic Symposia(JEMS) 2010, Soft-A-oral 370, August 2010, Krakow, Poland.

[2] D. C. Jiles, et al., J. Mag. Mater., 61 (1986) 48.

#### Bio:

- 1984 Ph.D, Dept of Electrical Engineering, Tohoku University

- 1984 Assistant Professor, Dept of Electrical Engineering, Tohoku University

- 1991 Associate Professor, Research Institute of Electrical Communication, Tohoku University

- 2003 Professor, Dept of Electrical Engineering, Tohoku University

#### Academic Society Activities

- 2010 Editor of the IEEE Transactions on Magnetics Conference (Intermag 2010)

- 2003-2009 Program Committee member of the IEEE International Magnetics Conference (Intermag 2003 2009)

- 2005-2009 Member of the Board of Directors, Co-Editor-in-Chief, the Magnetics Society of Japan.

- 2002 2008, General Chairman of the IEEE Magnetics Society 1st to 7th International Workshop on the high frequency micromagnetic devices and materials

- 2007 IEEE Magnetics Society Japan-Sendai Chapter Chair

#### Awards

- 2010, 2004, 1986: Outstanding paper award, The Magnetics Society of Japan

- 2002 Award of the Society of promotion of Scientific measurements "High frequency magnetic field measurements using multilayer shielded-loop coil."

DC-DC convertors on silicon

next generation technology for emerging business opportunities

# Low-Temperature Deposited Metallic Magnetic Films and Ferrite Films and Their Applications in Integrated RF Magnetic Devices

Nian Sun

Northeastern University, USA

#### Abstract:

Integrated magnetic inductors, magnetic transformers and RF magnetic filters, etc. require soft magnetic material that can be deposited at low temperatures and have a high permeability, large saturation magnetization, high resistivity, high ferromagnetic resonance frequency, low loss tangent, etc. In this presentation, we will cover our research on different metallic magnetic films and ferrite films deposited at near room temperature and their applications in integrated RF magnetic devices. These metallic magnetic films include FeCoN, FeCoHf, and CoZrTa/Al<sub>2</sub>O<sub>3</sub> multilayers, etc. High saturation magnetization FeCoN films with a saturation magnetization of 2.4 T were developed with a high relative permeability of 1000, high ferromagnetic resonance frequency of ~2 GHz and a low coercivity of ~1 Oe. In addition, we investigated the composition gradient sputtering method for depositing a series of  $(Fe_xCo_{1,x})_{1,y}Hf_y$  alloy films with different Fe/Co atomic ratios and a small amount of Hf doping, which had a high saturation magnetization of 1.8 ~ 2.2 T. The compositional gradient of the Hf content in Fe-Co-Hf films led to a large in-plane anisotropy field of 200 ~ 500 Oe and a high ferromagnetic resonance frequency of > 7 GHz. We also investigated the magnetic properties of laminated CoZrTa/Al<sub>2</sub>O<sub>3</sub> multilayer films with different periods and a total thickness of ~1.7µm, which show significantly enhanced performance at GHz frequency compared to single layer CoZrTa films with similar thickness. Besides metallic magnetic films, we also fabricated different NiZnCo-ferrite films with high µ, in the GHz range through spin spray deposition at a low temperature of 90°C. The NiZn-ferrite films showed a low magnetic loss tangent tan $\delta_m = \mu''/\mu'$  of ~0.025 between 1~1.5GHz, and a high ferromagnetic resonance frequency of 2.7 GHz. At the same time we have designed, fabricated and tested different RF magnetic devices such as inductors, transformers and filters which showed excellent performance.

#### Bio:

Nian Sun is an associate professor at the Electrical and Computer Engineering Department, Northeastern University. He received his Ph.D. degree from Stanford University. Prior to joining Northeastern University, he was a research scientist at IBM and Hitachi Global Storage Technologies between 2001~2004. Dr. Sun was the recipient of the NSF CAREER Award, ONR Young Investigator Award, USAF Summer Faculty Fellowship, and the first prize IDEMA Fellowship. His research interests include novel magnetic, ferroelectric and multiferroic microwave materials and devices such as antennas, filters, phase shifters, circulators, inductors, transformers, energy harvesting technologies, magnetic sensors, solar cell materials and devices, etc. He has over 80 publications and has >20 patents and patent disclosures.

# Magnetics on Wafer: Transitioning From Prototype to Manufacturing

Matthew Wilkowski

Enpirion, USA

#### Abstract:

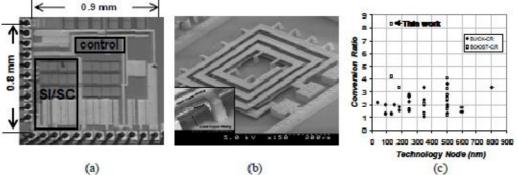

Integration of the magnetic function with the power switches and control function for dc-dc converters has progressed significantly over the past twenty years. There have been numerous publications citing reduction of physical size with acceptable power efficiencies for dc-dc converters with the magnetic function implemented on silicon. With the existence proofs in place for the various fabrication and design methodologies, it is time to drive further improvements in cost, technology acceptance by proliferation of device designs into various applications and availability of certification and field reliability data etc., through commercialization of products.

The cost effective and successful commercialization of magnetics on silicon requires trade-offs between the obvious technical physical and electrical improvements and the constraints of the currently available manufacturing processes with an eye towards future process capabilities as market acceptance warrants the required investments.

Critical performance criteria such as small signal inductance, series resistance, saturation current and large signal ac power loss can be defined for inductor performance for specific levels of device performance as well as for specific combinations of materials, geometries and fabrication technologies. However these levels of performance must be sustainable through the temperature and physical stresses of wafer manufacturing process and the device packaging process. This requires verification of the critical inductor parameters through all stages of the manufacturing process as well as through industry recognized JEDEC device level reliability characterization programs in an effort to identify potential variations and shifts and their appropriate countermeasures.

The insights obtained from manufacturing and reliability characterization of the first generation of commercial devices can be applied to more complex second generation devices which involve greater levels of integration of materials and geometries.

#### Bio: