## Power SoC Vs SiP

Competitive Challenges in High-Volume Applications

**Brian Molloy**

brian.molloy@infineon.com

molloy@ieee.org

- History to understand rational of decision making

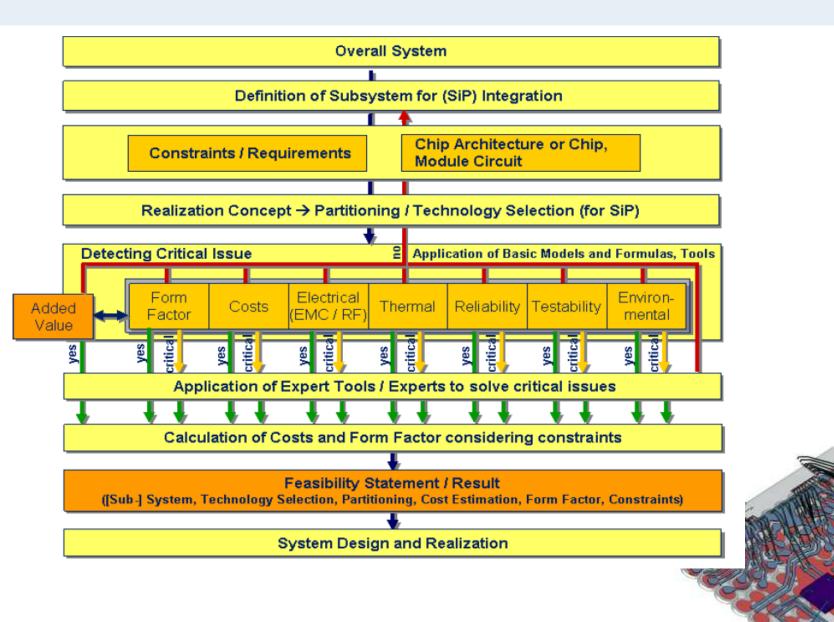

- Processes for SiP Vs SoC Decision Making

- Analysis of commercial challenges and trade-offs.

- Conclusions / Recommendations

## SiP History at Infineon Infineon First complex SiP for Wireless in prod. In 1998 Learnings: "Overengineered" SiP – at least for 1998! SiP comprised total 5 dies with digital and analog baseband, E<sup>2</sup>PROM, SRAM and Flash for cellular handset SIEMENS and Telefonbuch towners Info wares gene Rufnumer eser \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* granding and the second of the 0 The state of the second states and the

#### SiP History at Infineon GSM Power Amplifier Module in production in 2000

- 5 Layers Low-Loss Ceramic Multilayer

- Part Count: 7 Dies and 31 SMD's

- One Amplifier Chain with GaAs-Die and Switched Output Matching

Learning's: Thermal Simulation

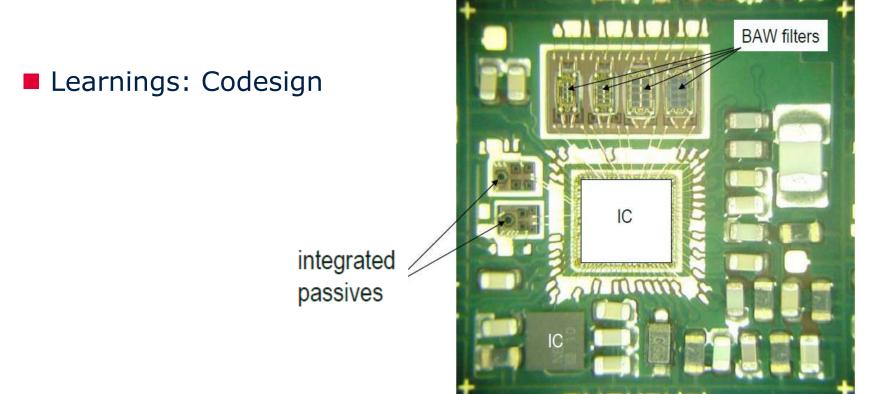

#### SiP - RF module for GSM handsets

- Driver: minaturisation

- Complete RF module in 10mm x 10mm

- 6 dies (transceiver, BAW filter, LDO die) integrated passives and SMD BAW

## Chip Package Board System **Co-Design**

$\bigcirc$

Ŭ

Ę

MA

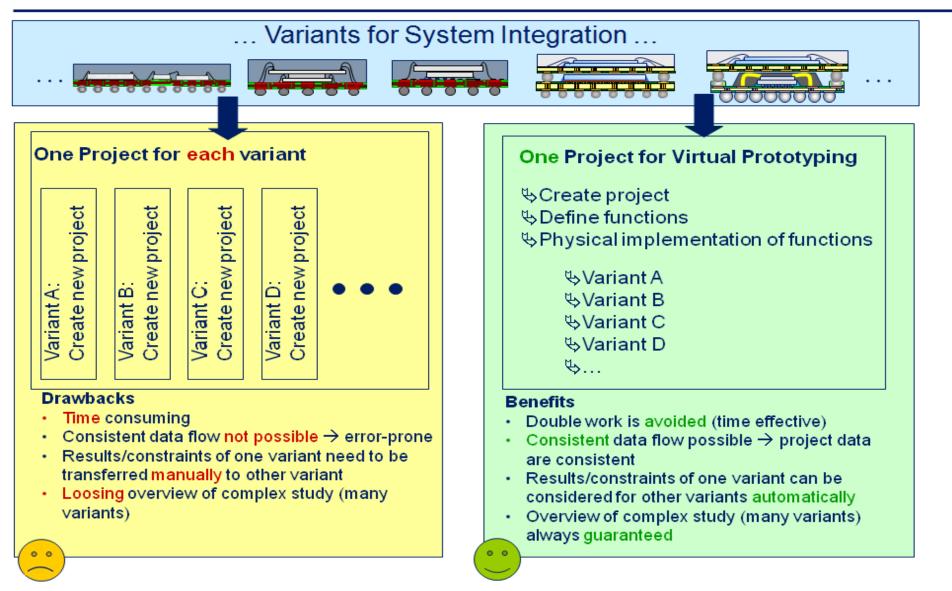

## Use Case Virtual Prototyping

#### Copyright Infineon Technologies AG

02.12.2010

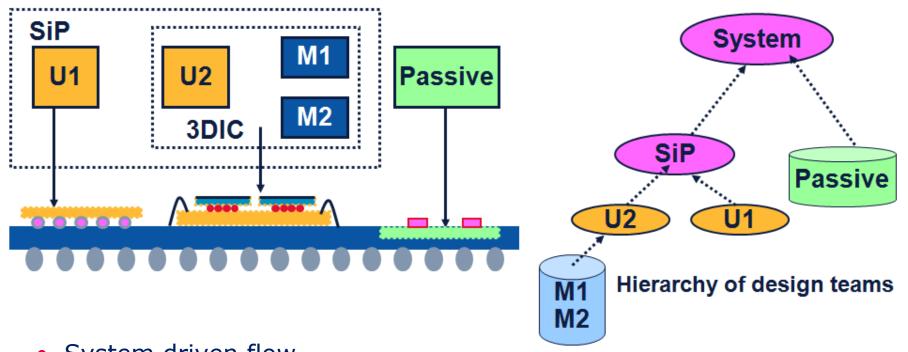

### System-in-Package (SiP) Co-Design

- System driven flow

- Co-Design methodology for integration of the different components

- Trade-off checks and feasibility analysis for the various SiP possibilities

- Building the complete SiP with the interconnects: flip chip, wire bond, substrate, face to face

- Building of complete interconnect model for analysis

#### General concept of Virtual SiP Prototyping

## SiP in Automotive and Industrial

- Infineon has a long track record for SiPs in Automotive and Industrial of more than 10 years with more than 50 different products

- Shipped Volume: several 100 million units

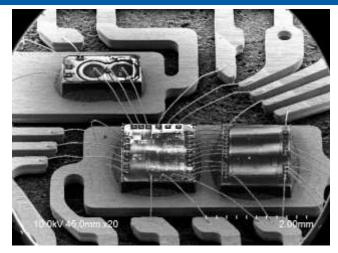

- Assembly technology: chip on chip and side-by-side on leadframe

- Examples in Automotive:

- high current PROFET<sup>®</sup>: (N-channel vertical power FET with charge pump and diagnostic feedback with load current sense).

- Smart Motor Bridges (Bridges, Half Bridges)

- Examples in Industrial:

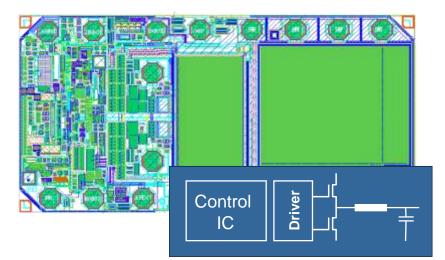

- CoolSET

- Integrated PWM ControlIC + Power MOSFET

- Integrated PFC control-IC+ CoolMOS<sup>™</sup> Power MOSFET

- Fast IGBT DuoPack<sup>™</sup>: Fast IGBT and anti parallel fast recovery diode

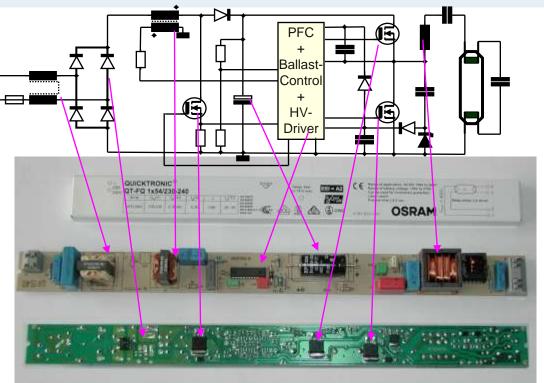

System Integration with multi-chip in a Package enables "intelligent digital control" of Lamps

#### **Digital Smart Lamp Inverter**

- Digital Control methods enable optimized closed loop control vs. analog concepts by changing operation-modes condition-based.

- Digital Power Management comprehensively simplifies optimizations throughout the whole switched mode power supply chain (PFC+PWM+Driver)

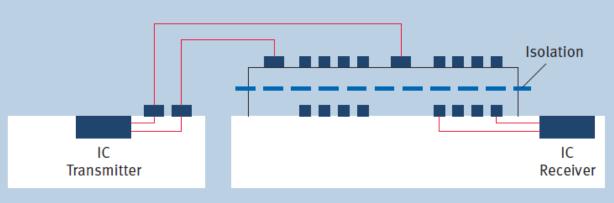

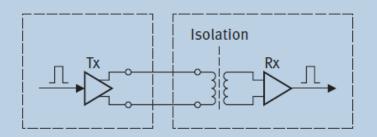

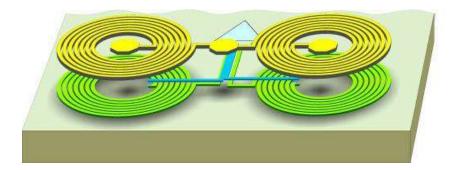

#### ISOFACE<sup>™</sup> PowerSiP

Coreless Transformer Principle

## A lot of advantages compared to optocoupler

- No degradation over time

- Gain reliability

- High temperature range ... 150°C

- Very fast transmission (10 ... 100MHz)

- Low power consumption

- Replaces Opto-coupled solution (9 Opto-couplers)

- 70% PCB area reduction

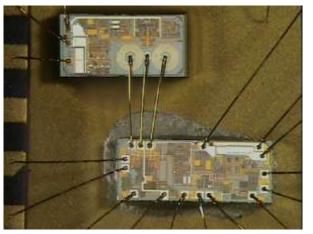

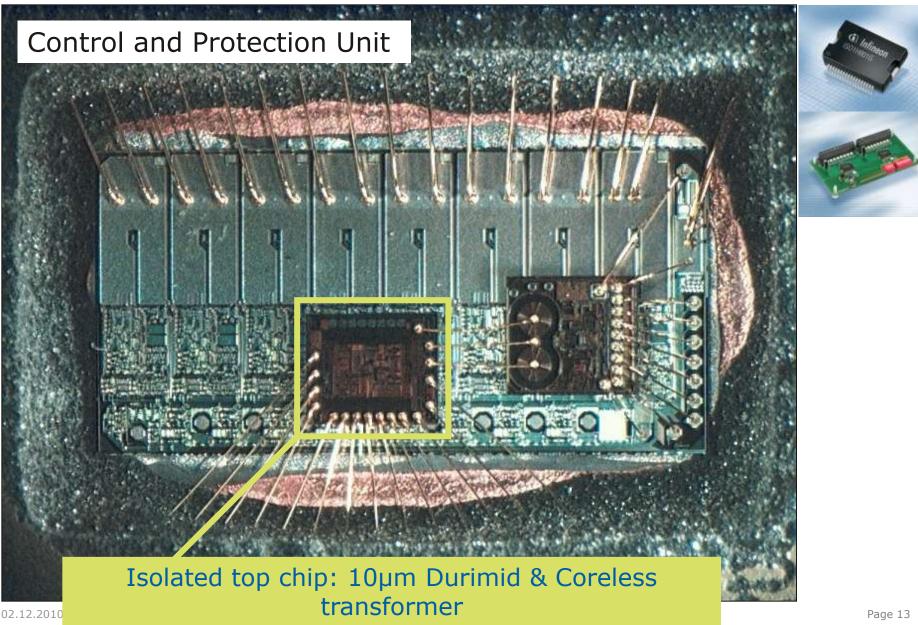

#### ISOface<sup>™</sup> – SiP in Multi-Chip Packaging (Chip-by-Chip-on-Chip)

#### **Our Core Competencies**

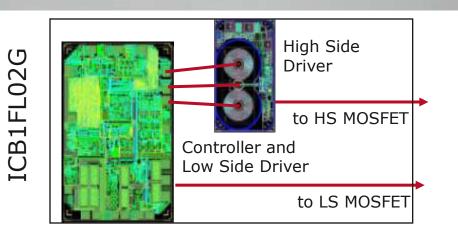

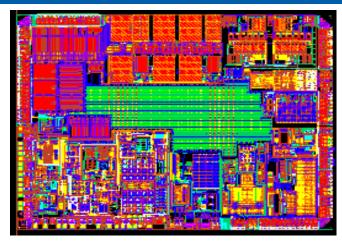

#### High Integration 130nm

#### **High Voltage Isolation on Chip**

#### System in Package

#### **System on Silicon**

#### Factors That Come Into Play

#### Cost Neutral or

- Performance is compelling

- Space saving is required and significant

- Performance Neutral

- No performance penalty unless space saving or cost saving is compelling

#### Dual Source

- Unless cost, performance or space saving is compelling

■ Without differentiation (compelling cost, required space saving or performance) you will find yourself only gaining traction in niche markets → low volume

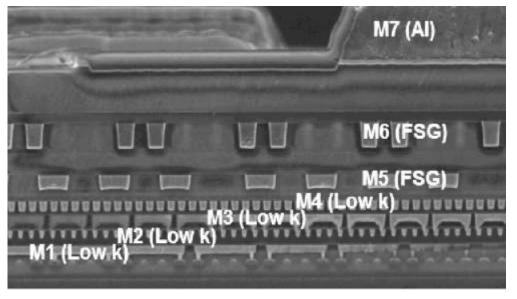

#### **Cost Neutrality** Front-End Technology Comparison

Optimos<sup>™</sup> Power Process

High Density CMOS Process

#### High Density CMOS manufacturing is ~2X higher cost

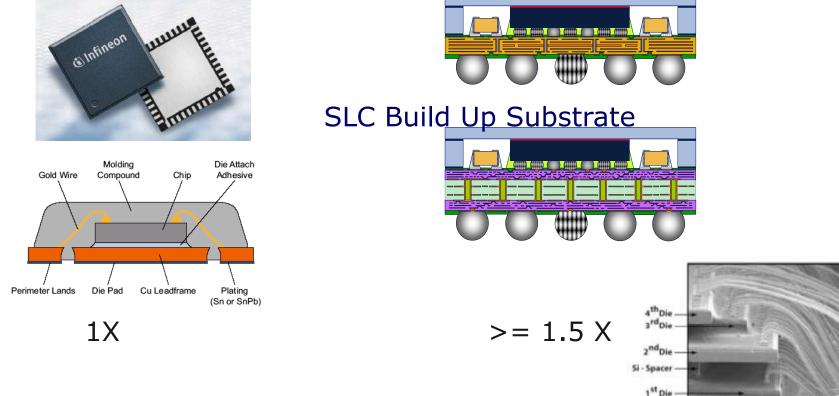

## SiP Build-up Package Vs Standard leadframe

SiP requires more expensive package technology

#### SoC should target standard molded package for best cost

## infineon

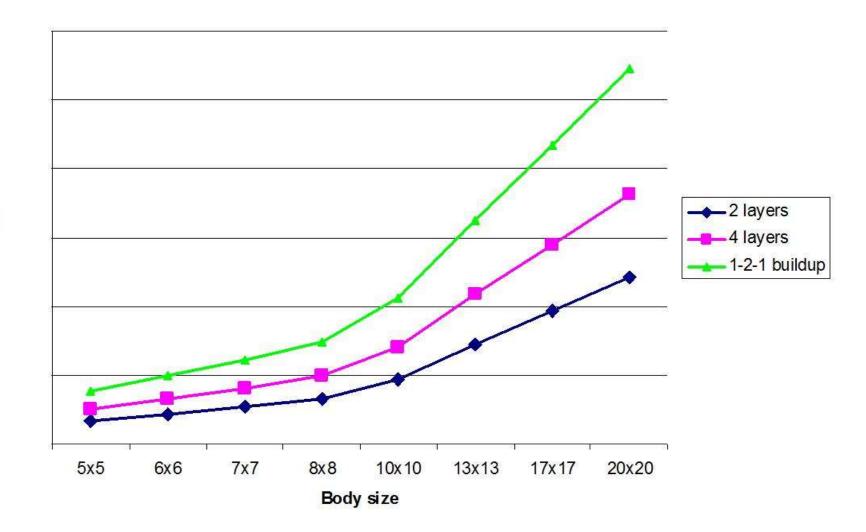

#### Cost Drivers in Package – Body Size

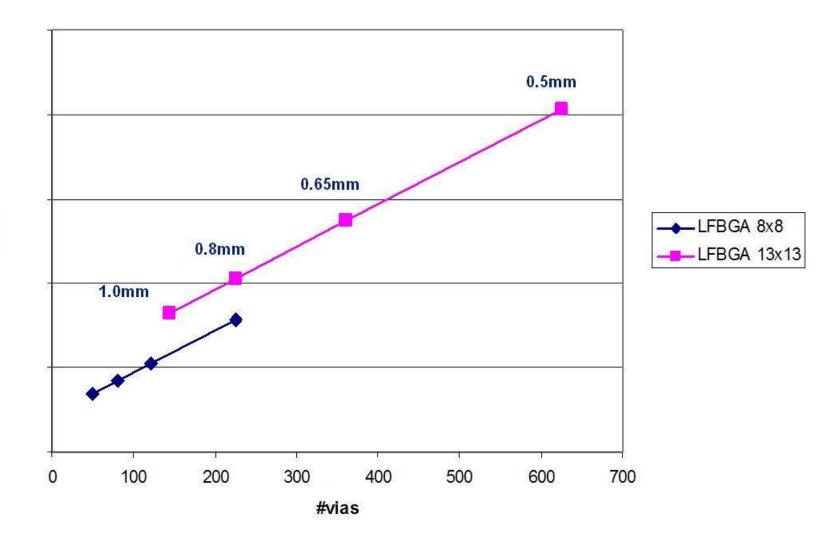

#### Substrate Cost Drivers

price

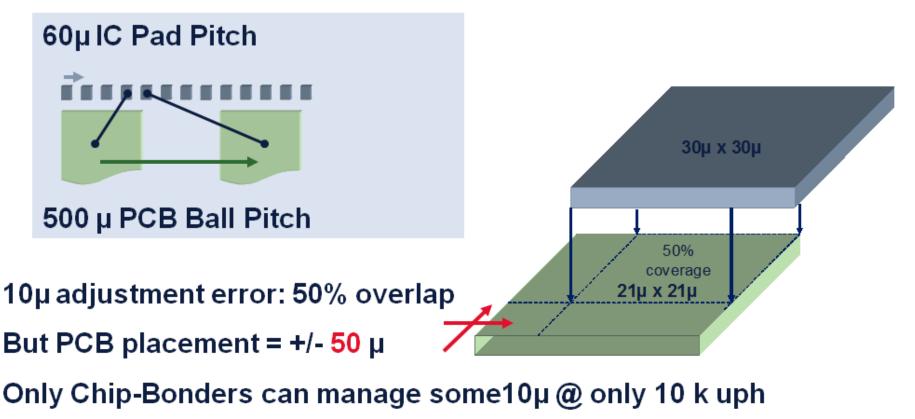

#### PCB Vs Bonder Placement Speed Vs Accuracy

Today we have 0.4 up to 1.0 mm PCB pitches and a component placing accuracy of  $+/-30 \mu$  up to  $+/-70 \mu$  (@100 k uph equipment).

But direct placing of IC's with  $30x30 \ \mu m$  pads ( 60  $\mu m$  pitch) – would need a 10 $\mu$  placing accuracy to get 50% connection area

## Main Power Stage Configurations Today

| DrMOS                    | iPS                                                                              | CanPak          | S308/SS08                | SS08            |

|--------------------------|----------------------------------------------------------------------------------|-----------------|--------------------------|-----------------|

|                          |                                                                                  |                 | URNITAN<br>GAESTE<br>G   |                 |

| CTX01-18738<br>52CQ09 X1 | C48<br>C51<br>C63<br>C63<br>C63<br>C63<br>C63<br>C63<br>C63<br>C63<br>C63<br>C63 |                 | CTX01-18738<br>49CQ09 X1 |                 |

| 20.6mm x 9.0mm           | 21.1mm x 8.9mm                                                                   | 21.5mm x 8.7mm* | 25.2 mm x 7.6 mm*        | 27.6mm x 11.5mm |

| 185.4 mm²                | 187.8 mm²                                                                        | 187.1 mm²       | 191.5 mm²                | 318.4 mm²       |

02.12.2010

Copyright Infineon Technologies AG

#### Cost Neutrality Power Stage Cost Comparisons

#### Discrete Driver, HS + LS

#### SiP: Driver, HS + LS

#### Monolithic -Driver, HS + LS

#### 1X >= 1.2 X >= 2 X

#### Approx equivalent performance

- Significant cost impact to integrate (whether SiP or SoC)

- SiP and Monolithic are attractive for applications where space is a crucial factor.

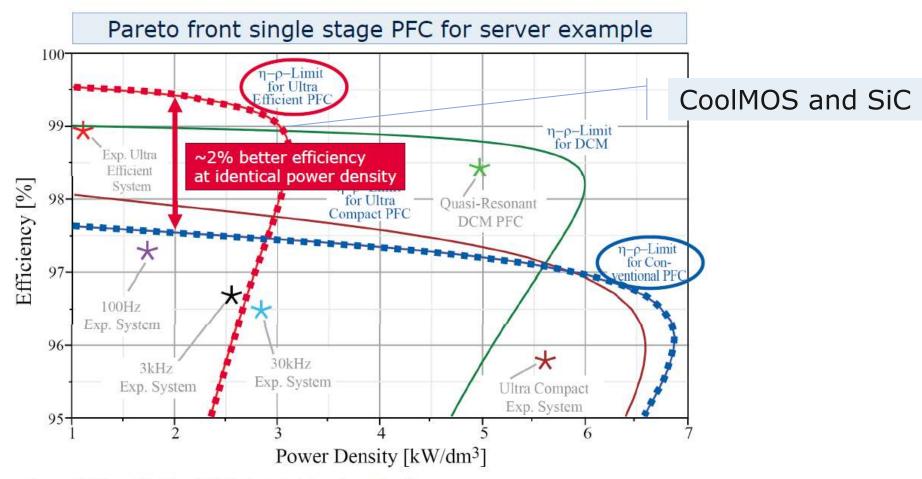

#### **Performance Neutral**

The high bar today for semiconductor conversion is >99% !

■ In Server V<sub>core</sub> DCDC we are above 92%

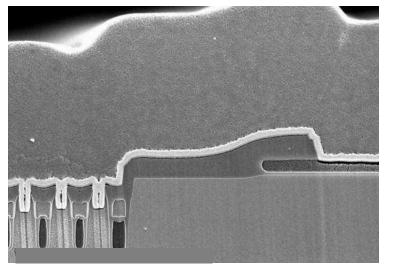

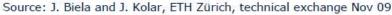

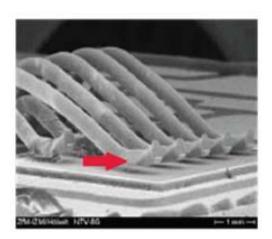

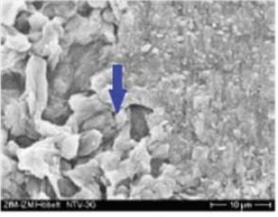

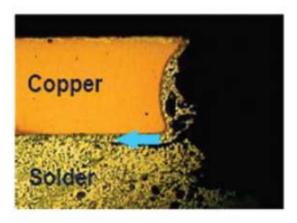

#### Interconnect Technologies Thermo-mechanical wear out becomes critical

wire bond lift-off

degradation of chipmetallization

#### solder joint cracking

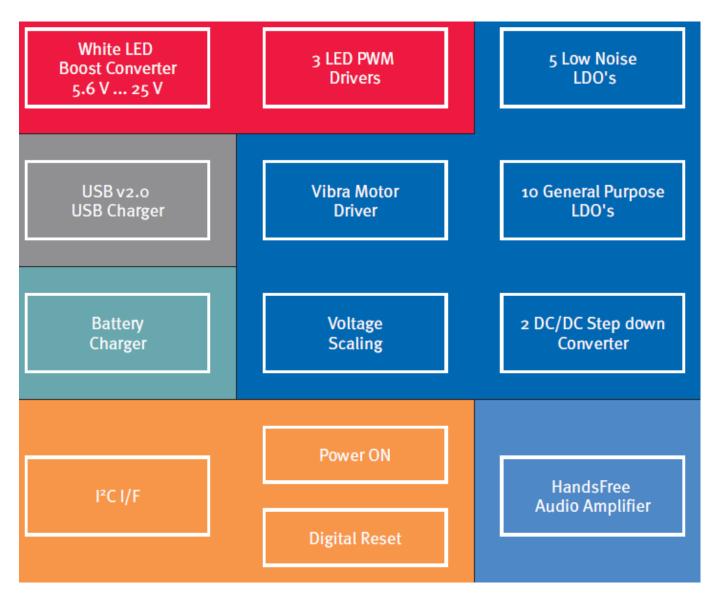

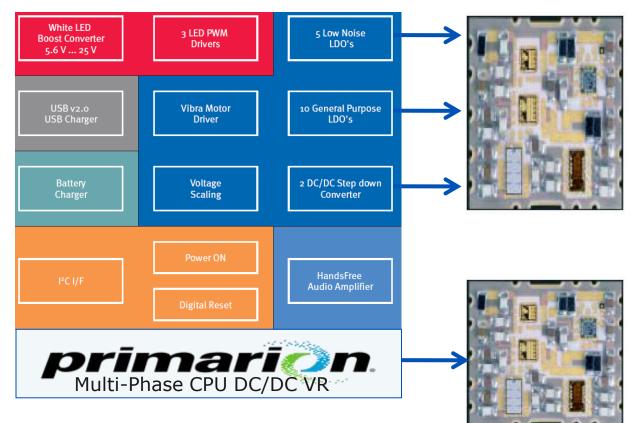

#### Smartphone/Tablet PMU > 17 Controllers integrated

#### iPad is basically a large battery with a small **PCB**

#### There is room for PCB increase – SiP/SoC is a hard **Se**

## Tablet Power System Integration may follow the SmartPhone Model

- Maximum leverage of semiconductor technology to integrate low-current power, digital power and smart-power functions.

- Maximum use of SiP technology to integrate Drivers, Highcurrent MOSFET's and passives.

## Conclusion

SiP is established and will continue to grow into all areas of Power Management and Power Delivery.

SoC will gain Mass-traction once certain Triggers are Met

- Cost Neutral

- Co-Design / Virtual Prototyping for product decision making

- Passives over Active Area minimum die size penalty

- Performance Neutral or Better

- □ Reliability

- Needs more activity and focus

- Decision Matrix

- □ In Research Space please push the technology

- In Commercial Space set a methodology and metrics to evaluate and find the 'should do' answer for your product.

# We commit. We innovate. We partner. We create value.

# ENERGY EFFICIENCY COMMUNICATIONS SECURITY

Innovative semiconductor solutions for energy efficiency, communications and security.