# Mixed Signal Technologies Enabling PSOC and PSIP

Sameer Pendharkar Analog Technology Development Texas Instruments Inc. Dallas, TX, USA

Analog Tech. Development

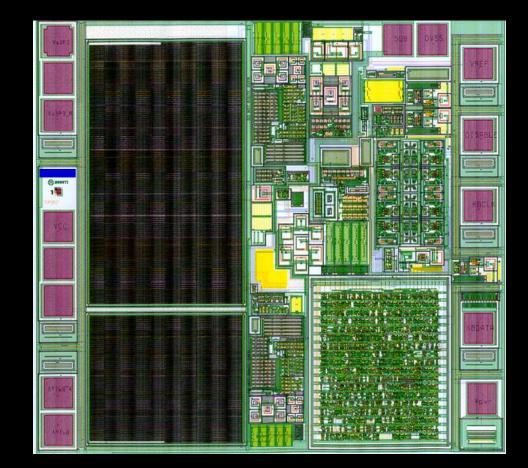

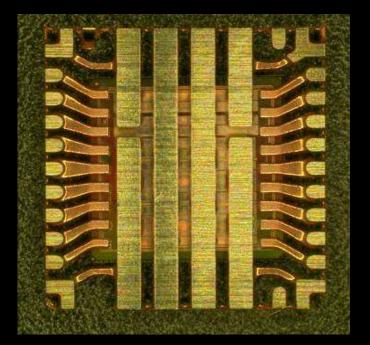

## Typical Power Management IC

- Digital content

- Controllers, Logic

- Analog content

- Feedback, ADC, DAC, Fault detection/prevention, Sensing

- High voltage

- Gate driver, charge pump, regulators

- Power

- Linear regs, SMPS (boost, buck, flyback)

- Passives

- Capacitors, Resistors

**U** Texas Instruments

Analog Tech. Development

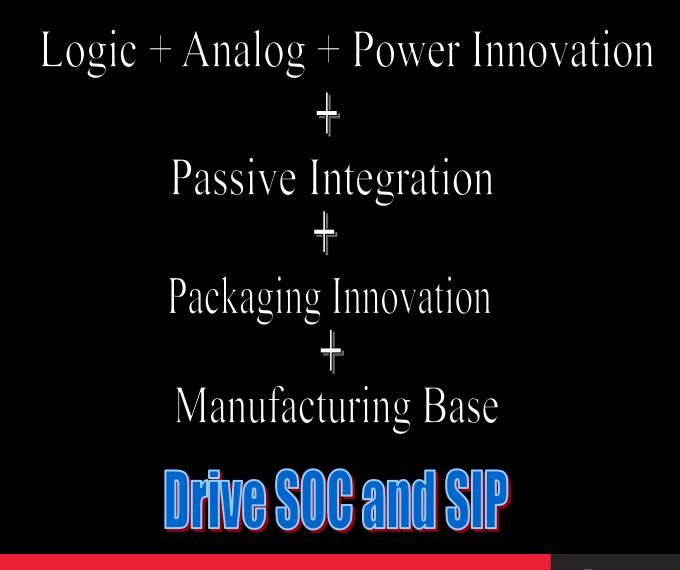

# (Power)SOC & SIP

- Benefits

- Utilization of the best controlled manufacturing process

- Smallest size solution for complete application

- Reduced manufacturing cost

- Increased functionality, fault management and sensing

- Challenges

- Process technology compatibility → integration of digital+analog+high voltage+power+passives

- In-package thermal management

- Circuit isolation and noise management

- Metal interconnect and oxide voltage and reliability

### Mixed Signal Technology Integration

- Digitization of Analog Functions

- enabled by cheap gates

- reduces power consumption

- drives to defect limited yield

- complex closed loop algorithm implementation

- Analog Characterization of "Digital Processes"

- <u>key</u> to enable "system-on-a-chip" (even SIP)

- analog "process control" for roadmap digital technology

- digital transistor "adjustments" to meet analog circuit demands

Analog Tech. Development

### Mixed Signal Technology Integration

#### Total Mixed Signal Integration

- integrate whatever that cannot be integrated on a DSP/MCU chip

- cost focused maximize analog and HV integration

- process complexity to support specialized components

- low/no incremental process cost and complexity exclusively for digital density

- balanced process/component design & circuit design problem

## Mixed Signal Technology Drivers

- Analog CMOS

- low noise and improved matching (Leff <0.15um)</li>

- low Vt and low leakage

- well characterized base analog CMOS building blocks

- Integrated HV and power devices

- single/dual gate technology (Vt management)

- variable voltage capability

- variable voltage high current carrying power device design

## Mixed Signal Technology Drivers

- Integrated passives

- well matched capacitors and resistors (magnetics?)

- no area constraints, design flexibility

- Dielectric/junction isolation

- separate analog and digital blocks for noise control

- band gap, reference and sensing management

- Other components

- higher voltage "analog friendly" cmos

- HV and high performance bipolar devices, efficient diodes

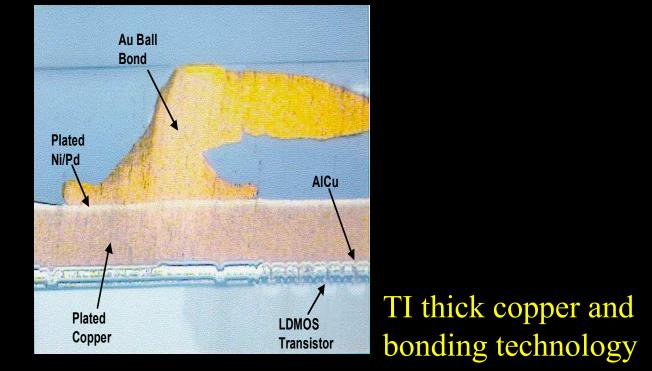

### Mixed Signal Technology Drivers

- High current capable power bussing/interconnect

- bussing interconnect technology to reduce power device area (thick metal driver)

- bond over active area

Analog Tech. Development

Technology for Innovators<sup>™</sup>

Texas Instruments

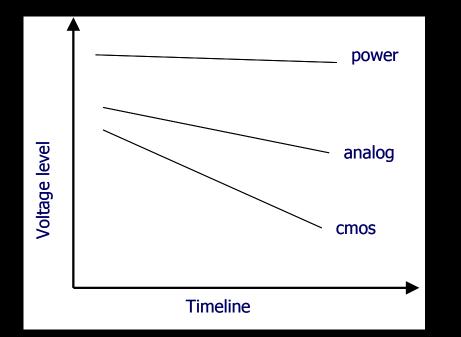

#### Voltage Roadmap vs. Technology Platform

- CMOS & Logic roadmap

- aggressive size reduction

- aggressive voltage reduction (Efield scaling)

- Analog roadmap

- slow size reduction

- moderate voltage reduction

- precision improvement and better passives

#### • Power roadmap

- slow size reduction

- voltage stability or increase

- optimized power performance

<u>Challenge</u>: To develop a single <u>cost-effective</u> integrated technology

Analog Tech. Development

Technology for Innovators<sup>™</sup>

🦆 Texas Instruments

#### **Process Direction**

#### <u>CMOS & Logic</u>

- thin & low-k dielectrics

- thinner & narrower metallization

- multiple CMP metal levels

- expensive deep submicron lithography

- speed & power & density

- shallow trench isolation (STI)

- zero/minimal thermal budget

- complex chain implants and sub-micron profiles

- Ion/Ioff ratio driven

- highly integrated

- <u>Analog & Power</u>

- epitaxy (Si, SiGe)

- thick copper metallization for current

- CMP metal

- SOI, buried layers, deep trench isolation, STI

- standard lithography

- power density & functionality

- precision passives

- deeper junctions

- single/dual gate oxide

- non-volatile solutions

- modular integration

Analog Tech. Development

Technology for Innovators<sup>™</sup>

🥠 Texas Instruments

### **CMOS** Roadmap and Power ICs

#### • <u>Pros</u>

- salicide technology

- trench etch & fill

- CMP and W-plugs

- MeV (high energy) implants

- "resurf-like" wells

- thick oxide field plates

- improved alignment tolerance

- better matching & parametric control

#### <u>Cons</u>

- thinner & low-k

dielectrics

- thinner metal system

- very high doped wells

- significantly reduced thermal cycle

- thinner gate oxides

- higher energy implants

- increased process cost

#### Key Component Requirements

- Analog CMOS

- compatible with high performance logic, modular features and low cost

- "very good" analog DC characteristics

- Vt. Gds. Gm. Delta-Vt, Ioff, Vdd

- additional features

- high voltage

- low Vt, low leakage

- excellent matching and 1/f noise and low dynamic Vt shift

- isolate substrate and switching interference noises

Analog Tech. Development

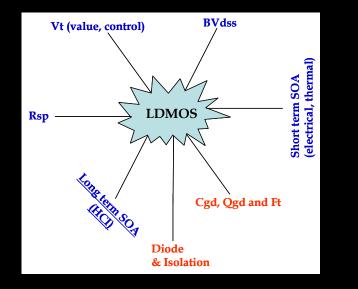

### Key Component Requirements

- High voltage & power

- voltage scalability & isolation

- modular and minimal process cost

- current scalability

- compatibility with high performance logic

#### → <u>Drives</u>

- MOS based solution

- ease of integration & high i/p impedance

- mostly uniform current flow & faster switching

- Lateral solution

- easier to integrate

- easier voltage scalability

- normally lower Rdson X Qgate compared to vertical (lower Rdson)

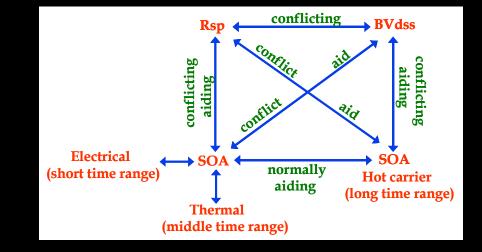

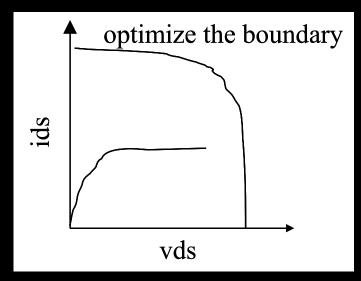

# Optimizing Power Devices

- Key HV device parameters

- breakdown voltage ( $\infty$ )

- on-state resistance (0)

- device robustness (intrinsic  $\infty$ )

- switching speed (intrinsic  $\infty$ )

- reliability (>> 10 years)

**TEXAS INSTRUMENTS**

Analog Tech. Development

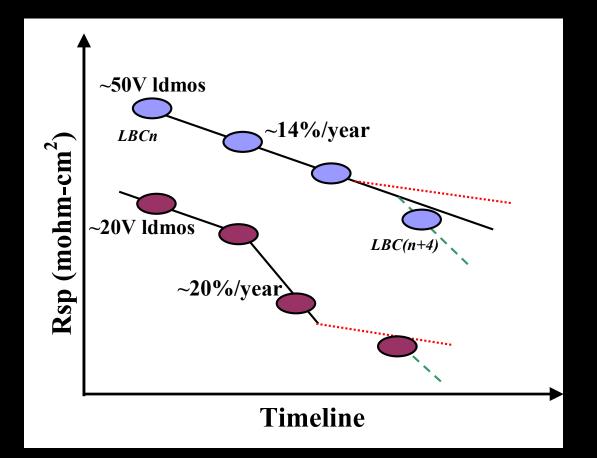

#### Integrated FET Scaling – Drives Technology

Integrated FET improvement at TI

about 25-30% node-on-node improvement

Analog Tech. Development

Technology for Innovators<sup>™</sup>

**TEXAS INSTRUMENTS**

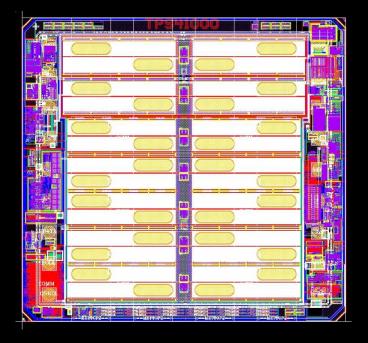

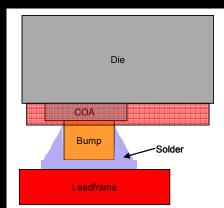

#### Packaging Innovation –SOC/SIP power density

- Up to 20A monolithic dc-dc converter

- enhanced thermal performance

- no wires, low parasitics and high reliability

**U** Texas Instruments

Analog Tech. Development

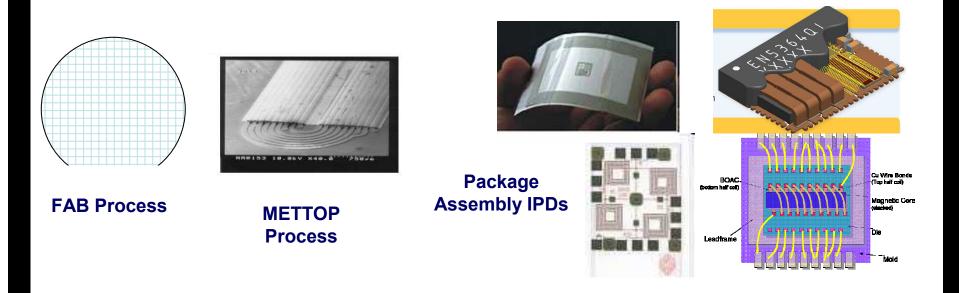

#### **Passive integration**

- Drives improved isolated and non-isolated power supplies (transformers and inductors)

- Drives high density capacitors decoupling, precision

- Enables full power supply in package

Analog Tech. Development

Technology for Innovators<sup>™</sup>

🥠 Texas Instruments

#### Summary

Analog Tech. Development