# Integration of passives components and reliability improvement by design

#### Matthieu Nongaillard

Laboratoire AMPERE, 21 avenue Jean Capelle, 69621 Villeurbanne cedex, France NXP Semiconductors, 2 rue de la Girafe BP5120, 14079 Caen France

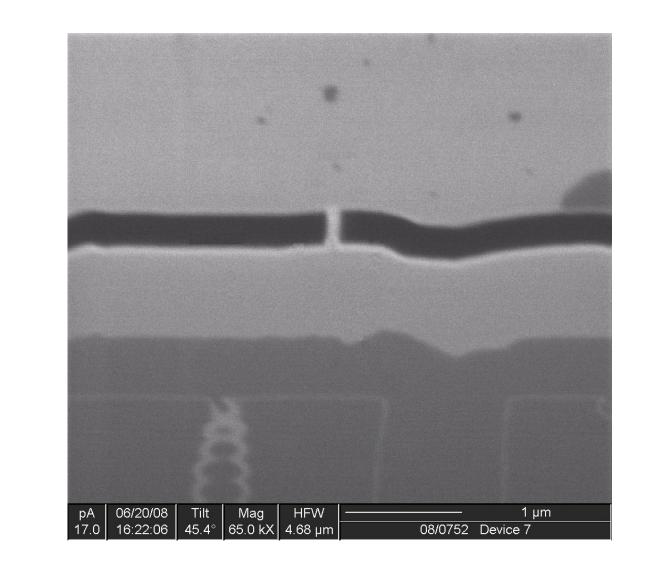

# Problems of integrated passives devices

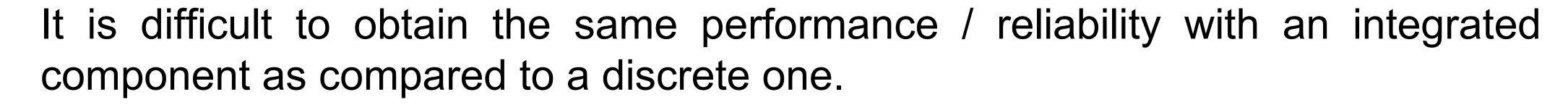

System-in-package (SIP) technology that is widely used in the industry makes it possible to stack many dice in the same package. This allows one to use the most appropriate integrated circuit (IC) fabrication technology for each die.

Ampere

#### Reliability: Passive Thermal Cycling Test

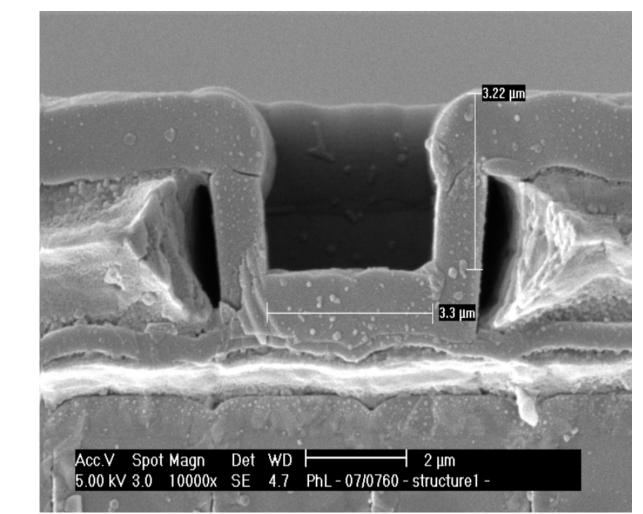

Thermo-mechanical stress can damage dice and create cracks and short-circuits due to differences in the CTE (Coefficient Thermal Expansion) of different layers.

The number of cycles and temperatures are not identical for all products.

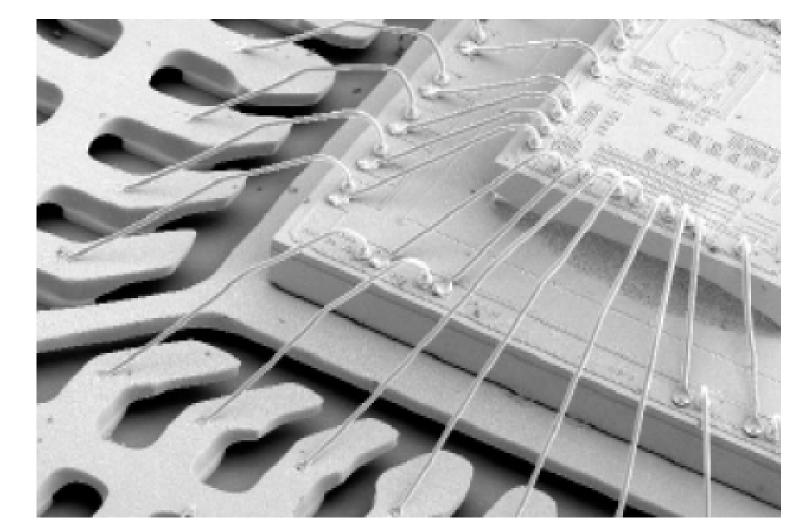

# Principle of stress relief pattern

Additional structures which are intentionally fragile (stress relief patterns) help to reduce thermo-mechanical stress. Destruction of these structures does not affect functionality of the circuits.

Evaluations of the test chips: Test chips are based on a known weak reference design. Improvements will be estimated based on the difference in the number of defects observed between different versions of the test chip and the reference design.

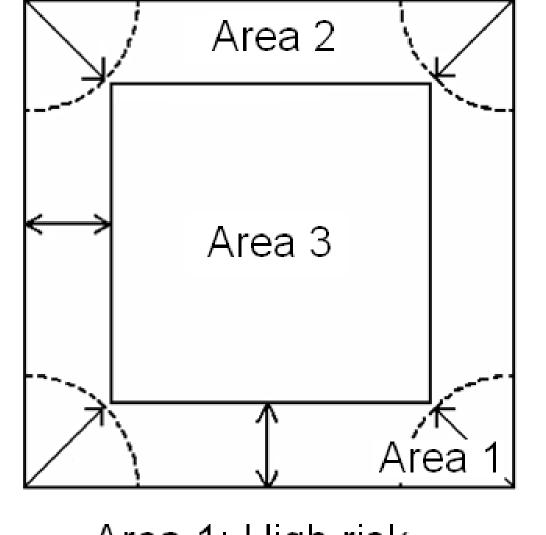

Area 1: High risk Area 2: Medium risk Area 3: Low risk

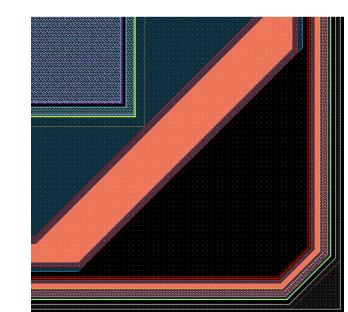

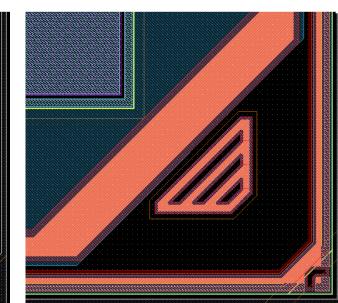

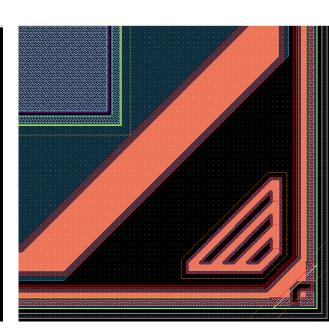

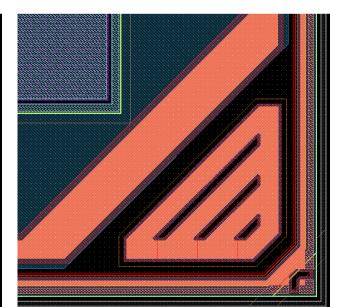

### Corner stress relief (CSR)

Die corners are free of functional structures and stress relief structures placed in each corner can complete the seal ring.

Main geometrical parameters have been evaluated experimentally.

#### **Slots**

Principle is the same as CSR: slots are inserted on the upper metallic layer with the goal of reducing thermo-mechanical stress

There are some restrictions for using slots: they can be used on area 2 only.

Distribution of slots on a die is studied with regard to its ability to reduce stress.

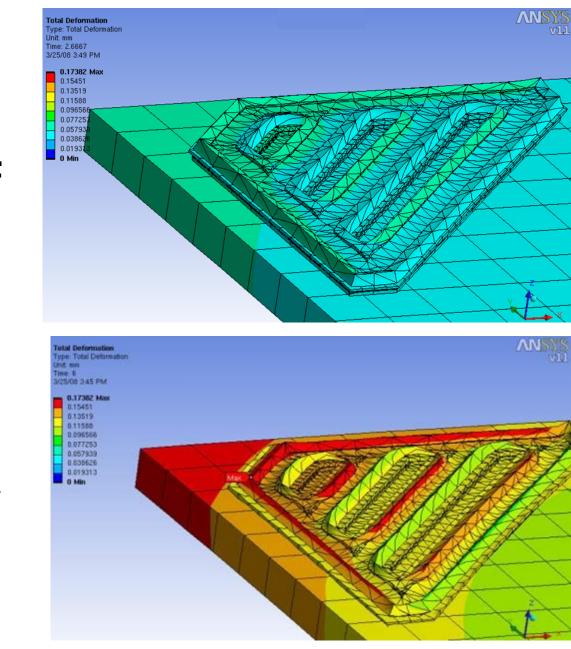

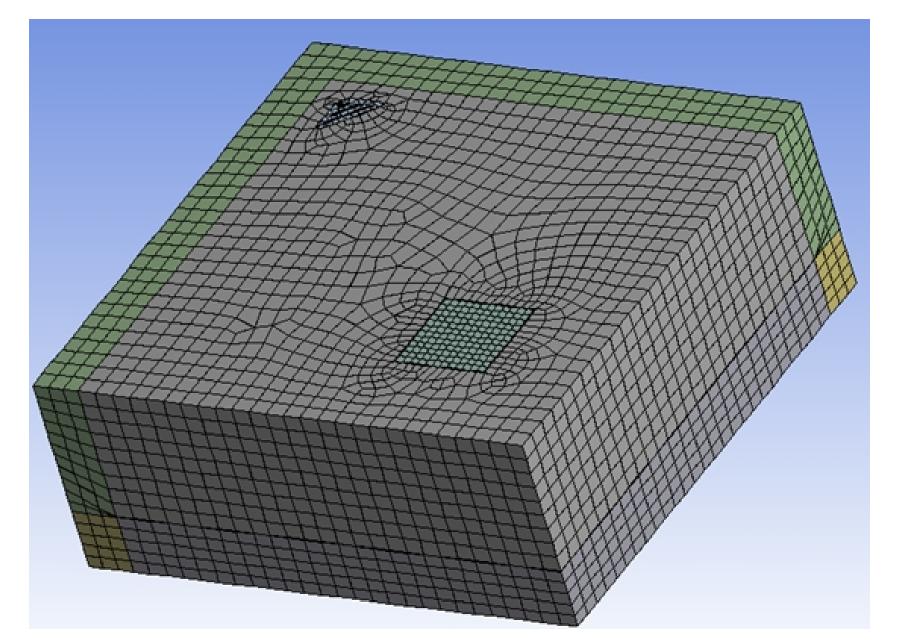

## **Simulation**

Simulation makes it possible to increase the number of solution evaluated: the experimental approach is too expensive, limiting the number of solutions that can be tested on silicon.

Current simulation results will be confirmed by experimental results