# Integrated inductive DC/DC down conversion for integrated power management using a two-die approach

Henk Jan Bergveld, Kasia Nowak, Ravi Karadi September 24, 2008

# Outline

- Introduction

- Why integrated power management?

- Two-die approach for integration

- First demonstrator

- Design aspects

- System-in-Package (SiP) construction

- Measurement results

- Second demonstrator

- Improvements with respect to first demonstrator

- Design aspects

- Measurement results for active die

- Conclusions and future outlook

#### Introduction

# Why integrated power management?

- Energy-source voltage ≠ load voltage

- Drive for <u>efficient voltage conversion</u>

- ...for increased run time in mobile devices

- ... for reduced petrol consumption in automotive

- Switched-mode conversion: Ls and/or Cs

- Drive for smaller size/integration of power supplies

- Package integration; low L,C, high  $f_s$

- Enables integration of power supply with load: system integration

- <u>System integration</u> would allow increased power efficiency

- Integrated power management: <u>small form-factor highly efficient</u> <u>DC/DC converters</u>

# Integrated DC/DC conversion

- Integrated capacitive converters

- Advantage

- · Avoid integration of inductor

- Disadvantages

- Limited control of output voltage

- Multi-ratio converters require many capacitors

- Integrated inductive converters

- Advantages

- Limited number of passives

- Good control of output voltage

- Disadvantage

- Integration of inductor difficult

- Approach:

- Integrated inductive down conversion using planar air-core inductor

- 100-mW output power range

# **Two-die approach for integration**

- Rationale:

- Actives integrated in nm-CMOS with the load

- Passives in low-mask-count optimized passive-integration process (PICS)

- Pros

- High-density capacitors, low area for  $C_{in}$  and  $C_{out}$  (10-100 nF)

- Low height (<600  $\mu m)$

- Cons

- Need copper for reasonable Q factor inductor

- Planar technology, relatively large foot print coil (e.g. 10 nH costs 1 mm<sup>2</sup>)

#### **Results for the first demonstrator** (\*)

(\*) H.J. Bergveld, R. Karadi, K. Nowak, 'An inductive down converter System-in-Package for integrated power management in battery-powered applications', IEEE Power Electronics Specialist Conference, PESC08, pp. 3335-3341, Rhodes, Greece, June 16-18, 2008

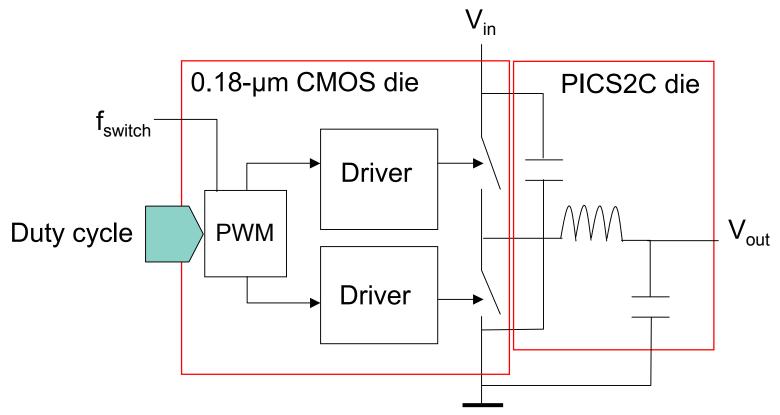

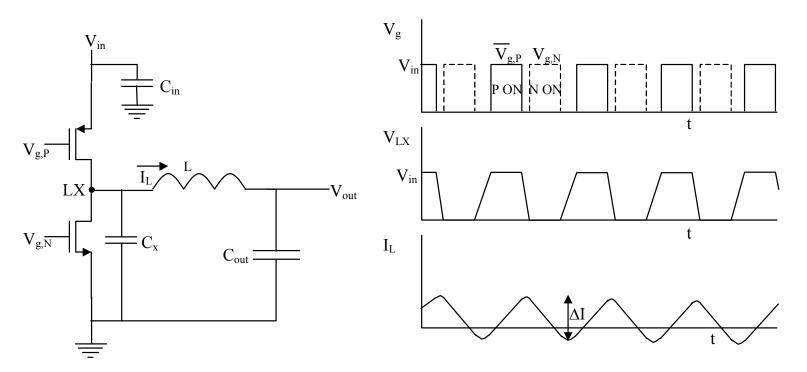

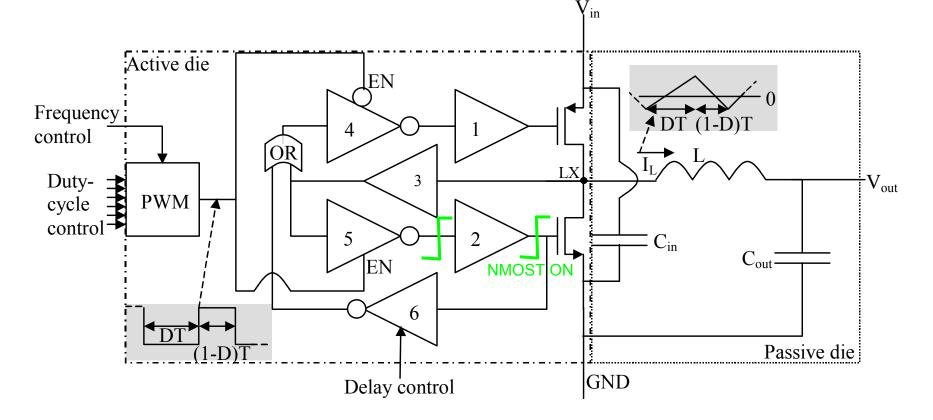

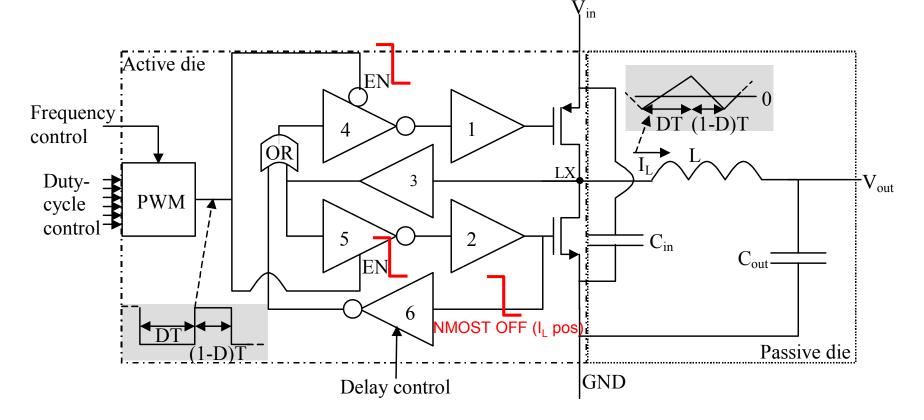

System block diagram of synchronous DC/DC down converter

No closed-loop control! Focus on power stage and two-die approach

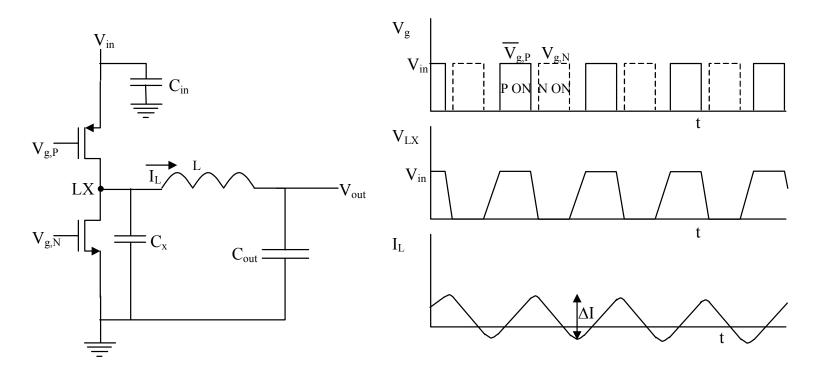

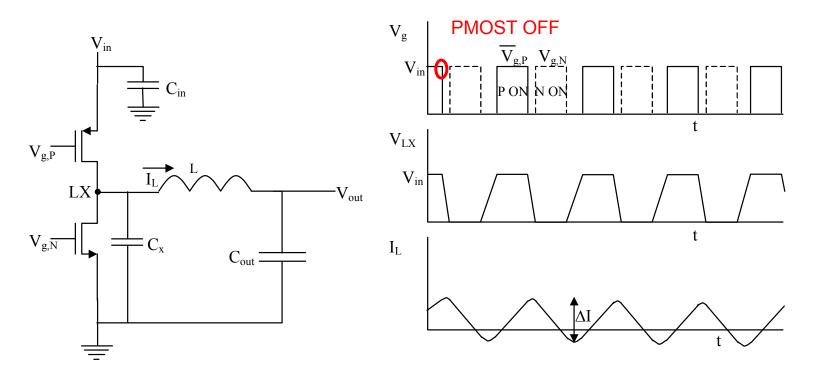

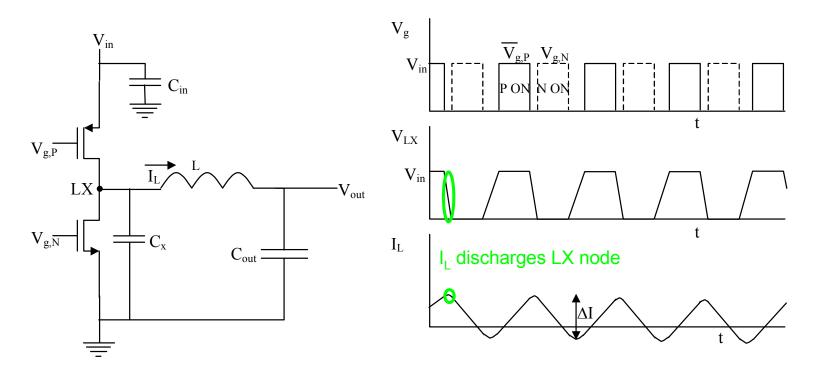

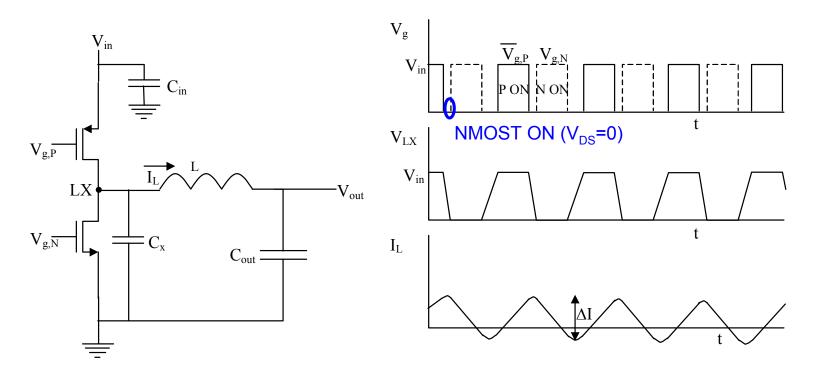

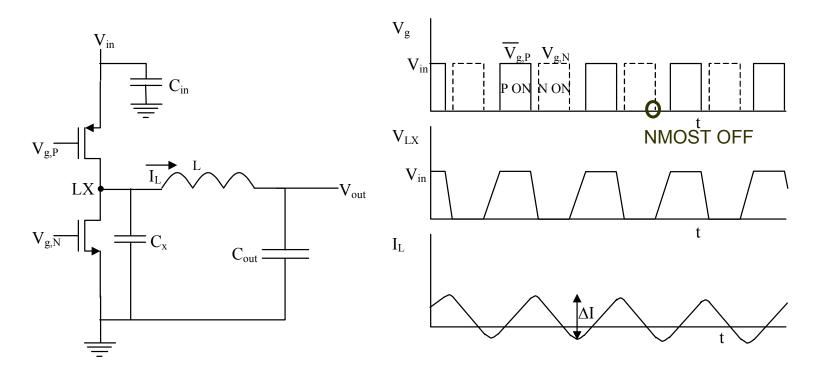

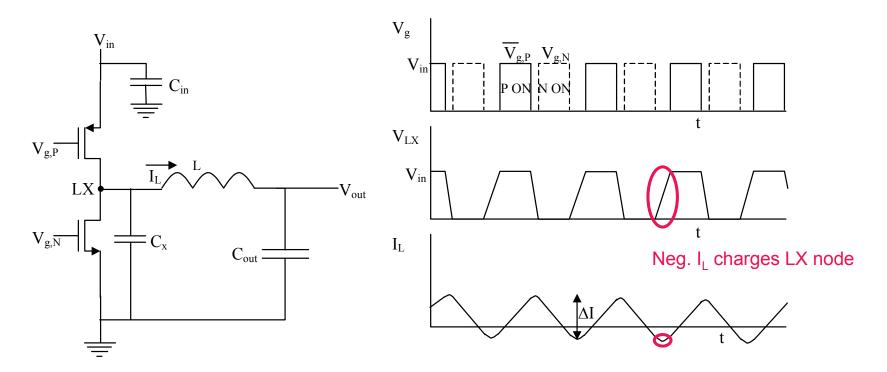

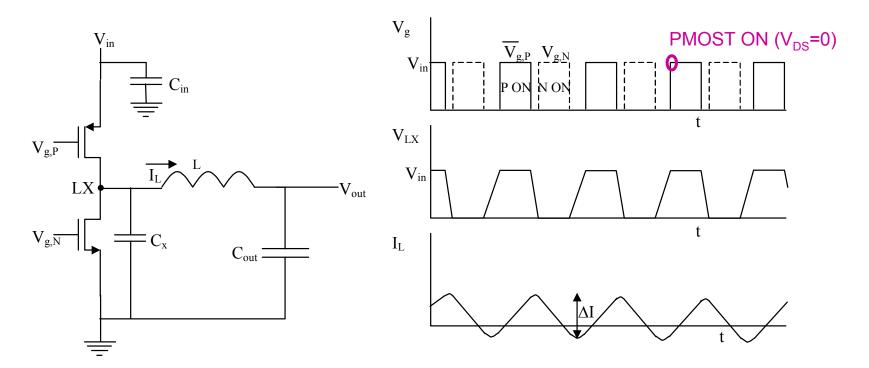

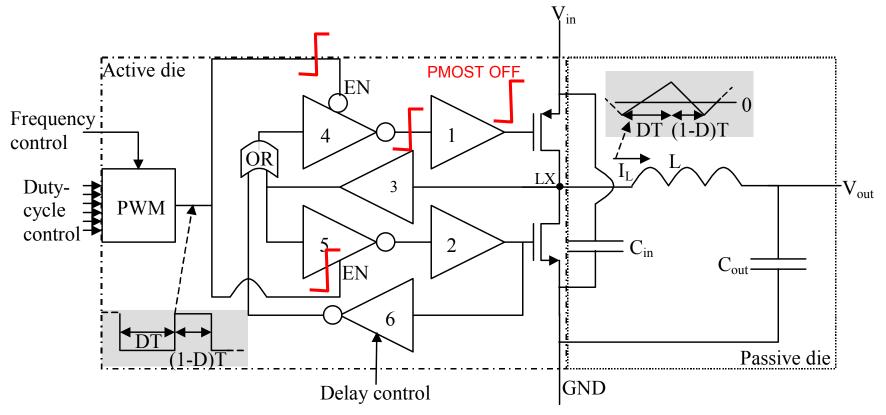

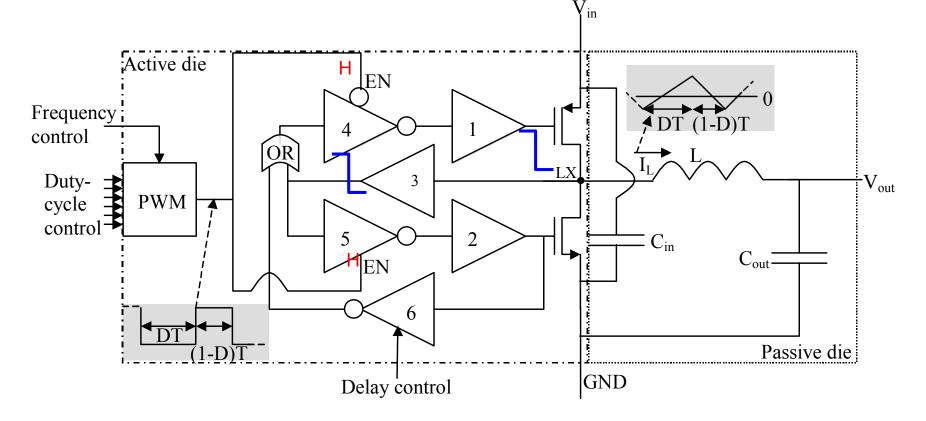

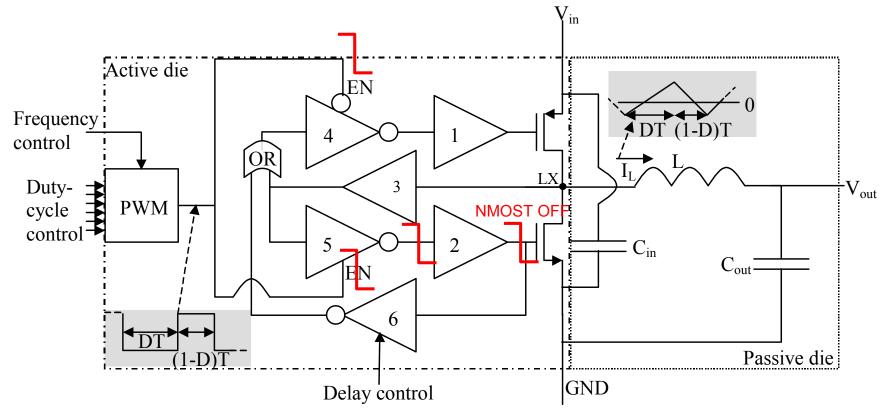

Zero-Voltage-Switching (ZVS) concept (Continuous Conduction Mode)

Zero-Voltage-Switching (ZVS) concept (Continuous Conduction Mode)

Zero-Voltage-Switching (ZVS) concept (Continuous Conduction Mode)

Zero-Voltage-Switching (ZVS) concept (Continuous Conduction Mode)

Zero-Voltage-Switching (ZVS) concept (Continuous Conduction Mode)

Zero-Voltage-Switching (ZVS) concept (Continuous Conduction Mode)

Zero-Voltage-Switching (ZVS) concept (Continuous Conduction Mode)

Zero-Voltage-Switching (ZVS) concept (Continuous Conduction Mode)

- Need adaptive dead-time control

- $V_{in}$ =1.8 V,  $P_{out}$ =100 mW  $\rightarrow$  Simple ZVS

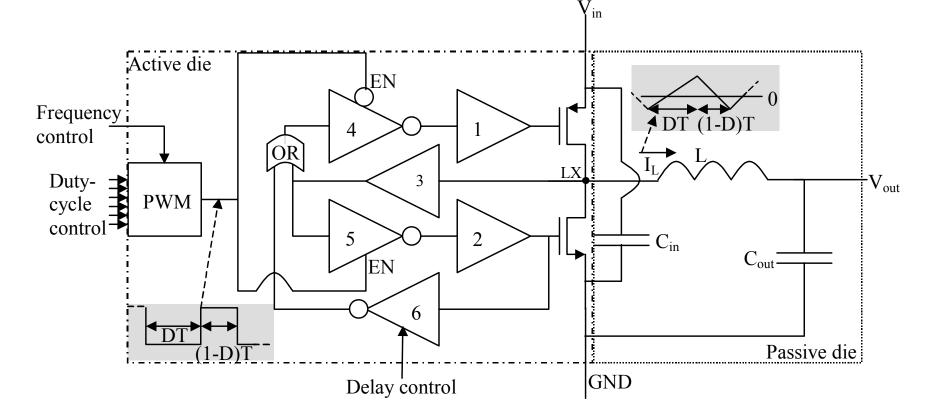

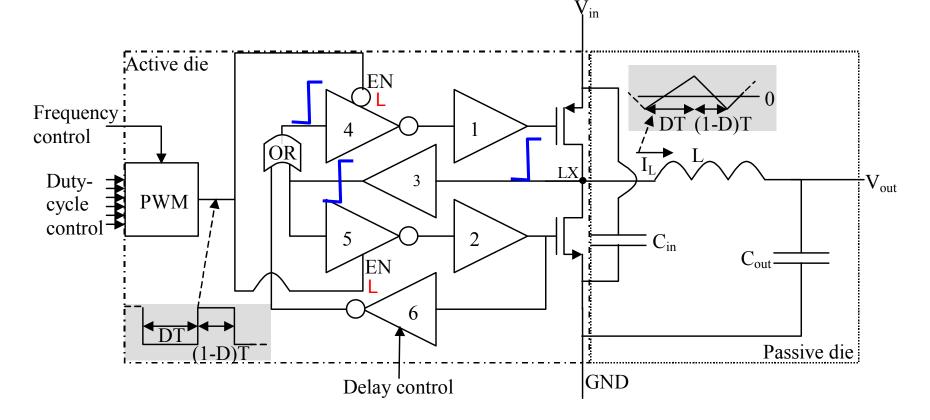

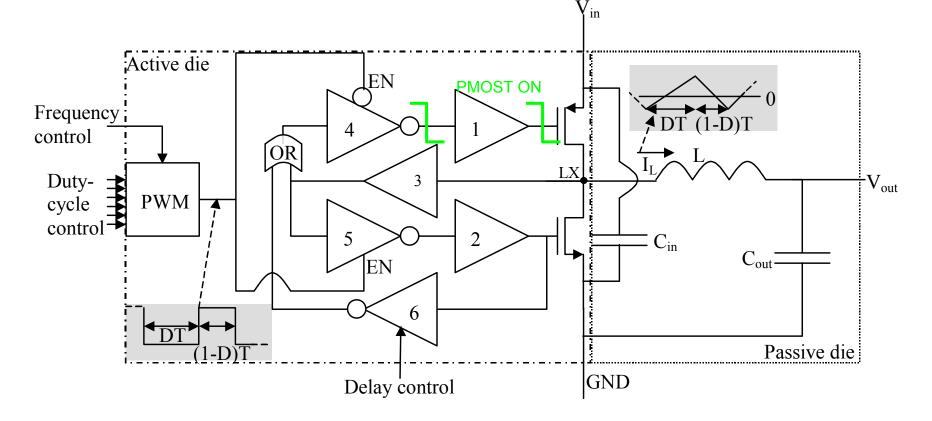

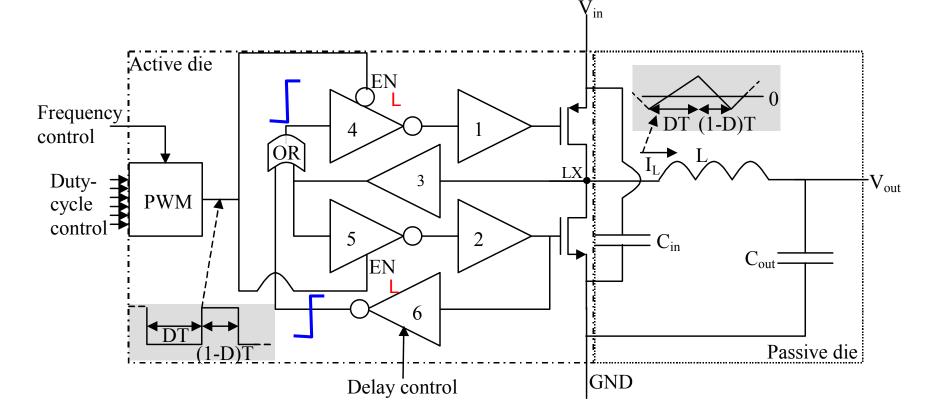

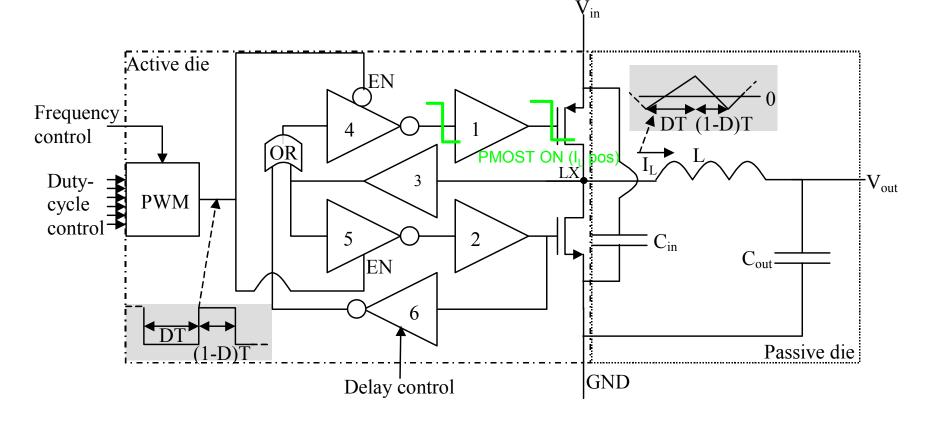

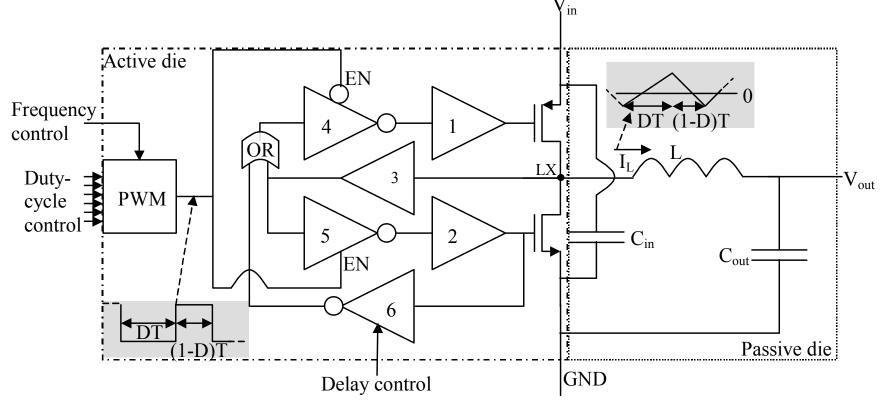

System block diagram incl. ZVS implementation

System block diagram incl. ZVS implementation

System block diagram incl. ZVS implementation

System block diagram incl. ZVS implementation

System block diagram incl. ZVS implementation

System block diagram incl. ZVS implementation

System block diagram incl. ZVS implementation

System block diagram incl. ZVS implementation

System block diagram incl. ZVS implementation

System block diagram incl. ZVS implementation

System block diagram incl. ZVS implementation

- Switches optimized for f=50 MHz, I=100 mA, L=20 nH

- Driver tapering factor and number of stages optimized

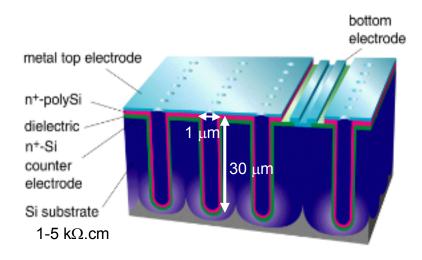

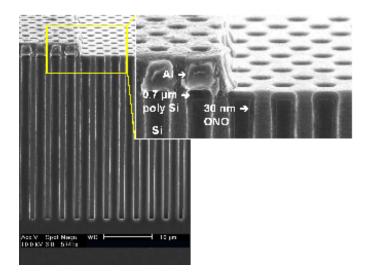

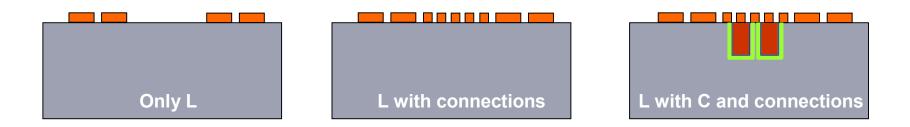

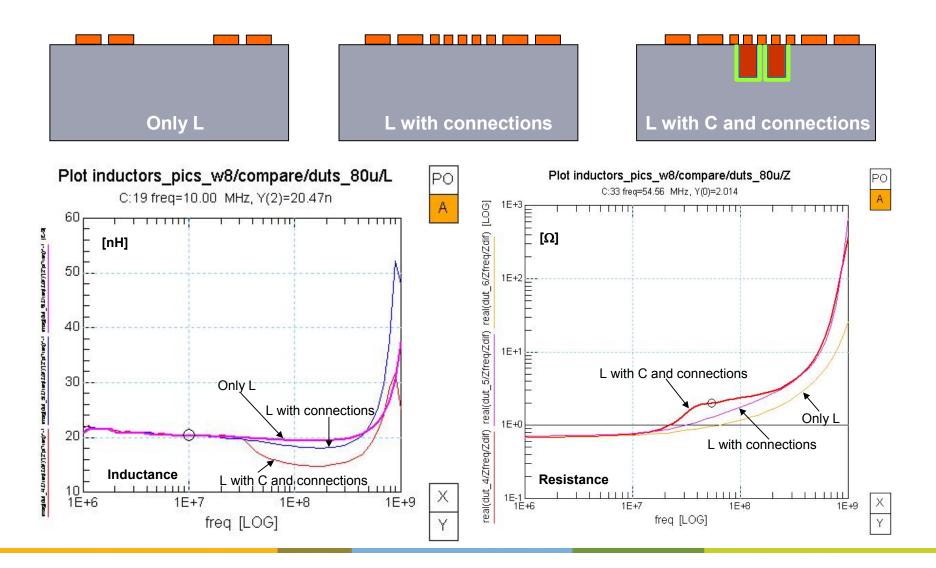

- Passive process: <u>Passive-Integration</u> <u>Connective</u> <u>Substrate</u>

- Silicon-based platform for integrating R, L, C

- High capacity density: 80 nF/mm<sup>2</sup> in used version,  $V_{BV}$ =15.5 V

- Two metal layers

- First-level aluminium

- Second-level 8-μm copper: inductor

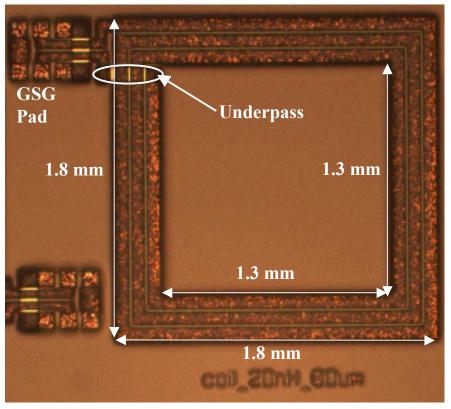

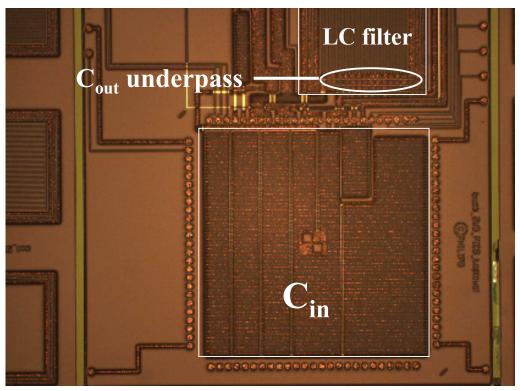

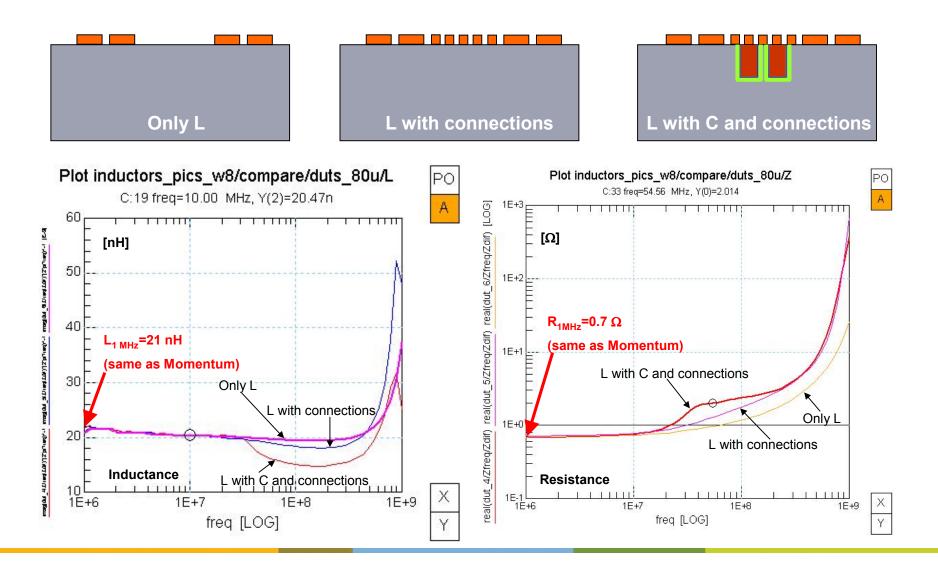

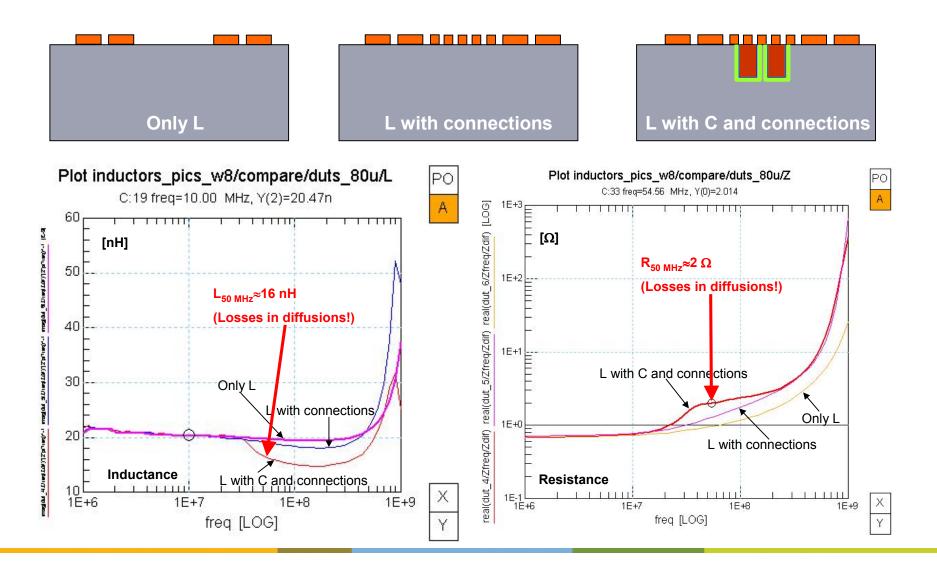

#### Inductor design

- Fit  $C_{out}$ =75 nF (15 mV<sub>pp</sub> ripple) inside

- L=20 nH: N=3, w=80 µm, s=8 µm

- Underpass: balance R and  $f_{res}$  (1 GHz)

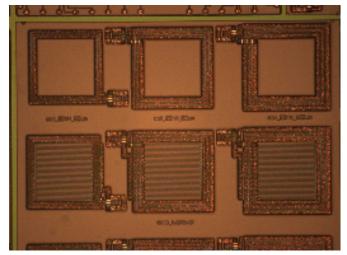

- Various test structures for probing

#### Total die design

- $C_{out}$  connections

- Thin parallel stripes: low losses

- Copper routing (low ESR)

- $\bullet$  GND underpass: balance ESR and  $\mathrm{f}_{\mathrm{res}}$

- Thick supply lines (250 µm)

- C<sub>in</sub>=300 nF

- Complete area active die (3.8x3.8 mm<sup>2</sup>)

- Total passive-die area: 6.6x6 mm<sup>2</sup>

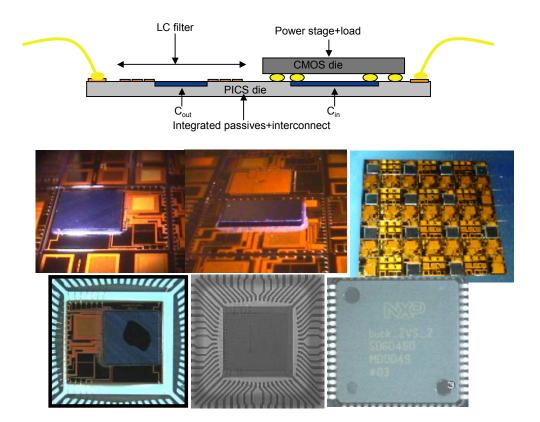

# **SiP construction**

- Flip-chip: Thermo compression gold stud bumps

- Sandwich wire-bonded in QFP64 package

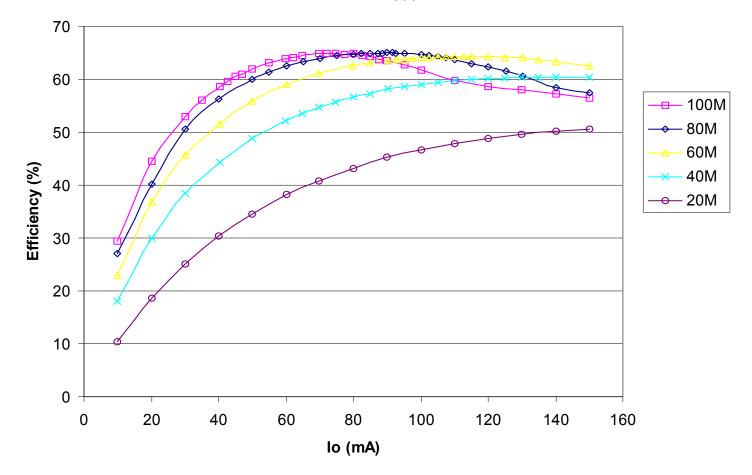

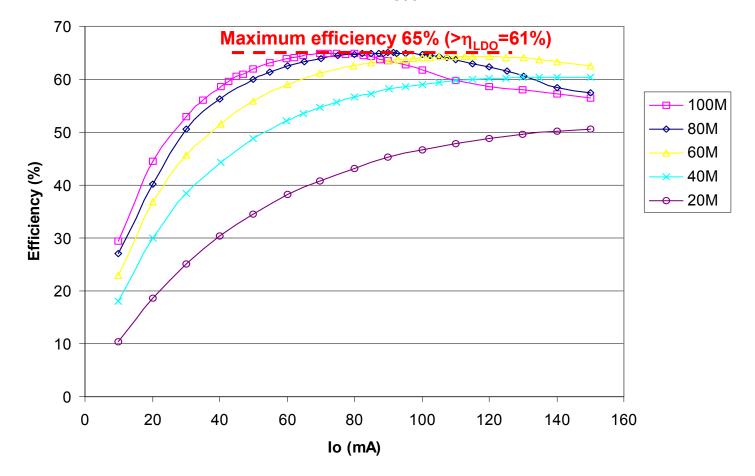

#### Measurement results: complete converter

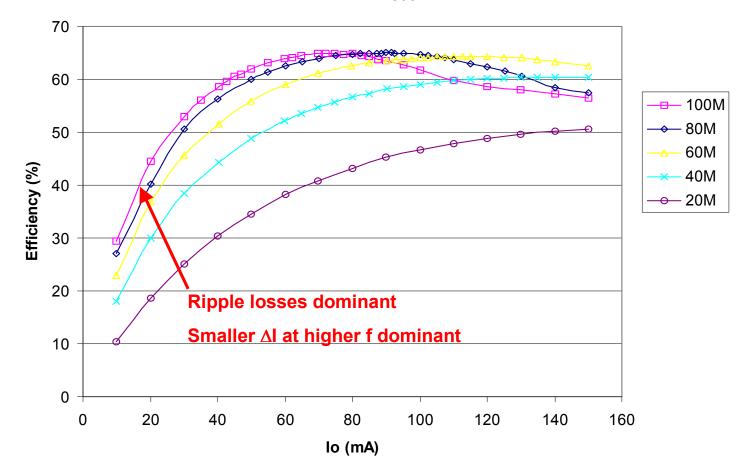

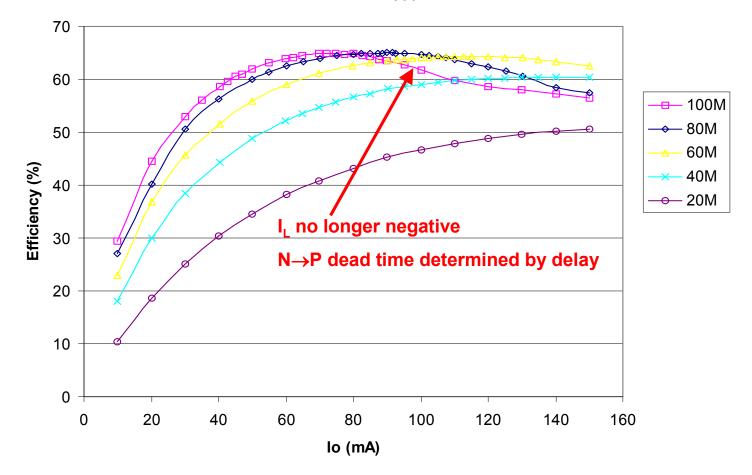

Measured efficiency for  $V_{in}$ =1.8 V,  $V_{out}$ =1.1 V, minimum delay

Measured efficiency for  $V_{in}$ =1.8 V,  $V_{out}$ =1.1 V, minimum delay

CONFIDENTIAL 16 Integrated DC/DC conversion based on two-die approach, Power SoC 2008, Cork, Ireland, H.J. Bergveld, September 24, 2008

Measured efficiency for  $V_{in}$ =1.8 V,  $V_{out}$ =1.1 V, minimum delay

CONFIDENTIAL 16 Integrated DC/DC conversion based on two-die approach, Power SoC 2008, Cork, Ireland, H.J. Bergveld, September 24, 2008

Measured efficiency for  $V_{in}$ =1.8 V,  $V_{out}$ =1.1 V, minimum delay

CONFIDENTIAL 16 Integrated DC/DC conversion based on two-die approach, Power SoC 2008, Cork, Ireland, H.J. Bergveld, September 24, 2008

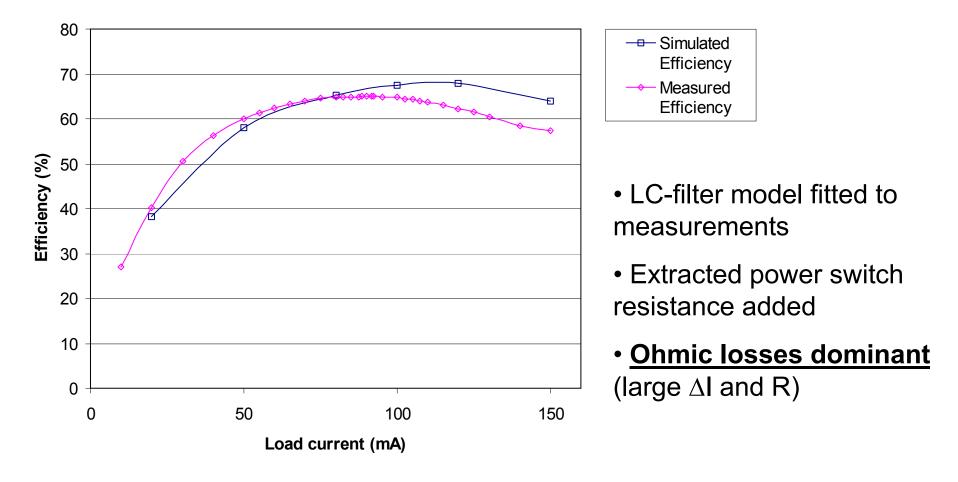

Measured vs simulated efficiency at f=80 MHz

CONFIDENTIAL 17 Integrated DC/DC conversion based on two-die approach, Power SoC 2008, Cork, Ireland, H.J. Bergveld, September 24, 2008

LX node voltage (f=50 MHz, I=15 mA)

- Supply decoupling effective (ringing caused by probe)

- ZVS functional, no body diode losses

### **Results for the second demonstrator**

## Improvements with respect to first demo

### Decrease ohmic series resistance

- Move C<sub>out</sub> out of middle L

- No eddy-current losses

- L area minimized

- Decrease switch connection resistance

- Fewer bond pads in parallel

- Optimized switch placement

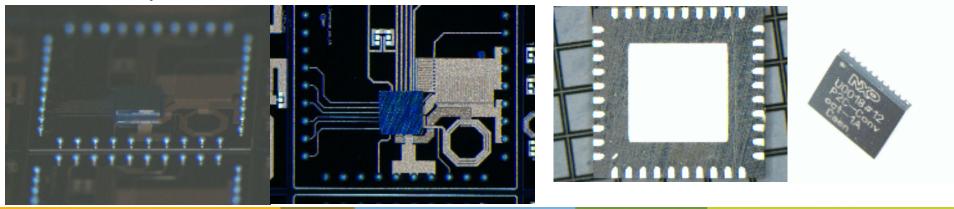

- No bond wires: double flip-chip

- Solder bumps (no gold stud bumps)

### Smaller active die

- One DC/DC converter, less I/O pads

- More routing space on passive die

### Smaller package

- HVQFN40

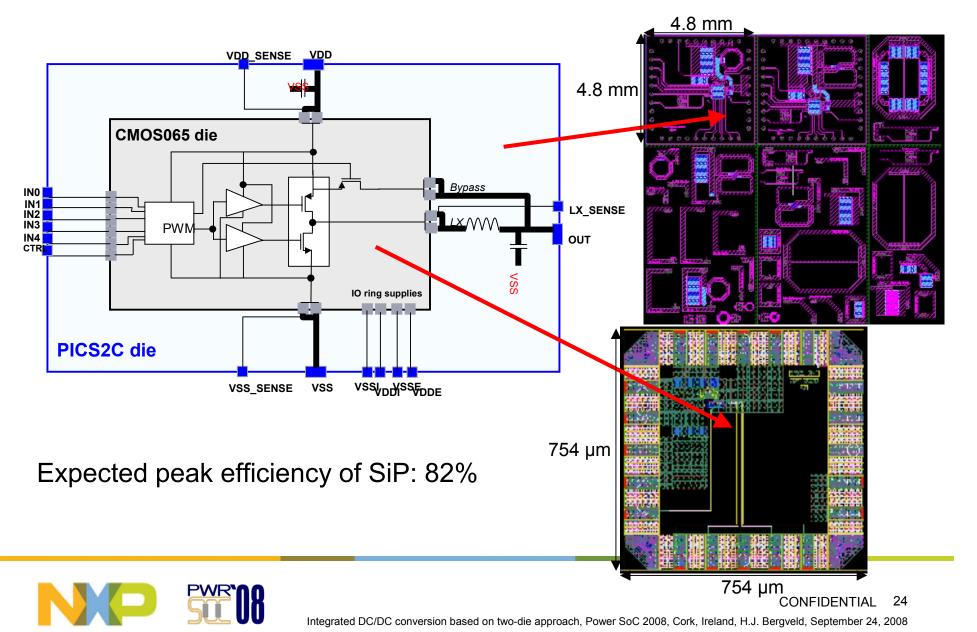

### Move to newer CMOS technology node

- 65-nm CMOS (load integration)

- V<sub>in</sub>=1.2 V (65-nm CMOS limit)

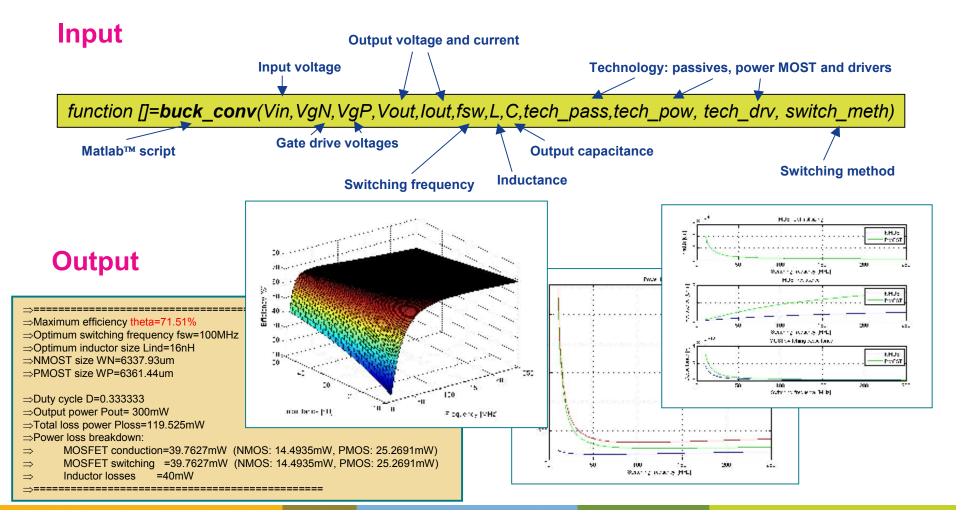

# **Optimize design for efficiency (Matlab**<sup>TM</sup>**)**

High-level modeling, design-space exploration

#### CONFIDENTIAL 21

Integrated DC/DC conversion based on two-die approach, Power SoC 2008, Cork, Ireland, H.J. Bergveld, September 24, 2008

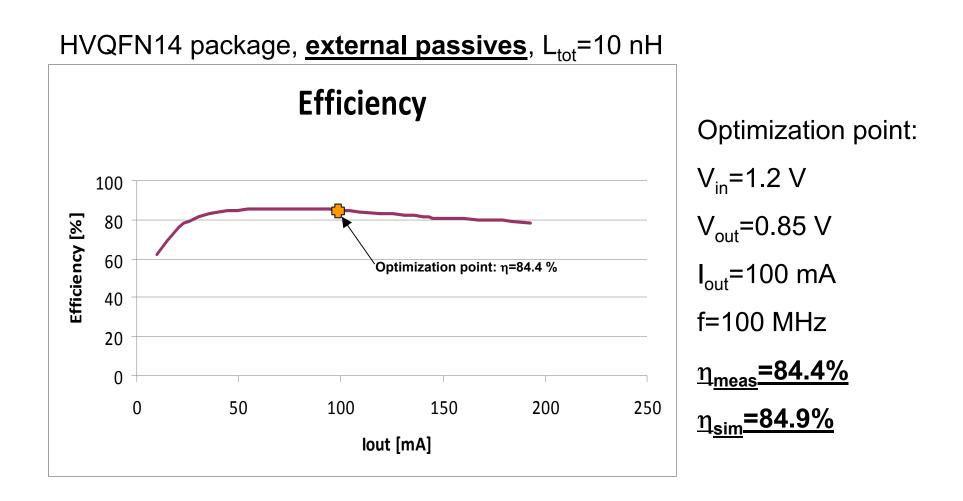

# **Design aspects**

- No ZVS implementation

- At V<sub>in</sub>=1.2 V ZVS implementation costs more efficiency than it saves

- Design optimization active die

- $V_{out}$ =0.85 V ( $\eta_{LDO}$ =71%)

- $I_{out}$ =100 mA

- f=100 MHz

- Simulated efficiency: 84.9 %

- No closed-loop control

- Design optimization passive die

- − L=10 nH (N=3, w=50 µm, s=8 µm, area≈1 mm<sup>2</sup>,  $R_{DC}$ ≈0.4 Ω,  $R_{100 \text{ MHz}}$ ≈ 0.5Ω)

- C<sub>out</sub>=30 nF (12.5 mV<sub>pp</sub> ripple)

- $C_{in}=21 \text{ nF}$  (underneath active die and slightly beside it)

## Measurement result active die (stand-alone)

# SiP construction (September 2008)

# SiP construction (September 2008)

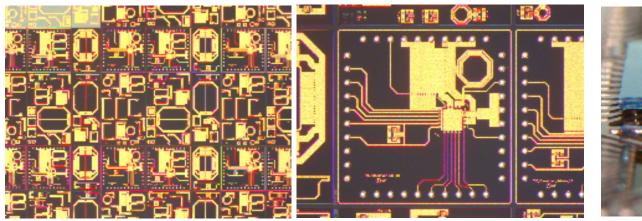

### Assembly pictures

### Passive wafer

**Double flip-chip**

Active-on-passive-die sandwich

HVQFN40

CONFIDENTIAL 25 Integrated DC/DC conversion based on two-die approach, Power SoC 2008, Cork, Ireland, H.J. Bergveld, September 24, 2008

### **Conclusions and future outlook**

# Conclusions

- Two-die approach feasible for integrated DC/DC conversion

- No external components, higher efficiency than linear regulators

- Integration with load enables system integration of power management

- Future Outlook

- Direct Li-ion battery connection

- Cascoding at high frequencies with low-power ZVS implementation

- Even higher capacitive densities

- Even beyond 400 nF/mm<sup>2</sup>, ref. Fred Roozeboom et al

## Acknowledgements

- NXP Eindhoven, Netherlands

- Stefan Menten, Ralf Pijper, Luuk Tiemeijer

- NXP Caen, France

- Jorge Ferreira, Lionel Guiraud, Sebastien Iochem, Sophie Ledain, Dick Mapanao, Eric Pieraerts, Mickael Pommier

- Philips Research, Eindhoven

- Derk Reefman

- INSA Lyon, France

- Bruno Allard, Malal Bathily, Nicolas Degrenne, Jerome Saby