# From Dual Die PwrSoC To Monolithic PwrSoC

**September 24, 2008**

## **Overview**

- Markets & Applications

- Strategy: From Dual Die to Single Die (Monolithic) For PwrSoC

- Milestones of Dual Die PwrSoC

- Inductor Design Issues

- Progression Towards Monolithic

# **Market Forces Affecting Power Designs**

Industry wide system demands are challenging power designs to deliver Higher Efficiency, Smaller Size and Lower Noise

#### **Energy Utilization**

- Reduction of OpEx

- Extension of battery life

- Improved thermals in constrained designs

#### New Services and Applications

- Driving additional functions -Adding more power rails

- In a constrained or shrinking board size

#### Broadband Technology

- Wireless and networking data rates increasing

- Reduction of jitter, ripple, EMI critical to achieve higher speeds

# **Innovating Power Designs**

Engineered from the start to enable the industry's first power system-on-chip solution

- High frequency design in proprietary CMOS

- Proprietary integrated inductor technology

- Package architecture enabling leading edge performance

- System level RF & EMI design for high performance

| LDO Replacement:              | Address space constraint challenges while<br>tripling power efficiency in ultra low noise<br>environments |

|-------------------------------|-----------------------------------------------------------------------------------------------------------|

| Noisy DC-DC Replacement:      | Replace offending noisy DC-DC with an ultra quiet, high-efficiency DC-DC converter                        |

| Alleviating the Space Crunch: | Miniaturize traditional discrete DC-DC                                                                    |

|                               |                                                                                                           |

# **PwrSoC's Deliver Value**

#### <u>Highest Power Density from</u> <u>Milli-Amps to Tens of Amps</u>

- Tiny Package/Low Profile

- Low Part Count and Small Solution Footprint

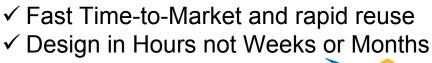

### Ultra-Low Ripple & Noise

- Up to 95% less Ripple

- Low Conducted and Radiated Noise

- High Performance

- Excellent Transient Response

- Load Matched to Technology

- Very High Efficiency: up to 95%

### Ease-of-use

- Simple Design

- Fully-tested Gerber files provided

✓ Reduces board area

✓ Enabling smaller designs with more features

✓ Superior RF performance✓ Higher data rate capability

Agenda

- ✓ Excellent match to <90nm technology

- ✓ Enables superior battery savings

# Markets Served by PwrSoC's

| Markets         | Applications                               | Value to Customer                      |

|-----------------|--------------------------------------------|----------------------------------------|

| Personal Mobile | PC Cellular Data Cards                     | <ul> <li>Smallest Footprint</li> </ul> |

|                 | <ul> <li>Navigation (GPS)</li> </ul>       | Low noise                              |

|                 | <ul> <li>Media Players</li> </ul>          | <ul> <li>Energy Efficiency</li> </ul>  |

|                 |                                            |                                        |

| Home            | <ul> <li>Audio Amplifiers</li> </ul>       | Low noise                              |

| Entertainment   | • DVR                                      | <ul> <li>Energy Efficiency</li> </ul>  |

|                 | <ul> <li>Blu-ray Disc Players</li> </ul>   | <ul> <li>Ease of use</li> </ul>        |

|                 | <ul> <li>Digital TV</li> </ul>             |                                        |

| Enterprise      | Servers                                    | <ul> <li>Smallest Footprint</li> </ul> |

|                 | <ul> <li>Storage Controllers</li> </ul>    | <ul> <li>Energy Efficiency</li> </ul>  |

|                 | <ul> <li>Solid State Drives</li> </ul>     |                                        |

|                 | <ul> <li>Office Automation</li> </ul>      |                                        |

| Telecom Access  | • DSL/GPON                                 | Smallest Footprint                     |

|                 | <ul> <li>Cellular Base Stations</li> </ul> | <ul> <li>Energy Efficiency</li> </ul>  |

|                 |                                            | Solution cost                          |

## **Strategy For Commercial Realization of PwrSoC** (Dual Die Transition to Single Die)

- Establish market viability and reliability track record for PwrSoC today

- Define technical operating conditions required to achieve single die solution

- Take advantage of current advanced assembly and components consistent with these technical operating conditions

- Use existing inductor technology to initially achieve the competitive cost thresholds

- Continue to work the manufacturability and cost of the single die solutions

- Focus on applications for which the monolithic approach can provide a compelling technical advantage

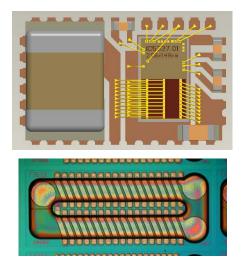

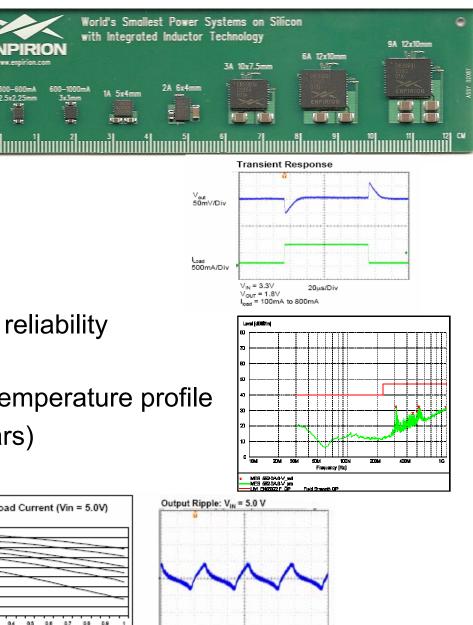

## Dual Die PwrSoC Approach (Milestones)

- Output Current Range

- 0 3A thru 9A

- Manufacturability

- Yield

- Quality & Reliability

- System level performance with IC reliability

- JEDEC, JESD

- MSL 3 260°C peak solder reflow temperature profile

- FIT rate = 6.1 (MTBF ≈ 18700 years)

- Technical Performance

- Transient response

- Noise performance

- Ripple performance

- Efficiency

ENPIR

## **Dual Die PwrSoC Approach**

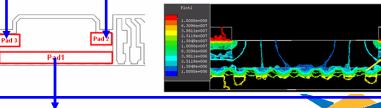

### (Design for Manufacturability Challenges)

- Discrete Inductor Size Compatibility With Semiconductor Packaging

- Molding compound

- Stress effects on magnetic characteristics

- o inductance & ac power loss

- Overhead coverage/clearance

- Sufficient volume to constrain internal reflow of solder joints

- MSL issues

- Balance

- Solder reflow

- MTBF

- Combine inductor reliability with silicon reliability

- Die to Substrate Connections

- Inductance effects on switching losses

- Layout

- Trade-off between efficiency & noise

- Thermal Dissipation

- Distribution of power losses

Minimize inductance of conduction path to reduce rise time

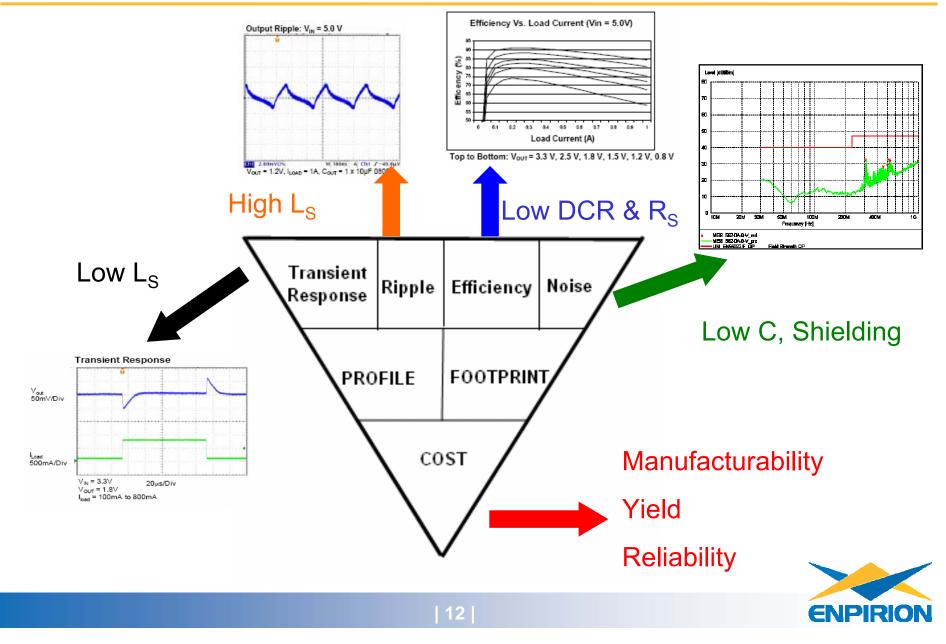

## Typical Inductor Design Criteria

(Physical Parameters of Commercially Available Inductors)

- Physical Size

- Profile dictated by application and market

- Footprint dictated by cost and application

- Terminations

- Location

- Effect on layout

- o Trade-off become flow of power current and clearance from wire bonds

- Metalization

- Choice of manufacturing i.e wire bond, smt, etc

- Au => wire bonding if flatness and hardness is met

- o Sn, SnAg or SnAgCu => smt

- Size

- Solder volume

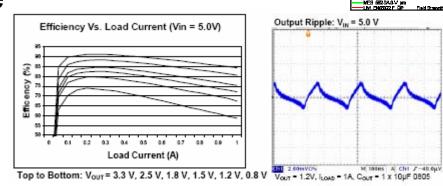

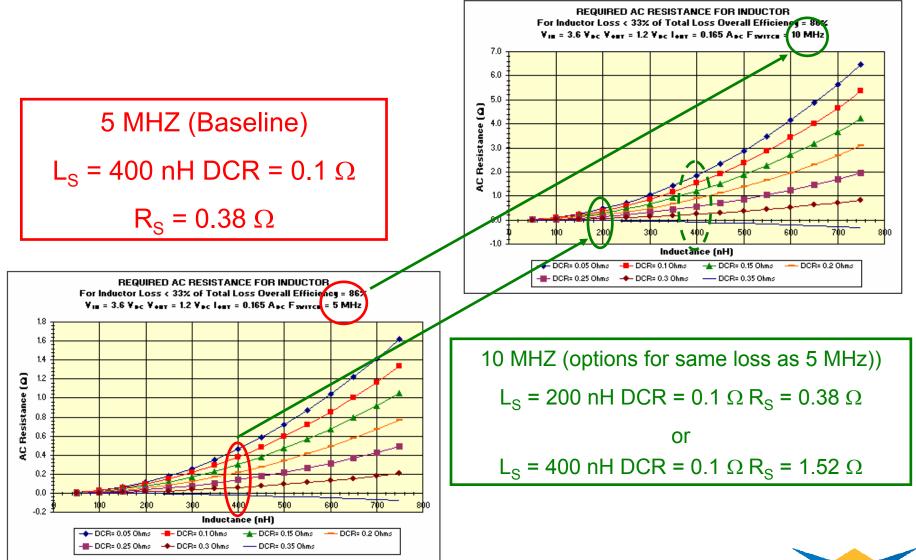

## **Dual Die to Single Die Solution**

(Transition Strategy)

- Address physical size of inductor consistent with wafer manufacturing process

- Revisit inductor design rules

- Inductance value required to meet ripple voltage

- Effect of power loss on distribution overall power loss budget

- Cost effective interconnect technology

## Inductor Sizing (Design Hierarchy)

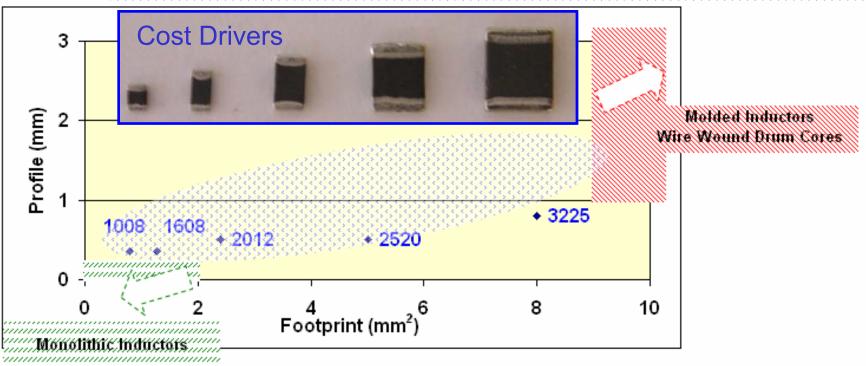

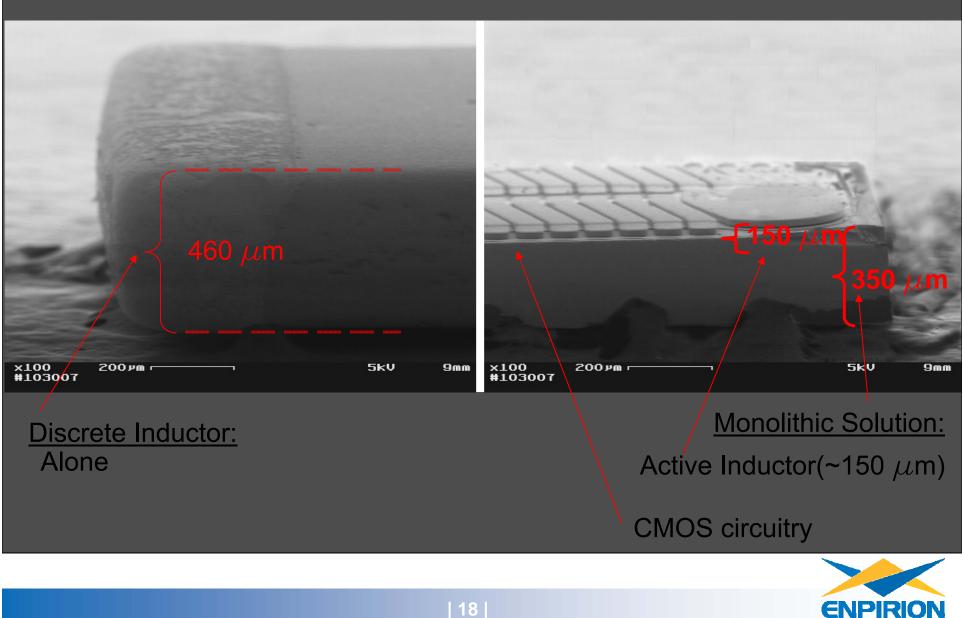

## **Inductor Size Progressions**

#### (Commercial Discrete Inductors Vs Monolithic Solution)

Multi layers inductors provide cost competitive solutions for applications that allow overall device height > 0.8 mm

Monolithic approach provide cost competitive solution for footprints  $< 2 \text{ mm}^2$ and a technical advantage for applications that require a device height < 0.6 mm

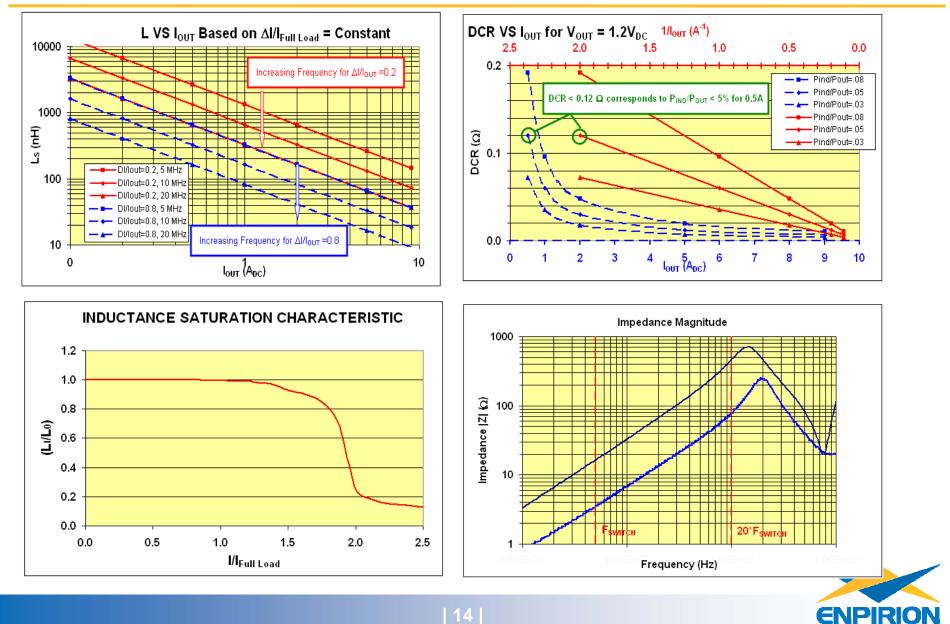

## **Traditional Inductor Design Criteria** (Electrical Parameters)

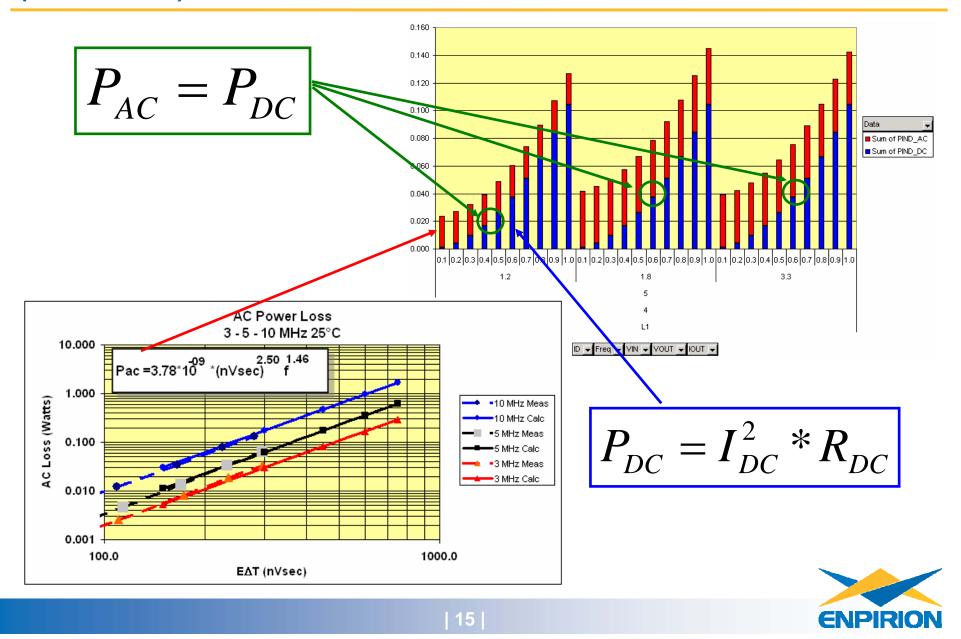

### Inductor Design Criteria (Power Loss)

## **Inductor Design Criteria**

(Surveying Small Signal Parameters to Fit Power Loss Budget)

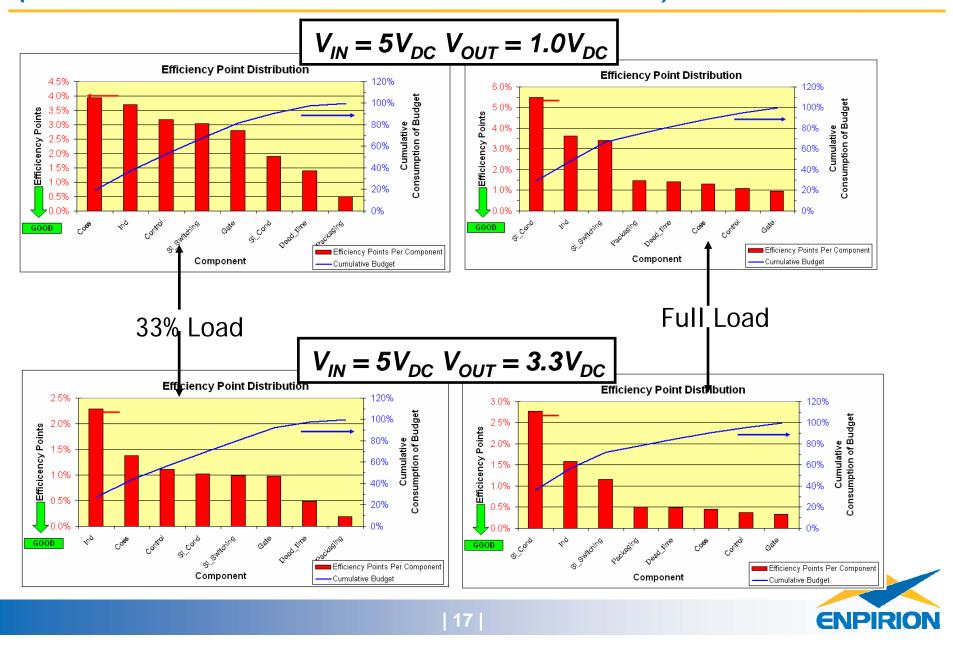

#### **Power Loss Distribution** (Pareto - 5V/1V Vs 5V/3.3V - 33% Load Vs Full Load)

## **Progression From Dual Die to Single Die Solution** (Advantage of Physical Profile)

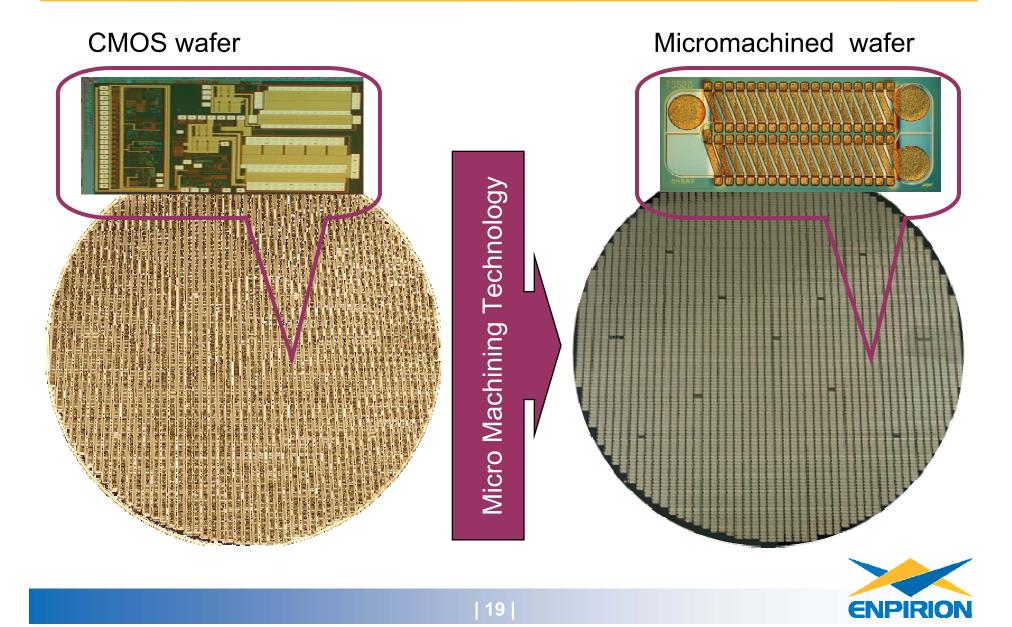

### **Progression From Dual Die to Single Die Solution** (Combination of Two Wafer Processing Technologies)

## **Progression From Dual Die to Single Die Solution** (Overview)

- Obstacles

- Costs

- Wafer size (150 mm -> 200 mm)

- o Increase die per wafer by increasing wafer size

- o Trade-off inductor function versus silicon function

- Wafer manufacturing yields

- Stress effects of copper & magnetic material

- o Wafer warp

- » Less material for less warp Vs more material for better performance

- o Technical performance

- » Effects on physical stress on magnetic properties

- Package assembly

- Assembly process effects on magnetic performance

- Interconnects between inductor and silicon functions

- Benefits

- Overall footprint approaches silicon die size for given profile

- Reduce cost, yield and reliability issues associated with mixed mode manufacturing (smt + wire bond)

- Lower inductance and resistances associated with interconnects

## Summary (PwrSoC)

- Dual Die Solutions Are Here Today And Serve To

- Set the pace towards higher switching frequencies

- Demonstrate market acceptance of PwrSoC

- Demonstrate manufacturability

- Establish a reliability track record for PwrSoC

- Address issues for inductor sizes to be compatible with wafer process

- adapt distribution of silicon, inductor and packaging losses

- adapt to established forward package assembly processes

- Establish capability limits of more conventional inductors

- Single Die (Monolithic) Solutions

- Will be required to meet the challenges of low profile

- <0.60 mm package height)</p>

- Address current applications that require

- LDO sizing and cost with switcher type efficiencies

Thank You for Your Attention (Any Questions?)