### Power Delivery for the Next Generation Mobile Platform

Tawfik Rahal-Arabi, Fellow IEEE

Jae-Hong Hahn, and Jorge Rogriguez

Mobile Platform Architecture Development

Email: Tawfik.r.Arabi@intel.com

Phone: (503) 456-0485

Acknowledgments: David Browning, Shekhar Borkar, Mike Graf, Jim Erikson, Bill McAuliffe

## **Agenda**

The Mobile Notebook Environment

Optimizing for Energy Efficiency

- Battery Life and Energy Star

The Mobile Notebook Power Delivery State of the Art

The Multi-Core Environment & Future Trends

Summary and Conclusions

## **Optimizing for Energy Efficiency**

Source: NPD, 2000

#### **Prices of Non-Energy Star vs. Energy Star Appliances**

| Category            | Average Price of<br>Non-Energy Star | Average Price<br>of<br>Energy Star | Energy Star<br>Price<br>Premium |

|---------------------|-------------------------------------|------------------------------------|---------------------------------|

| Dishwashers         | \$376                               | \$404                              | 7 %                             |

| Air Conditioners    | \$257                               | \$279                              | 9 %                             |

| Washing<br>Machines | \$379                               | \$869                              | 129 %                           |

| Refrigerators       | \$650                               | \$1,118                            | 72 %                            |

Energy Star appliances command premium prices. In spite premium, the study indicates consumers are shopping for energy efficiency."

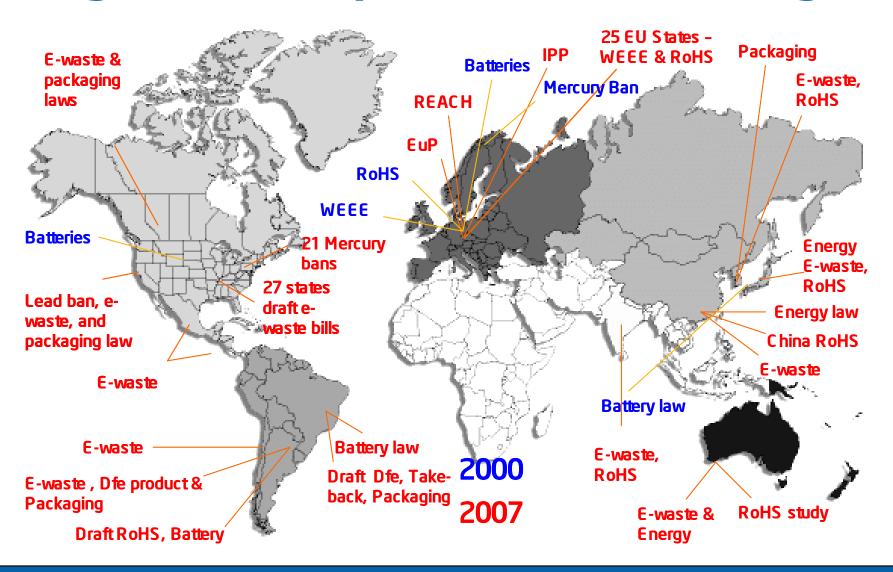

## Regulation explodes – EU leading

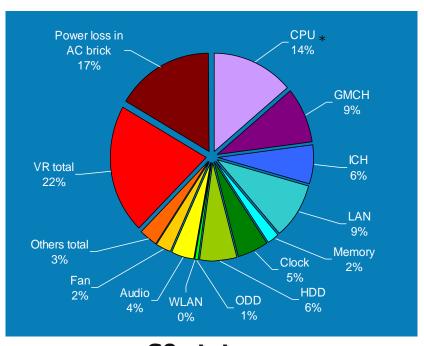

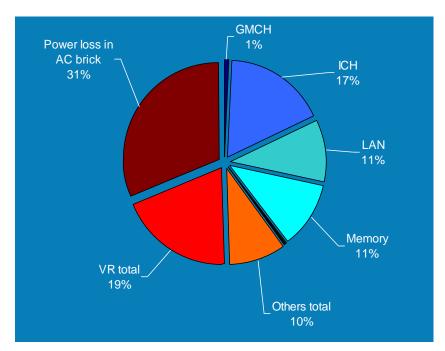

# Optimizing for Energy Efficiency: System Power Breakdown

S0 state

S3 state (WOL enabled)

High power loss in power delivery (AC brick + VRs)

<sup>\*:</sup> Varies depending on the power scheme in AC mode. The chart shows CPU power at C3. With C4/Deep C4 enabled, the CPU power decreases by ~50%.

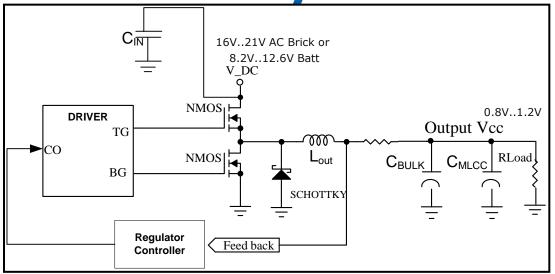

**Typical CPU Core VR Today**

- 2-3 phase

- fsw ~300kHz

- BW ~50kHz

- CBULK ~ 4x330uF

- CMLCC ~ 32x10uF

- Real estate ~625mm²

(bulk components only)

- BOM ~ \$6.5

- Efficiency at TDP ~ 86%

Single phase buck converter

| CPU TDP=35W, Vin=19V, VID=1.1125V, -2.1mOhm, 25C |                   |                |             |                |  |

|--------------------------------------------------|-------------------|----------------|-------------|----------------|--|

| OEM                                              | VR Power Loss (W) | Efficiency (%) | # of phases | FETs per phase |  |

| 1                                                | 5.43              | 86.56          | 3           | 2              |  |

| 2                                                | 5.56              | 86.27          | 3           | 2              |  |

| 3                                                | 5.52              | 86.38          | 2           | 4              |  |

| 4                                                | 5.518             | 84.28          | 2           | 3              |  |

Customers Maximize ROI given

Cost | Area | Efficiency | Performance Tradeoffs

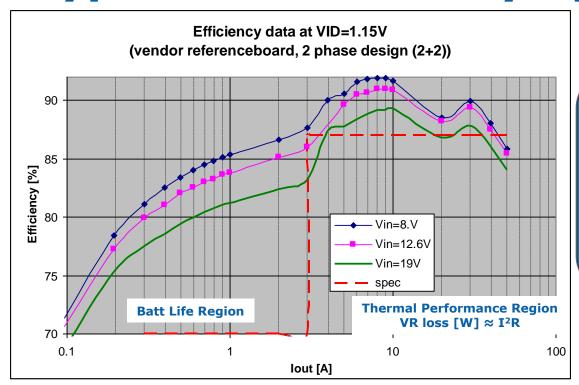

## **Typical VR Efficiency Specification**

## Efficiency optimized over full load range:

- •Full load all phases on

- •Mid load single phase on

- Light load DCM,PFM

| State       | Efficiency Target | ICC-CORE Level                                      |

|-------------|-------------------|-----------------------------------------------------|

| Sleep       | >70%              | $0.3 A \leq I_{\text{CC-CORE}} \leq 3 A$            |

| Sleep       | > 70%             | $3\text{A} \leq I_{\text{CC-CORE}} \leq 9\text{A}$  |

| Active Mode | > 87%             | $9\text{A} \leq I_{\text{CC-CORE}} \leq 18\text{A}$ |

| Active Mode | > 87%             | $9A \leq I_{\text{CC-CORE}} \leq TDC$               |

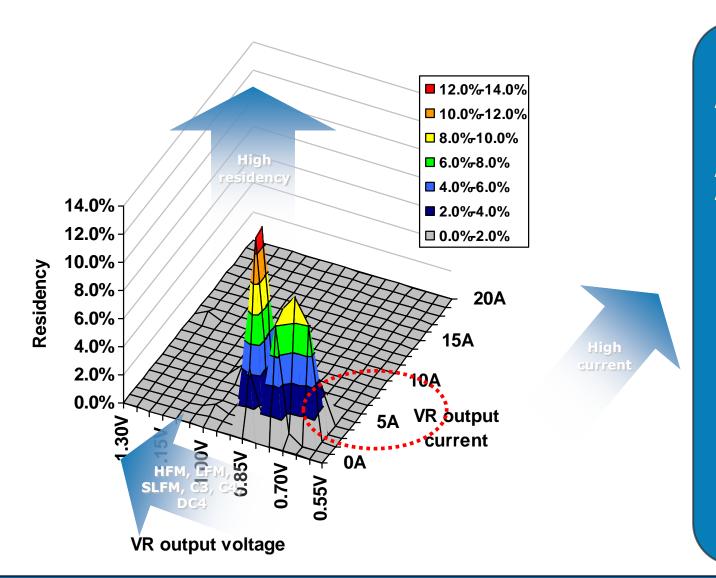

### **3D Histogram for IMVP Workload Analysis**

Very high residency at low power in typical laptop usage models (DVD playback, office productivity, Energy Star)

Optimize the VR efficiency for light workload

### **Mobile VR State of the Art**

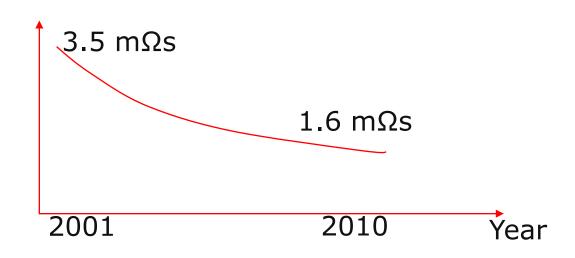

- 300KHz Switcher unlikely to get better Ouptut |Z| (Load Line) performance for next few years

- Limited by Cap technology and routing losses

- For lower Load Line, a new sweet spot of VR performance must be attained

## **Summary: VR State of the Art**

Load line from Regulator to CPU ~ 1.5 mOhms

- Nearly 75mV (7.5% frequency loss)

Single Rail, Single Stage 12-1V

Switching Frequency < 500kHz

High frequency caps needed to clamp MHz range noise below the load line

VR Efficiency ~ 87% @TDP, 70% at Low Current

- ~5W TDP loss for a mainstream mobile 35W CPU

- ~1W TDP loss on the board

### What is Desired

Multi-Core Computing Creates an Opportunity for a Multi-Rail Configurable VR

- Independent rail control can improve average power

- Independent rails without configurability hurts Enhanced Dynamic Acceleration Technology (EDAT)

- Therefore, there is a need for granularity & configurability

Shallower Load Line improves Performance and/or Thermal Design Power (TDP)

- What not ~ ZERO mOhms?

Efficiency improvements significantly help battery life, TDP, and/or performance;

- Need to improve efficiency @ TDP and low current to meet future Energy Star Requirements

Board space is premium, especially in small form factor segments

- Large voltage step conversion could reduce space but reduces Efficiency

- Alternatively, two stage step conversion may also provide space reduction

## **Summary**

Energy efficiency getting more prevalent for business and regulatory reasons

Power Delivery is aBig Factor in Improving Platform Efficiency

Significant gap between State of the Art and Desired Roadmap for power delivery

- Need non-linear improvements in VR technology

# THANK YOU